Устройство для возведения в квадрат

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (l9) (11) 4(5() С 06 F 7/552

ОПИСАНИЕ ИЗОБРЕТЕНИ

И АВТОРСКОМ У СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3594837/24-24 (22) 19.05.83 (46) 07.06.85. Бюл. й- 21 (72) Н.В.Черкасский, -В.M.Êðèùèøèí и Г.Ф.Криворучко (71) Львовский ордена Ленина политехнический институт им.Ленинского комсомола и Институт прикладных проблем механики и математики АН Украинской

ССР (53) 681.325 (088,8) (56) 1 Авторское свидетельство СССР

Ф 788106, кл, G 06 F 7/552, 1979.

2.Потапов В.И. и др. Быс.тродействующие арифметико-логические устройства цифровых вычислительных машин.

Новосибирск, изд-во НИСИ, 1978, с. 1-19, рис. 1,4.1 (прототип). (54) (57) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ

В КВ ЯРАТ, содержащее входной и выходной регистры, два блока памяти и сумматор, причем выходы К старших разрядов входного регистра подключены к входам первого блока памяти, выходы (; старших разрядов входного регистра подключены к первой группе входов второго . блока памяти (P (К ), выходы первого блока памяти подключены к первой группе входов сумматора, выходы которого соединены с входами выходного регистра, о т л и ч аю щ е е с я тем, что, с целью сокращения аппаратурных затрат, вторая группа входов второго блока памяти соединена с выходами (p — К ) младших разрядов входного регистра, выходы второго блока памяти соединены с второй группой входов сумматора (П— разрядность аргумента) . t 160402

Изобретение относится к вычислительной технике и предназначено для использования в универсальных и специализированных ЦВМ.

Известно устройство для возведения в квадрат, содержащее сумматор, блок памяти и умножитель (1 .

Недостатками устройства являются его сложность и невозможность контроля, связанная с усечением резуль- 10 тата вычислений.

Наиболее близким техническим решением к изобретению является устройство для возведения в квадрат, содержащее два регистра, блок памяти, 15 коммутатор, дешифратор, с-.умматор, входы первого слагаемого которого соединены с первой группой выходов блока памяти, вторая- группа выходов которого соединена с информационны- 20 ми входами коммутатор, управляющие входы которого соединены с выходами дешифратора, выходы которого соединены с разрядными выходами первого регистра, разрядные выходы второго ре- 25 гистра соединены с адресными входами блока памяти, выходы коммутатора соединены с входами второго слагаемого сумматора (2) .

Недостатком известного устройства ЗО являются относительно большие аппаратные затраты, необходимые для его реализации.

Цель изобретения — сокращение аппаратурных затрат.

Поставленная цель достигается тем, что в устройстве для возведения в кв"драт, содержащем входной и выходной регистры, два блока памяти и сумматор, причем выходы К старших разрядов входного регистра подключены к входам первого блока памяти, выходы 1 старших разрядов входного регистра подключены к первой группе входов второго блока памяти (F (K ), 45 выходы первого блока памяти подключены к первой группе входов сумматора, выходы которого соединены с входами выходного регистра, вторая группа входов второго блока памяти соединена с выходами (4-К) младших разрядов входного регистра, выходы второго блока памяти соединены с второй группой входов сумматора (П вЂ” разрядность аргумента) .

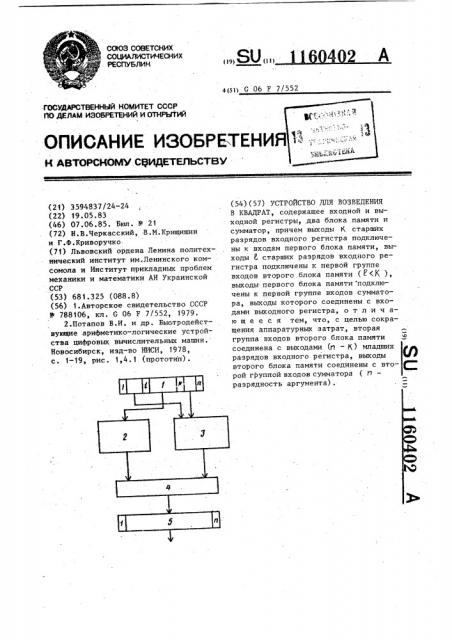

На чертеже представлена блок-схема устройства.

Устройство содержит входной регистр 1, два блока 2 и 3 памяти, сумматор 4 и выходной регистр 5.

Диапазон изменения аргумента (О, 1) к разбивается на 2 подынтервалов.

Внутри каждого L -го подынтер вала значение функции 9 (x) = Х определяется следующим образом

9(x) - g (x .l * ц (x) = M (x) де.Ò (x;) = "1 2 (x x„) — значение

1 -К функции ц (x)=r в начальной точке f -Го подынтервала с поправкой для сбалансированной погрешности;

Х вЂ .начальная точка подынтервала, включающего в себя среднюю точку j -го интервала; — значение корректирующей функции и Х-X-X .

Ц (ЬХ) 9 (йХ) = (Х .п+2 ) -Х п= 2Х и 2 +2 к-Г

Каяу(ыи интервал включает 2 подинтервалов, и ошибка приближения максимальна на концах интервала. Точное

Корректирующая Функция у (йХ) являW-Г

J. ется общей для 2 подынтервалов, объединенных в ) -й интервал, и определяется в виде

Ц (дк) = У(Х „+ ЬХ) — Х п

Всего на интервале (О 1) определяР

1 ется 2 корректирующих функций и (ЬХ>, = 1,2

Определим величину p v К при погрешности приближения/ F 1 2 . Длина и подынтервала равна 2 . Тогда максимальное значение корректирующей функции б0602

Для 15-разрядных входных чисел

15,К=10,Г=4.

Общая ошибка вычисления функции

9 (Х) = Х предлагаемым устройством рав10 на с=сл+ о

Ф

15 где п — погрешность приближения; о — погрешность округления.

В данном случае

Таким образом

/E/<1, 5 ° 2

К-Г -1 -К

Х„л-Х;= 2 2 получим с .ъ К-Р-1 -2К -К-Р-1 си= 2 =2

При

Для запоминания значений корректирующих функций используется блок 3 40 памяти (ПЗУ) объемом

Г и-К +п-.К Ц2= 2 2 ° rn =2 - л.1,,, Разрядность rn регистра 5 определяется мах / у fh X )/

-45 ,) л1пх / g (Ь Х)! < 2, m = n- к+1

Г+и к

Q2 = 2 (П - К 1)9л.

Составитель А.Казанский

Техред А.Бабинец

Корректор В.Бутяга

Редактор О.Юрковецкая

Заказ 3779/46 Тираж 710

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Подписное

Филиал ППП "Патент", г.Ужгород, ул.Проектная,4 з 11 значение функции g (х)= х в крайней правой точке -го интервала равно (Хл 2 2 +2 ) K-P-1 -к. 2 (>jn+2 ° 2 ) + 2Х 2 +2 2" " 1. " . 2к

2 + 2

Определим приближенное значение ч

Ч(Х) в этой точке . Ц(Х„) =(Х л+2 2 ) -2 (Х л -Х;) — К -2К

Ц,< Х) г х,„ 2

E-==(õjë.2 2 ) — х,л+2 - .2 )+

КГ1 -K 2 К

+ 2 (Хрл-Х;) Я .Х „4 К,2 2

Учитывая, что для Х; — крайней правой узловой точки -го интервала

-и

ЛЯ I 2" г и

Для запоминания значений У (Х )

1 используется " блок памяти (ПЗУ) объемом

Оптимальное значение параметров К и Ф можно определить из условия минимизации суммы

Q =Q1+Q2

При изготовлении. устройства значения функции у (Xq} и корректирующих функций у (йХ), j =1,2 записываются в блоки 2 и 3 памяти. Предварительно значения этих функций рассчитываются на ЭВМ.

Устройство работает следующим образом.

В первом такте входное число поступает в регистр 1. После этого K старших разрядов входного числа поступают на вход блока 2 памяти в качестве адреса, по которому выбирается число, являющееся значением л функции У (Х;) в соответствующей узловой точке. (старших и И вЂ” к младших разрядов входного числа по,ступают на вход блока 3 памяти в качестве адреса, по которому выбирается число, являющееся значением соответствующей корректирукицей функции.

Х

Во втором такте искомое значение

Х записывается в выходной регистр

5, а в регистр 1 записывается второе число

Таким образом, устройство не содержит коммутатора и дешифратора.