Устройство приоритета

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ПРИОРИТЕТА, содержащее узлы анализа по числу источников запросов, а в каждом узле анализа группу элементов И и регистр, отличающееся тем, что, с целью повышения быстродействия оно содержит группу элементов И-НЕ, а в каждом узле анализа две группы элеыентов И-НЕ,. причем первый вход первого элемента И-НЕ первой группы и первый вход первого элемента И группы в каждом узле анализа соединены с соответствующим запросным входом устройства, первый вход каждого L -го элемента И-НЕ первой группы и первый вход -го элемента И группы в каждом узле анализа

COlO3 СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„11 0412 А

4(5() G 06 Г 9/46 т -"

»

)i *«

»»» ч

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H ABT0PGHOMV СВИДЕТЕЛЬСТВУ

ЬР

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3610859. 24-24 (22) 24.06.83 (46) 07. 06. 85. Бюл. 9 21 (72) Н. A. Волобуев, Б. А. Солдатов, A.M.Попов, H.Ã.3óåâ и Л.В.Никишина (53) 684.325 (088.8) (56) 1»Каган Б.M. Электронные вычисли11 тельные машины и системы. M., Энергия", 1979, с. 298, рис. 8-17.

2.Авторское свидетельство СССР

В 1037253, кл. С 06 F 9/46, 1983 (прототип). (54)(57) УСТРОЙСТВО ПРИОРИТЕТА, содержащее узлы анализа по числу источников запросов, а в каждом узле анализа группу элементов И и регистр, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит группу элементов И-НЕ, а в каждом узле анализа две группы элементов И-НЕ,. причем первый вход первого элемента И-НЕ первой группы и первый вход первого элемента И .группы в каждом узле анализа соединены с соответствующим запросным входом устройства, первый вход каждого с -ro элемента И-НЕ первой группы и первый вход i --го элемента И группы в каждом узле анализа (j =2..., n, r) число запросов) соединены с выходом (< -1)-го элемента И группы своего узла анализа, второй вход каждого элемента И-НЕ первой группы в каждом узле анализа соединен с прямым выходом одноименного разряда регистра своего узла анализа, первый вход каждого элемента И-НЕ второй группы каждого узла анализа соединен с выходом одноименного элемента И-HE группы, второй вход каждого элемента

И-НЕ второй группы в каждом узле анализа соединен с инверсным выходом одноименного разряда регистра своего узла анализа, второй вход каждого элемента И группы в каждом узле анализа соединен с выходом одноименного %ФУ элемента И-НЕ второй группы своего С узла анализа, выходы < -х элементов

И-НЕ первой группы каждого узла анализа соединены с соответствующими входами -го элемента И-НЕ группы

Э выходы последних элементов И группы в каждом узле анализа являются выходами расширения устройства, выходы © элементов И-HF. группы являются груп- мР пой выходов устройства.

1160412

Изобретение относится к вычислительной технике, а именно к организации систем прерывания программ, и может быть использовано при построении схем наивысшего приоритета. 5

Известна схема однотактпого определения запроса наивысшего приоритета, содержащая элементы ИЛИ, НЕ, И и шифратор (1$ .

Недостатком этого устройства явля-10 ется невысокое быстродействие.

Наиболее близким по технической сущности и достигаемому результату к изобретению является многnKBHaffbное устройство приоритета, содержашее1 каналы, а в каждом каналс. элемент И, элемент HF, элемент ИЛИ-НЕ, элемент

ИЛИ и триггер I2J .

Недостатком известного устройства является низкое быстродействие.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство приоритета, содержащее узлы анализа по числу пы в каждом узле анализа соединены с соответствующим запросным входом устройства, первый вход каждого < -го35 элемента И вЂ” НЕ первой группы и первый вход т -го элемента И группы в каждом -;зле анализа (1 =2,..., q, число запросов) соединены с выходом (4 — 1)-го элемента И группы своего узла анализа, второй вход каждого элемента И-НЕ первой группы в каждом узле анализа соединен с прямым выходом одноимeffffof-n pasp va регистра своего узла аналт за, первьй вход каждого элемента И вЂ” НЕ втор ли группы

45 каждого уз.-IR анализа соединен с Bf>f— ходом одноименного элемента И-HF, группы, второй вход каждого элемента

И-HI. вто рлй группы в каждом узле ана-5О лиза сле;цтнен с инверсным выходом одHnlfMeêffoão разряда регистра своего узла анализа, второй вход каждого злемента И группы в каждом узле анализа соединен с выходом одноименного э.гтегмента И-1{Е второй группы своего узла анализа, выходы 1 -х элементов

И-НЕ lfервлй группы каждого уз IR анаисточников запросов, а в каждом узле анализа группу элементов И и регистр, введены группа элементов И-НЕ, а в каждый узел анализа две группы элементов И-НЕ, причем первыи вход перЗО вого элемента И-HF. первой группы и первый вход первого элемента И груплиз а с сед!тне ны с с Оот ветс т В ух)щтfми входами т -го элемента И вЂ” НЕ группы, выходы последних элементов И группы в каждом узле анализа являются выходами расширения стройства, выходы элементов И-НЕ группы являются группой выходов устройства.

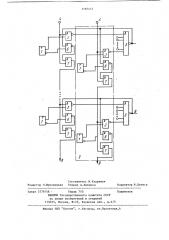

На чертеже приведена структурная схема предлагаемого ус.тройства. устройство содержит регистры 1, узлы 2 анализа, элементы И-HF. 3 группы, запросные входы 4, элементы

И-НЕ 5 группы, элементы И-НЕ 6 группы, элементы И 7 группы, группу выходов 8, выходы 9 расширения.

Устройство работает следующим образом.

Триггеры регистров 1 хранят заданный двоичный код прерывания. При поступлении сигналов запросов на входы 4 старшие разряды регистров кода через первый элемент И-HF 3 (для удобства рассмотрим первый уровень первого разряда) поступают на соответствующие входы элемента И-HE

5, на выходе которого формируется сигнал "1" или "0". Сигнал прерывания с выхода второго элемента И-НЕ

5 поступает на один из входов третьего элемента И-НЕ 6, на второй вход которого поступает инверсный сигнал с выхода соответствующего разряда регистра 1. Элемент И-HF. 6 сравнивает выходной разряд устройства со значением кода соответствующего разряда регистра прерывания. При наличии в в и

cèãíàëå запроса 1, а в соответствующем разряде регистра — "0, на выходе третьего элемента И-HF. 6 формируется сигнал блокировки всех других младших разрядов запроса данного уровня прерывания. Этот сигнал с выхода третьего элемента И-HF. 6 поступает на вход элемента И 7, где он объединяется с сигналом блокировки из предыдущего разряда (кроме старшего разряда), а в старшем разряде объединяется с сигналом (отсутствием сигнала) на входе 4 устройства. Отсутствие сигнала блокировки во всех разрядах соответствующего уровня прерывания означает, что данный уровень является старшим по приоритету и его код формируется на выходах 8 устройства.

Применение изобретения позволяет повысить быстродействие устройства.

1160412

Составитель N. Кудряшев

Редактор О.Юрковецкая Техред А.Бабинец

Корректор В. Бутяга

Подписное

Филиал ППП "Патент", г.ужгород, ул.Проектная,4

Заказ 3779/46 ° Тираж 710

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5