Множительное устройство

Иллюстрации

Показать всеРеферат

МНОЖИТЕЛЬНОЕ УСТРОЙСТВО, содержащее блок выделения модуля и знаковьй компаратор, входы которых объединены и явл яются первым информационным входом устройства, аналогоцифровой и цифроаналоговый преобра .зователи, дискретно-аналоговый и аналоговый блоки умножения, блок .вычитания, первый инвертор, первьй коммутатор и сумматор, два входа которого подключены к выходам соответственно дискрегтно-аналртового, и аналогового блоков умножения, а выход является выходом устройства, выход знакового компаратора соединен с управляющим входом первого коммутатора , два информационных входа которого подключены соответственно к входу и выходу первого инвертора, дискретный вход дискретно-аналогового блока умножения подсоединен к выходу аналого-цифрового и входу цифроаналогового преобразователей, вход аналого-цифрового преобразователя подключен к выходу блока выделения модуля, один из входов аналогового, блока умножения подсоединен к выходу блока вычитания, отличающееся тем, что, с целью повьпиения точности, .оно содержит второй инвертор и второй коммутатор, управляющий вход которого соединен с выходом знакового компаратора, а два инфор (Л мационных входа и выход подключены с соответственно к входу и выходу второго инвертора и к вычитающему входу блока вычитание, подсоединенного суммирукщим входом к первому информационному входу устройства, вход второго инвертора подключен к выходу цифроаналогового Преобразователя, о: второй вход аналогового блока умноо жения соединен с входом первого ин4: 4 вертора и вторым информационным входом устройства, выход первого коммуto татора подключен к аналоговому входу дискретно аналогового блока умножения..

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

4(51) С 06 С 7 16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3688509/24-24 (22) 04.01.84 (46).07.06.85. Бюл. У 21 (72) lo.Í. Бобков, И.P. Соболевский и А.А. Третилов (71). Львовский ордена Ленина политехнический институт им. Ленинского комсомола (53) 681.3(088.8) (56) 1. Кори Г. Кори Т. Электронные аналоговые и аналого-цифровые вычислительные машины. И., "Мир", 1968, ч. 1, с. 395.

2. Патент Японии У 55-47421, кл. С 06 G 7/161, опублик. 1980 (прототип). (54)(57) МНОЖИТЕЛЬНОЕ УСТРОЙСТВО, содержащее блок выделения. модуля H знаковый компаратор, входы которых объединены и являются первым информационным входом устройства, аналогоцифровой и цифроаналоговый преобра.зователи, дискретно-аналоговый и аналоговый блоки умножения, блок .вычитания, первый инвертор, первый коммутатор и сумматор, два входа которого подключены к выходам соответственно дискретно-аналогового.и аналогового блоков умножения, а выход является выходом устройства, выход знакового компаратора соединен с управляющим входом первого коммута„„SU„„1160442 А тора, два информационных входа которого подключены соответственно к входу и выходу первого инвертора, дискретный вход дискретно-аналогового блока умножения подсоединен к выходу аналого-цифрового и входу цифроаналогового преобразователей, вход аналого-цифрового преобразователя подключен к выходу блока выделения модуля, один из входов аналогового. блока умножения подсоединен к выходу блока вычитания, о т л и ч а ю щ ее с я тем, что, с целью повышения точности, .оно содержит второй инвертор и второй коммутатор, управляющий вход которого соединен с выходом знакового компяратора, а два информационных входа и выход подключены соответственно к входу и выходу второго. инвертора:и к вычитающему входу блока вычитания, подсоединенного суммирующим входом к первому.информационному входу устройства вход втоУ

I®eeL рого инвертора .подключен к выходу цифроаналогового преобразователя, Май второй вход аналогового блока умно- © 1 жения соединен с входом первого инвертора и вторым информационным вхо- э4 ь дом устройства, выход первого комму- 4ай татора подключен к аналоговому входу

I дискретно-аналогового блока умножения.

1 1160

Изобретение относится к аналоговой вычислительной технике и может быть использовано в системах и устройствах автоматики.

; Известно множительное устройство с аналого-цифроаналоговым преобразо5 вателем, содержащее аналого-цифровой (АЦП) и цифроаналоговый (IIAII) преобразователи, дискретно-аналоговый и аналоговый перемножители, схему. вычи!

О тания и. сумматор Pl ).

Однако это устройство (если АЦП и

ЦАП вЂ” однополярные, а дискретно-аналоговый блок умножения соответственно двухквадратный) способно осуществлять

15 операцию перемножения лишь в двух квадрантах. Расширение области работы устройства до четырех квадрантов путем применения биполярных АЦП и ЦАП и четырехквадрантного дискретно-аналогового перемножителя существенно

20 увеличивает объем устройства.

Наиболее близким по технической сущности к изобретению является множительное устройство, в котором

25 используется множительное устройство (1J в качестве двухквадрантного. Такое устройство содержит блок выделения модуля, знаковый компаратор, аналого-цифровой и цифроаналоговый. преобразователи, дискретно-аналоговый и аналоговый блоки умножения, блок вычитания, сумматор, инвертор и коммутатор, причем входы блока выделения модуля и знакового компаратора соединены с первым входом устройства,35 выход знакового компаратора соединен с управляющим входом коммутатора, первый и второй входы которого соединены соответственно с входом и выходом инвертора, выход блока выделения мо- @» дуля соединен с входом аналого-цифрового преобразователя, выход которого соединен с входом цифроаналогового преобразователя и дискретным входом дискретно-аналогового перемножителя, выход последнего подключен к одному из входов сумматора, второй вход сумматора соединен с выходом аналоговбго блока умножения, первый вход которого соединен с выходом блока вычитания (2 ).

Однако в известном устройстве точность блока выделения модуля в цепи одного из перемножаемых сигналов влияет на точность работы устрой- 5 ства в целом.

Цель изобретения - повышение точмости устройства..

442 2

Поставленная цель достигается тем, что множительное устройство, содержащее блок выделения модуля и знаковый компаратор, входы которых объединены и являются первым информа»ционным входом устройства, аналогоцифровой и цифроаналоговый преобразователи, дискретно-аналоговый и аналоговый блоки умножения, блок вычитания, первый инвертор, первый коммутатор и сумматор, два входа которого подключены к выходам соответственно дискретно-аналогового и аналогового блоков умножения, а выход является выходом устройства, выход знакового компаратора соединен с управляющим входом первого коммутатора, два информацион ных входа которого подключены соотI ветственно к входу и выходу первого инвертора, дискретный вход дискретноаналогового блока умножения подсоединен к выходу, аналого-цифрового и входу цифроаналогового преобразователей, вход аналого-цифрового преобразователя подключен к выходу блока выделения модуля, один иэ входов аналогового блока умножения подсоединен к выходу блока вычитания, дополнительно содержит второй инвертор и второй коммутатор, управляющий вход которого соединен с выходом знакового компаратора, а два информационных входа и вьгход подключены соответствен;.о к входу и выходу второго инвертора и к вычитающему входу блока вычитания, подсоединенного суммирующим входом к первому информационному входу устройства, вход второго инвертора подключен к выходу цифроаналогового преобразователя, второй вход аналогового блока умножения соединен с входом первого инвертора H вторь»м информационным входом устройства, выход первого коммутатора подключен к аналоговому входу дискретно-аналогового блока умножения.

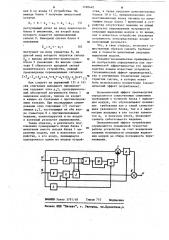

На чертеже представлена структурная схема множительного устройства.

Устройство содержит блок 1 выделения модуля, знаковый компаратор 2, аналого-цифровой преобразователь (АЦП) 3, цифроаналоговый преобразователь (ЦАП) 4, дискретно-аналоговый и аналоговый, блоки умножения соответственно 5 и б, блок 7 вычитания, сумматор 8, первый 9 и второй 10 инверторы, первый 11 и второй 12 коммутаторы, первый 13 и второй 14 информационные входы и выход 15 уст(3) где - абсолютная погрешность на х

40 выходе блока выделения модуляе

3 1160442 4 ройства. Входы блока 1 выделения Код Y„ поступает на дискретный модуля, знакового компаратора 2 и вход дискретно-аналогового блока 5 суммирующий вход блока 7 вычитания Умножения, на аналоговый вход котообъединены и образуют вход 13 устрой- рого подается сигнал с вьмода перства, выход блока 1 вьделения модуля вого коммутатора 11, который, в . соединен со входом АЦП 3, à выход свою очередь, образуется из второго последнего — со входом ЦАП 4 и диск- перемножаемого сигнала Y путем иэмеретным входом дискретно-аналогового нения его полярности в соответствии блока 5 умножения. Выход ЦАП 4 под- с полярностью сигнала X. Сигнал Y ключен через инвертор 10 к одному из 19 поступает на один нэ входов коммутавходов и непосредственно — к второму тора 11 непосредственно, а на другой входу коммутатора 12, управляющий его вход — через инвертор 9. Коммувход которого соединен с аналогичным татор 11 подключает к аналоговому входом коммутатора 11 и выходом зна.- входу дискретно-аналогового блока 5 кового компаратора 2, а выход — с вы- 1у умножения сигнал У со входа 14 устчитающим входом блока 7 вычитания, ройства при наличии сигнала логичесвыход .последнего подключен к одному кой единицы на его управляющем входе, иэ входов аналогового блока 6 умно- . и инвертированное значение сигнала— жения, выход которого подключен к У, получаемое на выходе инвертора 9, одному .из входов сумматора .8, второй 2О если на управляющем входе блока 11

Ъ вход которого соединен с выходом имеется сигнал логического нуля. дискретно-аналогового блока 5 умно- Таким образом, коммутатор 11 и инжения. Входы ннвертора 9, коммутато- вертор 9 совместно со знаковым комра 11 и второй вход аналогового бло- паратором 2 осуществляют перемноже-. ка 6 умножения объединены и образуют д ние сигнала Y на знак сигнала Х. вход 14 устройства, выход. коммутато- Дискретно-аналоговый блок 5 умножера 11 соединен с аналоговым входом - ния перемножает сигнал Y на квантодискретно-аналогового блока умноже- ванное значение модуля сигнала X ния, выход сумматора 8 является вы- Z К,К„ =К,К, IXl/+ „ЧI. ходом 15 устройства.

30 При выполнении условия К,,К = 1 устройство работает следующим получим

3 образом.

Перемножаемый сигнал со входа 13 устройства поступает на вход блока 1 где У вЂ” произведение. сигнала Y на выделения модуля. Сигнал на выходе последнего д знак сигнала Х, К - масштабный коэффициент дйскретно-аналогового блока

Х„= Х1 4„, (1}

Код N„ïoñòóïàåò также на вход

ЦАП 4, при помощи которого преобразуется в аналоговую форму х =к й„ =@3K,(lxl ++h )

При К К = 1 получим

Одновременно сигнал Х поступает на вход знакового компаратора 2, Х„= lx la+ Ьх ) (4) на выходе которого при Х 0 обра0 4$ где К вЂ” масштабный коэффициент ЦАП 4. зуется сигнал логической единицы, а при Х C 0 — сигнал логического ну- . Сигнал Х поступает непосредстля. венно на один.из входов коммутатора

Сигнал Х, с выхода блока 1 по- 12, и через инвертор 10 — на другой ступает далее на вход АЦП 3, на вы- его вход. Коммутатор 12 подключает ходе которого образуется код к вычитающему входу блока 7 вычитания сигналы 1Х, +д„или -l X l -dz х 1 з(Х ld х) таким образом, что знаки сигналов Х

Э и j X 1 +6„всегда совпадают. Следогде t X 1 " квантованное IIO уровню вательно, на вычитающем входе блока значение величины (Xl> 7 имеется сигнал Х, +6„с восстановК вЂ” коэффициент преобраэова- ленной полярностью. На суммирующий э ния АЦП 3. вход блока 7 вычитания поступает сиг1160442

ВНИИЙИ Заказ 3781/48 Тираж 710 Подписное

Филиал НПП Патеит", г. Ужгород, ул.Проектная,4

3 нал Х со входа 13 устройства. На выходе блока 7 получаем аналоговый остаток х, = х.— х -4, х,-л„, (5) поступающий далее на вход аналогового блока 6 умножения, на второй вход которого подается перемножаемый сигнал Y. Выходной сигнал блока 6 умножения 10

2о= X î, поступает на вход сумматора 8, на другой вход которого подается сигнал ..Z с выхода дискретно-аналогового 1 о блока 5 умножения. На выходе сумматора 8 образуется выходной сигнал множительного устройства, равный произведению перемножаемых сигналов = И о="д х ++X Ч-Ь„Ч= 5„ )МУ (Как следует иэ выражений (3) и (6) оба слагаемых выходного произведения содержат член d „Y, пропорциональный абсолютной погрешности блока 1 2 выделения модуля, причем он входит в каждое из слагаемых с противоположными знаками. При последующем суммировании этих слагаемых (7) составляющая а „Y, поступающая на оба входа сумматора 8 с противоположными знаками, компенсируется и. не входит в конечный результат перемножения.

Таким образом, в результате подключения суммирующего входа блока 7 Э5 вычитания вместо выхода блока 1 выделения модуля, как в известном устройстве, к его входу, являющемуся одновременно одним иэ входов устройства, а также введения дополнительных блоков 10 и 12, предназначенных для восстановления знака сигнала на вычитающем входе блока 7 вычитания в устройстве отсутствует влияние на общий результат перемножения погрешности операции выделения модуля в то время, как в известном устройстве указанная погрешность непосредственно входит в получаемый результат.

Это, в свою очередь, позволяет существенным образом снизить требования к точности выполнения операции выделения модуля.

Технико-экономические преимущества изобретения определяются как экономической эффективностью его производства взамен известных устройств (экономический эффект производства), так и улучшением технических характеристик систем, в которых может быть использовано изобретение (экономический эффект потребления).

Экономический эффект производства определяется существенным снижением требований к точности блока 1 выделения модуля, что обусловливает понижение требования как к самой схемотехнике укаэанного блока, так и к параметрам входящих в его состав элементов и, в конечном итоге, позволяет снизить себестоимость иэделия.

Экономический эффект потребления определяется повышенной точностью работы устройства эа счет исключения влияния погрешности операции выделения модуля на общую погрешность перемножения.