Регенератор цифрового сигнала

Иллюстрации

Показать всеРеферат

РЕГЕНЕРАТОР ЦИФРОВОГО СИГНАЛА. содерокаши усилитель-корректор , вход каюрого соединеи с входом регенератора , с цепью.автоматической pery;tH; ровки усиления в обратиой связи, последовательно содинеиные первый аналоговый ключ, формирователь порога и усреднитель порога, выход которого подкл.ючен к второму входу цепи автоматической регулировки усиления, элемент совпадгния. причем первый его вход и сигнальный пхол первого аналогового колюча соелмнены с выходом усилнтеля-корректор.1. и формирователь выходногосигнала, вход которого fof-. дииен с выходом элемента сонмадония и управляющим входом первого аналогового ключа, в выхоа - с вы)одом регенератора. а также блок тактовой 1:нм(

СО>ОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕС< >УБЛИН

%<51) П <>3 V,, )<(>0

К АВТОРСКОМ .Ф СВИДЕТЕЛЬСТВУ а также блок тактовой сннхр<>ни.1,11>ии. с<н тоящнн H 1 BT<)por<> н Пи Tht l t) нн,>л<)<()»ых ключей, лнух ячеек пнчити, нычитнющг< блока. интегратора, ) <)p;>»лне«<)I<) lt H< р.l тора, нключнкппег» н себ» шн:и л<>»»гель» соединенные <енернтор. )»р;>нлн< мый и.< пряженнем, и ныхолпой инск.lë и формир<>

Ватели K<)p<)T>«)< О IIM <>) !Ь< и. <>pHL < х<> l каждого н>>нлогоного клк>ч« lt рез нч< йл) памяти прис<>елинен к»è÷»ò»><»t«ìó блок>, выход которого через интегрнгор соелнн<» с управляемым геиернтороч. нричой ныхол которого соединен с упрннлякпцим вхолоч второго аналогового ключа и через формн рователь короткого импульса с вторым нх< дом элечента совпадения, а инверсный с управляющим входом третьего нна)<>«). ного ключа. огличающи<<сч теч, что. с. tlt лью повышения помехоустойчнности, н блок тактовой <)

HH);>t фазоврнщателн. причем»i<>л нннергнр> к)

ШЕ ГО ) С H 1H T« : H - <) l () Н и и Ч и 1 < . <« < Ч,<>р;<..>»ых«л усилителн ег>ч черн< ).>ем»»1 l,llljlrтн соедин(н с сигнальными í<<>.<нчи » ><>p<)l<) н тр<ть«о»l<.<л<п оных к.>л> н й, кннлр<<т)р

IA ныхол трнперногс> ф !.1<)»р»1>>»><ли пол ключеtl к унрннляк)шеч) нх<)л) t)t ме»Рз lн прет»

ГОСУДДРСТВЕННЫЙ НОМИТЕ Т СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРНТН4 (21) 3634236/24-2l (22) 09.08.83 (46) 07.06.85. Бюл. № 2l (72) И. Е. Байдан, Б. В. Карпухин и П.,С. Терещенко (7l) Одесский электротехнический институт связй им. А. С. Попова (53) 621.374 (088.8) (56) Гуревич В. Э. Лопушиин Ю. Г., Ра. бинович Г. В., Импульсно-кодовая модуляция в многоканальной телефонной связи. кСвязьн, l973, рис. 7.6а, с. >89.

Там же, рис. 7.9. с. 203.

Авторское свидетельство СССР Й 993449, кл. Н 03 500, l981. (54) (57) РЕГЕНИРАТОР ЦИФРО>)ОГО

СИГНАЛА. содержащи(усилитель-корректор, вход которого соединен с входом регеиератора, с цепью. автоматической регулировки усиления в обратной связи, последов вательно содиненные первый аналоговый ключ, формирователь порога н усреднитель порога, выход которого полключеи к вто. рому входу пепи автоматической регулировки усиления. элемент сонпаления. причем первый его ахоп и сигннльный нхол Нсрвого аналогового ключа соединены с выходом усилителя-корректора. и формировн. тель выхолного сигнал», нхол которого сое-. динен с выходом элемента со»явления и управляющим нхолом первого аналогового ключа, а выход — с ны)солом регенернтора.

U„„11 0547

11<>»)5>47

2 пения нзменеяия состояния аналоговс>й памяти интегрирующей цепи, если в линейном цифровом сигнале возникает большое количество пробелов (при этом постоя><ная времени интегрирующей цепи системы синхронизации не изменяется).

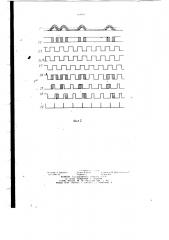

На фиг. 1 показана функциональная схема регенератора; на фиг. 2 — временные диаграммы работы на эпюрах напряжений.

Регенератор цнфровосо сигнала состоит

><ного через первый вналоговыА ключ 4 с выходом усилителя-корректора I, элемента 5 совпадения, форми 2S рователя 6 выходного сигнала. усредяятеля 7 порога н блока 8 тактовоА синхронизации, причем усилитель-корректор L с цепью

2 АРУ, формирователь 3 порогового напряжения с первым аналоговым клвзчом 4 и усреднитель 7 порога, элемент 5 совпадения и формирователь 6 выходного сигйа4<а образуют канал регенерации цифров<>го сигнала, я блок 8 тактовой синхронизация содержит миаертнрующий усилитель-ограничителЬ 9. элемент 10 запрета, второй и третий ан<тлоговне ключи I I н 12, первую и вторую ана35 логовне ячейки 13 н 14 иамятм, вычитаю>ltkA блок 15, интегратор 16. управляемый генератор 17. генератор 18, управляемый напряженнем, трнггерннй фазовращатель

l9 м формировят»ль 20 узких. нмпульсон (фмг I-). При этом второй и третиА аналотовне ключи I I и 12, аналоговые ячейки 13 и l4 памяти, анчитяюи<мй блок 15, интегратор 16, уираалмемнй генератор 17, включаемый управляемым напряжением, н триггермый фаз»<арап<атель 19 образуют систему фазовой автоиодстройкм частоты блока

8 тактовой синхронизация.

Регенератор цифрового сигнала работает следующим образом.

На вход регенератора (фиг. 1) постиа ют искаженные линией связи и помехау мн импульсы цифрового сигнала, пример. ная форма которых после усиления н кор. рекции усилителя показана íà эпа>ре 21 ф (фиг. 2). Лмння внутри заштрихованной области на этом графике прмблизнтельно с соответствует среднему мгновенному значению сигнала. После усиления и ограничения иивертирующим усилителем-ограннчн11<<>бр» т» НН» и»ни«итси к <«лнмк» иере

«;счн инфроян» (,s< >«r><>ax) сигналоа ио линии санин и миж»т быть использовано в кячесгsc окон«чннх и промежуточных регенерап>ров лннейм<>го сигнала многоканаль. ннх снстеч высокочастотной передачи с импульсно кодови илм дельта-модуляцией.

11елью изобретения является повышенис иомехоустоАчнв<>стн регемератора цифрового сигнала эа счет повышения тоности выделения тактовых импульсов путем устрат»»л«м !> (фнг 1) форма сигнала иря<><>1>» тает вмд. иокяэяиный (<а эиюре 22 (фмг 2!

Фронты вн>и>днн» импульсов ограничит»ли

9 могут находитыя в любой точке зацлрн хованных п6.>я»тай эиюры 22. Отрицатель ные импульсы 22 через элемент 10 запрета поступают ня первые входы второго 11 н третьего 12 аналоговых ключей. Если опорные импульсы 23 н 24 (фиг. 2). поступающие с прямого и инверсного выходов трнггерного фвзовращателв 19 (фнг. 1) на вторые входы аналоговых ключей I l н 12, расположены относительно импульсов 22 (т. е. фронты 23 и 24 совпадают с центрамн отрицательных импульсов 22). то прн наличии каждого информационндго импульса

22 на выходах аналоговых ключей 11 í 12 формируют одинаковые в средвем (т е в смысле математического ожндв(<яя) ии <>

25 и 26 ч выходов ан логовых ключеА I l и 12 (фнг. 1). пробелы, оответстаующме и) лям в цифровом сигнал<(. отсутствуют Если ило,цади импульсов 25 и» 26. полученных мз информационного сигнала в среднем одинаковы, то в интегрирующую цепь 16 ч»р»> вычитающнй блок 15 а среднем по»тупя»т нулевоА ток и с<>стояние аналоговой иямм ти интегрнрук>шей с»»ии 16 не изменя»т<.н г!е изменя»тем поэтому и частота сл«доня ния импульсом, генерируемых уиравлн»чнч генератором 17 Прн большом количестве нулей в цифровом сигнале на каждом Td>г- ки торых одинаковы. н состояние аналого ой памяти интегратора 16 также не изменяется

Частота н фаэн колебаниА на выход» ) и рааяяемого генератора 17 в этом сл ча« также не изменяются.

П>сть ио каким.то причинам иромзой дет смешение фазы информационных имиуль. сов 22 от><оснтельно опорных импульсов 23 и 24, например. в сторону опережения !ма иг. 2 — влево), тогда импульсы 25, сфор. мированмые из информационных, станут в реднем шире импульсов 26. которые также сформированы нэ информационных 22 !lp« обладающий. например. положительный «л с выхода вь читаю<«его блока 15 (фн< <

I l 60547 и меннт состояние аналоговой памяти нн. тегратора 16 так, чтобы с изменением часто. ты управляемого генератора 17 произошло смещение фазы опорных импульсов 23 н

24 в сторону опережения до тех пор, пока

Фронты импульсов 23 н 24 не станут сони»дать с центрзмн информационных импульсов 22 (фи 2! (lри заинздыsaнин информационных им пульсон 22 относительно опорных 23 и 27 начинает преобладать. например, отрнца тельный ток на выходе вычитающегЬ блока

15 (фиг. 1), состояние памяти интегратора

Iti изменяется в другую сторону, что ири. водит к снижению частоты и сдвигу фазы управляемого генератора 17 а сторону зн. инздывання Таким образом. систем» авто. подстройки, состоящая нз аналоговых клю. чей I I н 12, ячеек 13 и 14 памяти, вычитающего блока 15, интегрнтора 16. уирнн лнемого генератора -17. включающего генератор 18, управляемый напряженнем, и

rpHr герный фнзоврнщвтель 19, непрерывно следит за средним смещением фазы информационных импульсов н выставляет фронты опорных импульсов так, чтобы они со»пад» ли г серединой приходящих информационных импульсов

Положительный фронт импульсов 24 или отрицательный фронт импульсов 23 посредством элемента 20 нспользуется для формирования узких импульсов 29, предназначенных для опробования информационных импульсов 21 в элементе 5 совпадения, т. е. для регенерации цифрового сигнала.

Для работы системы фазовой автоподстройкн блока 6 синхронизации регенерации используется полная площадь каждого нз информационны» импульсов 22. » именно, упрйвляющее напряжение иа выходе ин ! о тегратора 16 образуется нз разности двух проннтегрироаанных токов. т. е. из полной . энергии каждой пары импульсов 25 н 26.

Использование полной энергии каждого нз информационных,нмпульсо для выделения тактовой частоты пов помехоустойчивость системы синхронизации.

При наличии большого числа нулей в информационном сигнале произвольного смещения фнзы тактовых -импульсов 23 н

70 24 не происходит. В этом случае (т. е, прн отсутствии единиц,. в сигнале 21) импульсы

25 и 26 формируются аналоговыми ключамн

II í l2 нз импульсов 27. получаемых с квадратурного выхода триггерного фазовращателя 19 (фнг, 1) через элемент!0 запрета. ПроIIcxoANT полная подмена информационных импульсов и аналоговая память интегрирующей цепи 16 своего состояния не изменяет.

22

24

27

©иг 2 (ии тннитr >»»

I r.т.> к r(>p . Г ра тнтло .Гг(ргл II IIr;» I ppr»>i>p М Мн» .«»».и «". (» к» > 313<1,53 3»рал(и ! .тикси< е

ВНИИПИ Государствен»»>ги кпиитг>н ((.(.!> по, Лелаи изобретен»Я » открыт»Я

I 1 3035. Москва, Ж 35. Ра»нс как на(>, л н>5

Филиал ППП ° Патент». г У>иго(» л,. 1!рт>ектнвн, »