Логический анализатор

Иллюстрации

Показать всеРеферат

ЛОГИЧЕСКИЙ АНАЛИЗАТОР,содержащий двоичный счетчик, элемент И, регистр, индикатор и.сумматор по модулю два, выходы которого подключены к соответствующим информационным входам регистра, выходы которого подключены к соответствувяцим входам индикатора и первым входам сумматора по модулю, два, вторые . входы которого, кроме последнего, соединены с соответствующими выходами двоичного счетчика, вход установки в О которого подключен к первому входу устройства и входу установки в О регистра, вход синхронизации которого соединен с вьгкодом элемента И, входы которого подключены к второму и третьему входам устройства соответственно, о т л и ч а ю щ и и с я тем, что, с целью повышения достоверности диагностики, счетный вход двоичного счетчика соеди нен с вторым входом устройства, а i. О) последний из вторых входов cy iatopa с по модулю ДВА подключен к пине логи-. ческой единицы.

„„SU„„11 0569

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ASTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

: (21) 3679736/24-21 (22) 26. 12. 83 (46) 07.06.85. Бюл. № 21 (72) Э.N. Витенберг, В.И. Луценко, И.Д. Шварцбанд и Н.П. Шибря (71) Научно-производственное объединение по радиоэлектронной медицинской аппаратуре (53) 621.294.14(088.8) (56) 1. "Электроника", 1977, Ф 5, .с. 26, 27, рис. 2..

2. Авторское свидетельство СССР № 1091339 кл. Н 03 К 13/32, 01.07.82, (54)(57) ЛОГИЧЕСКИЙ АНАЛИЗАТОР,содержащий двоичный счетчик, элемент И, регистр, индикатор и сумматор по модулю два, выходы которого подключены к соответствующим информационным входам регистра, выходы котоа(з1) Н 03 N 13/00 Н 03 К 13/32 рого подключены к соответствующим входам индикатора и первым входам сумматора по модулю. два, вторые входы которого, кроме последнего, соединены с соответствующими выходами двоичного счетчика, вход установки в

"0" которого подключен к первому входу устройства и входу установки в "0" регистра, вход синхронизации которого соединен с выходом элемента И, входы которого подключены к второму и третьему входам устройства соответственно., о т л и ч а юшийся тем, что, с целью повьппения достоверности диагностики, счетный вход двоичного счетчика соеди-. . ® нен с вторым входом устройства, а ь / последний из вторых входов сумматора по модулю два подключен к шине логи- С ческой единицы. а

1 1160569

Изобретение относится к импульс .: к ной технике и может быть применено ; ве для наладки, ремонта и контроля чи цифровых устройств (например, ЭВМ, по микропроцессорные системы и прочее}. 5 ва

Известен логический анализатор, вх содержащий регистр, индикатор и сум- с матор по модулю два, входы которого го подключены к выходам соответствующих му разрядов регистра сдвига, вход кото- щ но рого соединен с выходом сумматора по со модулю два Я е ва

Недостатком этого устройства яв- ма ляется невозможность локализовать не ошибку во входной последовательности.15

Наиболее близким техническим ре- на шением к предлагаемому является логический анализатор, содержащий дв двоичный счетчик, элемент И, регистр, мо индикатор и сумматор по модулю два, 20 и вьмоды которого подключены к соответ- ти ствующим информационным входам реги- "1 стра, выходы которого подключены к соответствующим входам индикатора и со первым входам сумматора по модулю 25 "0 два, вторые входы которого, кроме 3, последнего, соединены с соатветст- до вующими выходами двоичного счетчи- вх ка, вход установки в "0" которого со подключен к первому входу устройст- ре ва и входу установки в "0" регист- не ра вход синхронизации которого вь соединен с выходом элемента И, входы дв которого подключены к второму и со третьему входам устройства соответто ственно, при этом двоичный счетчик З5 не входит в состав счетчика с исключен- ло ным нулевым состоянием, содержащим, - вт кроме этого, три элемента И-НЕ и триггер (2 . сл

Однако известному логическому анализатору присуща недостаточная вх достоверность диагностики, заклюли чающаяся в невозможности выявления п ошибки более, чем в двух разрядах на входной последовательности. ф5 хр

Цель изобретения — повышение дос- ва товерности диагностики. си

Для достижения поставленной цели в логическом анализаторе, содержащем 50 двоичный счетчик, элемент И, регистр, индикатор и сумматор по модулю два, выходы которого подключены к соответствующим информационным входам регистра, вьмоды которого под- 55 ключены к соответствующим входам индикатора и первым входам сумматора по модулю два, вторые входы которого, роме последнего, соединены с сооттствующими выходами двоичного счетка, вход установки в "0" которого дключен к первому входу устройсти входу установки в "0" регистра, од синхронизации которого соединен вьмодом элемента И, входы котороподключены ко второму и третьевходам устройства соответственсчетный вход двоичного счетчика единен со вторым входом устройста последний из вторых входов сумтора по модулю два подключен к шилогической единицы.

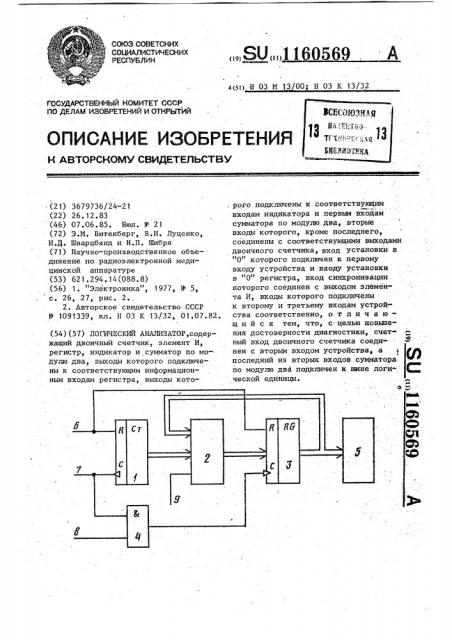

На чертеже приведена функциональя схема логического. анализатора.

Логический анализатор содержит оичный счетчик 1, сумматор 2 по дулю два, регистр 3,. элемент И 4, ндикатор 5, первый, второй и трей входы 6-8, шину 9 логической

tt

Вход 6 логического анализатора единен со входами установки в

" двоичного счетчика 1 и регистра вход 7 соединен со счетным вхом двоичного счетчика 1 и первым одом элемента И 4, выход которого единен со входом синхронизации гистра 3. Вьиоды регистра 3 соедины со входами индикатора 5 и перпи входами сумматора 2 по модулю а. Выходы двоичного счетчика 1 единены со вторыми входами суммара 2 по модулю два, кроме последго, который соединен с шиной 9 гической " 1". Вход 8 подключен ко орому входу элемента И 4.

Логический анализатор работает едующим образом.

Перед началом работы импульсом по оду 6 счетчик 1 и регистр 3 устанаввают в состояние "О". Проверяемую оследовательность подают на вход 8, вход 7 подают синхроимпульсы,синонизирующие каждый разряд последотельности. По переднему фронту нхроимпульсов происходит запись в регистр 3, по заднему — переключение счетчика 1.

Состояние выходов регистра 3 описывается уравнением где k — длина последовательности;

Д.;: — значение i-ro бита последовательности,4„ Г 1 О, 1);

Последовательность с ошибками мож- 15 но прадставить в виде с(= с"О+е

1 . I где е- последовательность, содержащая "0" в правильных битах и

" 1". в битах, где есть ошибка. 2О

Тогда, воспользовавшись линейностью операции,(1), можно записать и

Р4)= ((; +е„)И; = рЫ) +, >,. (3:)

<=1 .=1 25 где 1, j — номера бит, содержащих ошибку; ч — количество бит, содержащих ошибку.

Обнаружение и локализация ошибки 30 производится путем анализа суммы Д по модулю два. состояния /3 (с() регистра 3 для заведомо правильной последовательности и состоягия J1 уГ (й ) — для анализируемой последова35 тельности, возможно содержащей ошибки.

Из формулы (3) следует (4) > =ВЫ ) + ((). =, h"

1J

J=1

Подставив значение формулы (2) в формулу (4), получим (1) тодя у „" " " (5)

< 1 ) V ДЛЯ .Д =, > tij 1) 45

3=1

Отсюда вытекают следующие выводы.

Для последовательности любой .длины любые ошибки в нечетйом числе 5О бит будут обнаружены, так как

Д =У Ы2= 1.Ф 03 (1) для последовательности длиной

» 2" при ошибке в одном бите

<Г-1)

Д следовательно, такая ошибка однозначно локализуется:

55 з 11605

h — сигнал на входах сумматора по модулю два Hà i-ом шаге. с — суммирование по модулю 2.

Обозначим содержимое (r-1) разрядов, у .которых входы сумматора 2 соединены со .счетчиком, индексом г-1, содержимое г-ro разряда, для которого вход сумматора 2 подключен к шине

9 логической. единицы, индексом " 1".

Тогда 1О

fr 1 д " (2) (r -1)

i1=k+ 1 где i1 — номер ошибочного бита; для.последовательности длиной

k < 2 при ошибке в двух битах:

Д =(,-1l О (1,-1) =О, (r- 1

Г так как 11 Ф 1, следовательно, любая такая ошибка будет обнаружена.

П р и м е. р. Пусть число r разрядов регистра, сумматора по модулю два и счетчика будет равно 4 и исходная (эталонная) последовательность будет длиной 17 бит:

01110100001011001. Введем ошибки в 1, 2, 7, 9 и 13 биты:

01 1 1 1 100 1000 1 1010 (счет бит идет с конца) .

Состояния выходов счетчика 1, сумматора 2 по модулю два, регистра 3 при проверке исходной и ошибочной последовательностей для каждого такта работы анализатора приведены в таблице, причем состояния выходов регистра приведены для момента времени после окончания синхроимпульса соответствующего такта, а состояния выходов счетчика и сумматора по модулю два — для момента времени между передним и задним фронтами синхроимпульса.

Сравнение результирующих состояний выходов регистра 3 для исходной и .ошибочной последовательностей показывает нх несовпадение, что указывает на наличие ошибки (см. таблицу) .

При подключении устройства показания индикатора 5 в случае наличия однобитовой ошибки или двухбитовой ошибки при k Й 2 будут отличаться от показания для правиль- ". ной последовательности, таким образом, эти ошибки будут обнаружены;воэможна локализация однобитовой ошибки при k 6 2 . Кроме того, при любых k возможно выявление ошибок в любом нечетном числе бит.

Таким образом, подключение счетного входа двоичного счетчика ко входу сйнхрониэации, а последнего иэ вторых входом сумматора по модулю два к шине логической "1" повышает .достоверность диагностики цифровых устройств с помощью предложен ного логического анализатора, 1160569

Проверяемая последовательность

Номе такт г

ыход четчика

3 2 1

С ошибками

Исходная

i Выход регистра

Выход су матора

Выход сумматора

Вход

Выход регистра

4 3 2.1 4 3 2 1

4 3 2 1 4 3 2 1

О О О 1 О

О 1 1 1 О

О

1 1

О О О 1 1 1 1 1 0

О О 1 О

12

1 О О О О 1 } О 1 О 1 О 1 О 00 1 О О

О 1

О О

1 1 1 О О 1 1

О 1 1 1 0, 1 1 1

1 О 1 1

1 1 О 1

1 1 1 1

О О О О!

17

Составитеиь О. Ревинский

Редактор Н. Егорова Техред И.Пароцай . Корректор M. Розман

Заказ 3842/54 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

О О О 1

О О 1 О

О 1 О О

О 1 1 1

1 О 0 1

1 О 1 О

1 1 О

1 1 1 О

О О О О

О О 1 О

0 1 О О

О 1 1 1

1 О 0 О 1 О О О О 1 О О О О О О О

О О 0 1 1 О О О 1 1 00 1 1 О О 1

О О 1 0 1 О О О О О О 1 1 1 0 О 1

О О 1 1 О О 1 1 1 О

111.1111111

0 О О 1 О О О 1 О О О О О 1 1 1 О

1 1 1 О О О 0 1 О О О О 1 1 1 1 О

О О 1 О О О 1 1 О 1 1 О О 1 1 О

1 О 0 О О О О 1 О 1 1 1 1 О 1 1 О

О 1 1 О 0 О 1 О 1 1 О О О 1 1 О О 1 О 1 О 1 О 1 1 10 1 1 1 О

1 О О 1 1 О О 1 1 О О 1 О О О 1 О

О 1 1 О О 1 1 О 1 1 1 О 1 1 1 О 1

1 1 О О 1 1 О О О 1 О 1 1 1 О 1