Устройство регистрации полярных сигналов

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО РЕГИСТРАЦИИ ПОЛЯРНЫХ СИГНАЛОВ, содержащее последовательно соединенные накопитель и пороговый элемент, отличающееся тем, что, с целью расширения диапазона регистрируемых сигналов, в него введены триггер, первый и второй инверторы, первый и второй элементы И-НЕ, первый и второй элементы И и элемент ИЛИ, а накопитель выполнен в виде реверсивного счетчика , причем пороговый элемент выполнен в виде блока постоянной памяти, при этом первые входы первого и второго элементов И объединены и являются тактовым входом устройства, информационным входом которого являются объединенные информационный вход триггера, .второй вход первого элемента И и вход первого инвертора , выход которого соединен с вторым входом второго элемента И, выходы первого и второго элементов И соединены соответственно с суммирующим и вычитающим входами накопителя, вход «Сброс которого соединен с объединенными счетным входом триггера и выходом элемента ИЛИ, входы которого соединены с первым и вторым выходами порогового элемента , третий выход которого соединен с объединенными первыми входами первого и втоS рого элементов И-НЕ, выходы которых (Л соединены с третьими входами соответственно первого и второго элементов И, выход триггера соединен с вторым входом первого элемента И-НЕ и через второй инвертор - с вторым входом второго элемента И-НЕ. S 05 О О5 о со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

a(5D H 04 М 3 50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1Ь

1Р

1Ь

CO О

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3681042/24-09 (22) 27. 12.83 (46) 07.06.85. Бюл. № 21 (72) М. А. Жарков и В. О. Сергеев (53) 621.395.387 (088.8) (56) 1. Емельянов Г. А. Шварцман В. О.

Передача дискретной информации, М., «Радио и связь», 1982, с. 42, рис. 3.5.

2. Справочник по интегральным микросхемам. Ред. Б. В. Тарабрин. М., «Энергия», 1981, с. 636, рис. 5 — 107 (прототип). (54) (57) УСТРОЙСТВО РЕГИСТРАЦИИ

ПОЛЯРНЫХ СИГНАЛОВ, содержащее последовательно соединенные накопитель и пороговый элемент, отличающееся тем, что, с целью расширения диапазона регистрируемых сигналов, в него введены триггер, первый и второй инверторы, первый и второй элементы И вЂ” НЕ, первый и второй элементы И и элемент ИЛИ, а накопитель выполнен в виде реверсивного счетчика, причем пороговый элемент выполнен в виде блока постоянной памяти, при этом

„,Я0„„1160603 A первые входы первого и второго элементов И объединены и являются тактовым входом устройства, информационным входом которого являются объединенные информационный вход триггера, второй вход первого элемента И и вход первого инвертора, выход которого соединен с вторым входом второго элемента И, выходы первого и второго элементов И соединены соответственно с суммирующим и вычитающим входами накопителя, вход «Сброс» которого соединен с объединенными счетным входом триггера и выходом элемента ИЛИ, входы которого соединены с первым и вторым выходами порогового элемента, третий выход которого соединен с объединенными первыми входами первого и второго элементов И вЂ” НЕ, выходы которых соединены с третьими входами соответственно первого и второго элементов И, выход триггера соединен с вторым входом первого элемента И вЂ” НЕ и через второй инвертор— с вторым входом второго элемента И вЂ” НЕ.

1160603

55

Изобретение относится к электросвязи и может быть использовано в автоматических телефонных станциях для организации междугородной связи.

Известно устройство регистрации полярных сигналов, содержашее последовательно соединенные накопитель и пороговый элемент (1) .

Недостатком устройства является узкий диапазон регистрируемых сигналов, обусловленный фиксированным объемом накопителя.

Наиболее близким к предлагаемому является устройство регистрации полярных сигналов, содержащее последовательно соединенные накопитель и пороговый элемент (2).

Недостатком известного устройства является узкий диапазон регистрируемых сигналов.

Цель изобретения — расширение диапазона регистрируемых сигналов.

Для достижения поставленной цели в устройство регистрации полярных сигналов, содержащее последовательно соединенный накопитель и пороговый элемент, введены триггер, первый и второй инверторы, первый и второй элементы И вЂ” HE, первый и второй элементы И и элемент ИЛИ, а накопитель выполнен в виде реверсивных счетчика, причем пороговый элемент выполнен в виде блока постоянной памяти, при этом первые входы первого и второго элементов И объединены и являются тактовым входом устройства, информационным входом которого являются объединенные информационный вход триггера, второй вход первого элемента И и вход первого инвертора, выход которого соединен с вторым входом второго элемента И, выходы первого и второго элементов И соединены соответственно с суммирующим и вычитающим входами накопителя, вход

«Сброс» которого соединен с объединенными счетным входом триггера и выходом элемента ИЛИ, входом которого соединены с первым и вторым выходами порогового элемента, третий выход которого соединен с объединенными первыми входами первого и второго элементов И вЂ” HE, выходы которых соединены с третьими входами соответственно первого и второго элементов И, выход триггера соединен с вторым входом первого элемента И вЂ” НЕ и через второй инвертор — с вторым входом второго элемента И вЂ” НЕ.

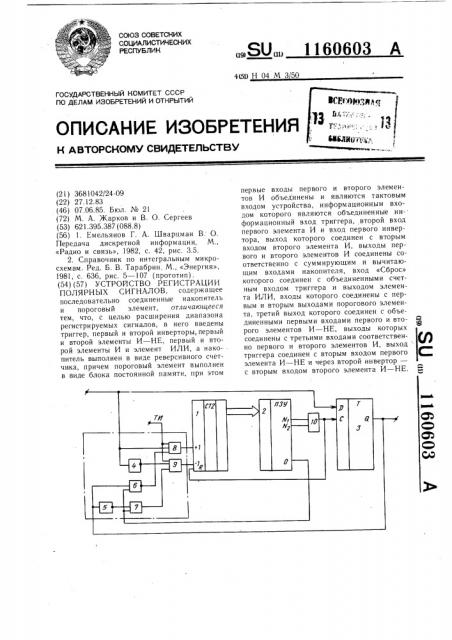

На чертеже приведена структурная электрическая схема устройства регистрации полярных сигналов.

Устройство регистрации полярных сигналов содержит накопитель 1, пороговый элемент 2, триггер 3, первый и второй инверторы 4 и 5, первый и второй элементы

И вЂ” НЕ 6 и 7, первый и второй элементы И 8 и 9 и элемент ИЛИ 10.

Устройство регистрации полярных сигналов работает следующим образом.

На тактовый вход поступают тактовые импульсы с частотой, обеспечивающей заданную точность регистрации. На информационный вход устройства поступает входной сигнал и в исходном состоянии накопитель 1 находится в нулевом состоянии, полярность выходного сигнала совпадает с полярностью входного. Нулевое состояние накопителя 1 поступает на вход порогового элемента 2, в результате чего на его третьем выходе имеется выходной сигнал («1»), который обеспечивается соответствующим программированием в пороговом элементе 2 ячейки с «нулевым» адресом. Этот выходной сигнал «разрешает» проключить значение выходной полярности с выхода триггера 3 через первый элемент

И вЂ” HE 6 или второй элемент И вЂ” HE 7 на соответственно первый и второй элементы И

8 и 9 запрещая совпадение сигналов на входах одной из них. При входной полярности, соответствующей логической «1» выходной полярностью, ей соответствующей, заперт первый элемент И 8 при входной полярности «О» и выходной полярностью, ей соответствующей, заперт второй элемент И 9.

Тем самым, если полярность на информационном входе не меняется и на выходе полярность соответствует входной, на входы накопителя 1 не поступают импульсы с тактового входа и он продолжает находиться в нулевом состоянии. Изменение полярности на информационном входе разрешит проключение через соответствующий первый и второй элементы И 8 и 9 на накопитель 1, пороговый элемент 2 перейдет в состояние, отличное от нулевого и с его третьего выхода снимается сигнал, разрешающий выходному потенциалу, поступающему с выхода триггера 3, управлять работой первого и второго элементов И 8 и 9. Накопитель 1 под действием тактовых импульсов, поступающих в соответствии с изменением полярности, на информационном входе по входу сложения или вычитании начнет и интегральный подсчет длительности преобладающей полярности, накапливая значения времени, соответствующие поступлению полярности сигнала, и вычитая значение времени, соответствующее ее изменению.

При достижении значения счетчика, соответствующего заданному значению длительности интегрирования (времени распознавания прихода полярности), на вход порогового элемента 2 поступает это значение, затем на соответственном выходе порогового элемента 2 появляется сигнал, 1160603

Составитель В. Шевцов

Редактор E. Лушникова Техред И. Верес Корректор М. Демчик

Заказ 3845/56 Тираж 659 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, K — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 который через элемент ИЛИ 10 поступает на вход сброса накопителя 1, вызвав его сброс в «О», и на вход записи триггера 3.

Таким образом, полярность, поступившая на информационный вход, запишется в триггер 3 и схема в соответствии с предыдушим описанием придет в исходное состояние.

Использование изобретения позволяет расширить диапазон регистрируемых сигналов и повысить устойчивость устройства регистрации к импульсным помехаа.