Устройство для исправления одиночных и обнаружения многократных ошибок

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО Щ1Я ИСПРАВЛЕНИЯ ОДИНОЧНЫХ И ОБНАРУЖЕНИЯ МНОГОКРАТНЫХ ОШИБОК, содержащее последовательно соединенные накопитель, первьй информационный вход которого является входом устройства, и полусумматор , выход которого подключен к второму информационному входу накопителя , второй выход которого подключен к информационному входу первого ключа, к первому управляющему входу которого подключен первый выход блока обнаружения ошибок,второй выход-которого подключен к первому входу датчика ошибок и к информационному входу второго ключа, управляющий вход которого объединен с вторым управляющим входом первого ключа и соединен с первым выходом блока управления, второй и третий выходы которого подключены соответственно к управляющему входу накопителя и к второму входу датчика ошибок, причем выходы первого и второго ключей являются выходами устройства , отличающееся тем, что, с целью сокращения.времени обнаружения ошибок, в него введен вычислитель синдрома, при этом информационный вход вычислителя синдрома объединен с первым информационным входом накопителя, к первому и второму управляющим вхо- . дам вычислителя синдрома подключены соответственно второй и четвертый выходы блока управления, а выход вычислителя синдрома подключен к первому входу блока обнаружения ошибок, к второму входу которого подключен выход датчика ошибок, а дополнительный выход блока обнару (/) жения ошибок подключен к другому входу полусумматора. 2. Устройство по п.1, о т л ичающееся тем, что датчик ошибок содержит входной ключ и последовательно соединенные первый и второй триггеры, первый полусумматор , третий триггер, второй полусумматор и четвертый триггер, прямой выход которого подключен к СП информационному входу первого триггера и к вторым входам первогои второго полусзп маторов, выход входного ключа подключен к управляющим входам первого, второго, третьего и четвертого триггеров, выходы которых являются выходами датчика ошибок.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСЦИХ

РЕСПУБЛИН а() Н 03 M 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

° ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНЯТИЙ (21) 3582438/24-.09 (22) 22.04.83 (46) 15.06.85. Бюл. Ф 22 .(72) Г.С. Евсеев и Е.А. Крук (71) Ленинградский институт авиационного приборостроения (53) 621.394.14 (088.8) (56) Авторское свидетельство СССР

9 72I817, 1980.

Авторское свидетельство СССР

Р 625312, 1978. (54)(57) 1. УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОДИНОЧНЫХ И ОБНАРУЖЕНИЯ МНОГОКРАТНЫХ ОШИБОК, содержащее последовательно соединенные накопитель, первый информационный вход которого является входом устройства, и полусумматор, выход которого подключен к второму информационному входу накопителя, второй выход которого подключен к информационному входу первого ключа, к первому управляющему входу которого подключен первый выход блока обнаружения ошибок,второй выход -которого подключен к первому входу датчика ошибок и к информационному входу второго ключа, управляющий вход которого объединен с вторым управляющим входом первого ключа и соединен с первым выходом блока управления, второй и третий выходы которого подключены соответственно к управляющему входу накопителя и к второму входу датчика ошибок, причем выходы первого и вто„„SU„„1 2053 А рого ключей являются выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью сокращения времени обнаружения ошибок, в него введен вычислитель синдрома, при этом информационный вход вычислителя синдрома объединен с первым информационным входом накопителя, к первому и второму управляющим входам вычислителя синдрома подключены соответственно второй и четвертый выходы блока управления, а выход вычислителя синдрома подключен к первому входу блока обнаружения ошибок, к второму входу которого подключен выход датчика ошибок, а дополнительный выход блока обнаружения ошибок подключен к другому входу полусумматора.

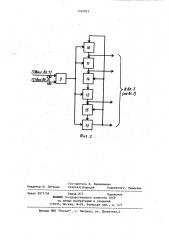

2. Устройство по п.1, о т л ич а ю щ е е с я тем, что датчик ошибок содержит входной ключ и последовательно соединенные первый и второй триггеры, первый полусумматор, третий триггер, второй полусумматор и четвертый триггер, прямой выход которого подключен к информационному входу первого триггера и к вторым входам первогои второго полусумматоров, выход входного ключа подключен к управляющим входам первого, второго, третьего и четвертого триггеров, выходы которых являются выходами датчика ошибок.

1 11620

Изобретение относится к технике связи, а именно к устройствам для обнаружения и/или предотвращения ошибок в принятой, информации, а также может быть отнесено к импульс- 5 ной технике, а именно к устройствам для коррекции ошибок.

Цель изобретения — сокращение времени обнаружения ошйбок.

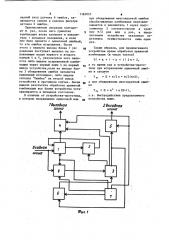

На фиг.1 представлена структурная 10 электрическая схема устройства для исправления одиночных и обнаружения многократных ошибок, на фиг.2— вариант реализации датчика ошибок.

Устройство содержит накопитель 1, 15 полусумматор 2, блок 3 обнаружения ошибок, первый и второй ключи 4 и 5, датчик 6 ошибок, блок 7 управления и вычислитель 8 синдрома, причем датчик б ошибок содержит входной ключ Я 20 первый, второй, третий и четвертый триггеры 10, 11, 12 и 13 и первый и второй полусумматоры 14 и 15.

53 2, в том символе, который находится в

Устройство работает следующим об2S разом.

Прием комбинации осуществляется путем подачи и импульсов сдвига с второго выхода блока 7 управления на управляющий вход накопителя 1, в результате чего через 1 тактов при-З0 нятая комбинация записана в накопитель 1. Одновременно 1 импульсов сдвига с второго выхода блока 7 уп- равления поступают.на первый управляющий вход вычислителя 8 синдрома, 3S на втором управляющем входе которого присутствует разрешающий сигнал с четвертого выхода блока 7 управления, а на информационный выход вычислителя 8 синдрома последовательно поступают символы принимаемой комбинации. В результате через И тактов в вычислителе 8 синдрома будет записан синдром принятой комбинации.

4S

Если ошибки в принятой комбинации отсутствуют,то на,первом выходе блока обнаружения ошибок формируется разрешающий сигнал, который поступает на первый управляющий вход первого50 ключа 4, а на втором выходе — запрещающий сигнал, который поступает на информационный вход второго ключа 5 и на первый вход датчика 6 ошибок, запрещающий осуществление в нем .55 сдвигов. При подаче на второй управляющий вход первого ключа 4 разрешающего сигнала с первого выхода блока 7 управления информация из накопителя 1 выдается получателю.

Если в принятой комбинации обнаружены ошибки, то исправление однократной ошибки происходит за и тактов работы, причем на каждом такте осуществляются следующие операции.

С выходов датчика 6 ошибок и вычислителя 8 синдрома записанные в них Ф -разрядные числа (щ — число проверочных символов в используемом коде) параллельным кодом поступают на входы блока 3 обнаружения ошибок, где вычисляется их поразрядная сумма по модулю два.

Если комбинации, записанные в датчике 6 ошибок и в вычислителе 8 синдрома, совпадают, то формируется единичный сигнал, который поступает на второй вход полусумматора 2.

В противном случае на второй вход полусумматора 2 поступает нулевой сигнал, который не изменяет значение сигнала на его первом входе.

С второго выхода блока .7 управления на управляющий вход накопителя 1 и на первый управляющий вход вычислителя 8 синдрома подается импульс сдвига. Чтобы при этом в вычислителе 8 синдрома сдвиг не происходил, на его второй управляющий вход с четвертого выхода блока 7 управления подается запрещающий сигнал. При этом в накопи- теле 1 происходит сдвиг принятой комбинации и очередной ее символ переписывается из последней ячейки накопителя 1 в первую ячейку беэ изменения, если на втором входе полусумматора 2 нулевой сигнал, и инвертируется при переписывании в противном случае. !

С третьего выхода блока 7 управления поступает на второй вход датчика 6 ошибок импульс сдвига.

Если одиночная ошибка еще не исправлена, то в датчике 6 ошибок. происходит сдвиг, в результате чего в первый, второй. третий и четвертый триггеры 10,11,12 и 13 записывается синдром одиночной ошибки последней (в направлении сдвига) ячейке накопителя 1. Если же одиночная ошибка уже исправлена, то сигналом с второго выхода блока 3 обнаружения ошибок, поступающим на

1162053 4 при обнаружении многократной ошибки обрабатываемая комбинация перезапиI сынается в накопитель 1 через полусумматор 2 соответственно в сред" нем П/2 раз или 11 раз, в предлагаемом устройстве указанная перезапись осуществляется лишь один й, раз. з первый вход датчика 6 ошибок, запрещаются сдвиги в кодовом фильтре датчика 6 ошибок.

Перечисленные операции повторя-. ют tl раз, после чего принятая комбинация вновь занимает в накопителе 1 исходное положение, и если оно было принято с одиночной ошибко то эта ошибка исправлена. После этого с первого выхода .блока 7 уп- 1п равления поступает импульс на управляющие входы первого и второго ключей 4 и 5, результатом чего является либо выдача исправленной комбинации через первый ключ 4 на первый выход устройства, если на выходе блока 3 обнаружения ошибок находится единичный потенциал, либо выдача сигнала "Ошибка" на второй выход устройства в противном. случае..После выдачи результата обработки принятой комбинации все блоки устройства устанавливаются в исходное состояние °

В отличие от устройства-прототипа, в котором исправление одиночной или

Таким образом, для предлагаемого устройства время обработки принятой комбинации (в числе тактов) Т1 =И +1+и+ 112И+2, в то время как в устройстве-прототипе при исправлении одиночной ошибки в среднем

T„, = П + n/2n = и/2(h+2), а при обнаружении многократной ошибки

Т „, - II + h = ц (П+1), т.е, быстродействие предлагаемого устройства выше.

7ЮыхИН497

ЙЙ/ИО

2Фиюдюая

ШИИТ

1162053

Составитель В. Евдокимова

Редактор М. Петрова ТехредМ.Пароцай Корректор Г. Решетник

Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 3977/56

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4

8дл. З (на 1к. 1)