Формирователь адресных сигналов для блоков памяти

Иллюстрации

Показать всеРеферат

1. ФОРМИРОВАТЕЛЬ,АДРЕСНЫ СИГНАЛОВ ДЛЯ БЛОКОВ ПАМЯТИ, содер жащий три инвертора, вход первого из которых является входом формирователя , отличающийс я тем, что, с целью повышения помехоустойчивости формирователя он содержит парафазный усилитель на транзисторах, нагрузочный элемент на транзисторе с обеднением заряда и ключевой элемент на тран А8%I зисторе, причем выход первого инвертора соединен с затвором первого транзистора парафазного усилителя , затвор второго транзистора которого подключен к входу формирователя , стоки первого и второго транзисторов подключены соответственно к шине питания и общей шине, истоки объединены и подключены к входу третьего инвертора и истоку транзистора ключевого элемента, затвор которого подключен к выходу третьего инвертора, а сток - к второго инвертора и истоку н затвору транзистора с обеднением заряда нагрузочного элемента. 2. Формирователь по п. о тличающийся тем, что на грузочный транзистор второго инвертора выполнен с обеднением заряда .

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТ ИЧЕСНИХ

РЕСПУБЛИК

4(5I) 0 1 1 С 7/00

7 сЪ -ър

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

il3., Ид

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

AO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3583437/24-24 (22) 27.04.83 (46) 23.06,85. Бюл. Ф 23 (72) А.Г.Солод, А.М.Копытов и С.В.Высочина (53) 681.327.6(088.8) (56) Патент США Ф 3927334, кл. G 11 С 7/00, опублик. 1976 °

Патент США Ф 4124900 кл. G 11 С 7/00, опублик. 1978. (54)(57) 1. ФОРМИРОВАТЕЛЬ, АДРЕСНЫХ .СИГНАПОВ ДЛЯ БЛОКОВ IIAMIITH содержащий три инвертора, вход первого из которых является входом формирователя, о т л и ч а ю щ и йс я тем, что, с целью повышения помехоустойчивости формирователя, он содержит парафаэный усилитель на транзисторах, нагрузочный элемент на транзисторе с обеднением заряда и ключевой элемент на тран„„SU„„1 163354 зисторе, причем выход первого ин- . вертора соединен с затвором первого транзистора парафазного усилителя, затвор второго транзистора которого подключен к входу формирователя, стоки первого и второго транзисторов подключены соответственно.к шине питания и общей шине, истоки объединены и подключены .к входу третьего инвертора и истоку транзистора ключевого элемента, эатвор которого подключен к выходу третьего инвертора, а сток — к входу второго инвертора и истоку н затвору транзистора с обеднением заряда нагрузочного элемента.

2. Формирователь по п. I, о тл и ч а ю шийся тем, что нагруэочный транзистор второго ин.вертора выполнен с обеднением заряда. г.

1 116335

Изобретение относится к вычисли- " тельной технике и может быть применено в качестве формирователей ад ресных и других типов импульсных сигналов. 5

Цель изобретения — повышение помехоустойчивости.

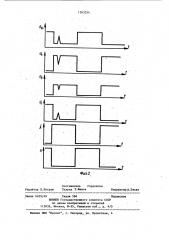

На фиг. 1 представлена принципиальная электрическая схема устройства, на фиг. 2 — временные диаграммы работы.

Формирователь адресных сигналов содержит первый инвертор (транзисторы 1 и 2), второй.инвертор (транзисторы 3 и 4), третий инвертор (транзисторы 5 и 6), парафазный усилитель (транзисторы 7 и 8), иагрузочный элемент на транзисторе 9 с обеднением в ключевой элемент на транзисторе 10.

Вход первого инвертора на транзисторах 1 и 2 является входом формирователя, а выход подключен к затвору верхнего транзистора 7 парараэного усилителя, затвор транзис- 2 .тора 8 которого соединен с входом фор мирователя. Выход парафазного усилителя соединен с входом третьего инвертора (эатвор транзистора 6) и с истоком транзистора ключевого эле- 30 мента 10, затвор которого подключен к выходу третьего инвертора на транзисторах 5 и 6, а сток — к входу второго инвертора на транзисторах

3.и 4 и к истоку и затвору нагрузочного элемента на транзисторе 9 с обеднением заряда.

Формирователь работает следующим образом.

При поступлении на вход схемы 4О сигнала с уровнем логического нуля .транзисторы 2 и 8 закрываются и на затворе транзистора 6 устанавливается положительный потенциал. ТранI зистор 6 открывается, и на затворе транзистора 1О устанавливается нулевой потенциал, транзистор 10 закрывается и на выход А поступает поло жительный потенциал, раВный напряжению источника питания. Транзистор

4 открывается и на выходе А устанавливается нулевой потенциал. При поступлении на вход схемы сигнала с уровнем логической единицы транзисторы 2 и 8 открываются и на затворе транзистора 6 устанавливается нулевой потенциал. Транзистор 6 закрывается, на затворе транзистора 10 устанавливается положительный потенциал, который открывает транзистор !

О, и на входе А устанавливается ну-, левой. потенциал . Транзистор 4 закрывается и .на выходе А устанавливается положительный потенциал, равный наПряжению источника питания.

Работа формирователей адресных " сигналов в случае, если уровень .нуля входного адресного сигнала равен пороговому йапряжению MOII транзисторов (фиг . 2 1, является худшим случаем и на вход схемы поступает помеха положительной полярности.

Появление помехи положительной полярности на входе устройства вызы-. вает понижение потенциала в точке b . Однако понижение потенциала в точке b приводит к повышению потен- циала в точке С,. что вызывает открывание транзистора !О и увеличение тока через транзистор 8, что, в свою очередь,.вызывает Повышение потенци-. ала в узле h и, соответственно, понижение потенциала в узле С, Транзистор

10 имеет двойное управление по истоку и затвору, что приводит к его быстрому запиранию и восстановлению потенциала .на выходе А.

1163354

Аох

Составитель Гордонов а

Редактор В.Петраш Техред T.Ôàíòà Корректор А.Тяско

Заказ 4105/49 Тираж 584 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4