Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее блок памяти, адресные входы которого подключены к выходам блока формирования адреса, информационные входы блока памяти соединены с выходами блока коммутации, первый и второй входы блока формирования адреса являются первым и вторым управляющими входами устройства и соединены соответственно с входами первого и второго счетчиков, третий вход блока формирования адреса, вход управления блока памяти и вход элемента НЕ объединены и являются третьим управляющим входом устройства, выход элемента НЕ подключен к четвертому входу блока формирования адреса, отличающееся тем, что, с целью повышения надежности устройства, оно содержит две группы элементов И-ИЛИ, первые, вторые, третьи и четвертые входы элементов И-ИЛИ первой группы соединены соответственно с выходами первого счетчика, выходами второго счетчика , входом элемента НЕ, выходом элемента НЕ, выходы элементов И-ИЛИ первой группьг подключены к одним входам блока коммутации , другие входы которого соединены с выходами элементов И-ИЛИ второй группы, первые,. вторые, третьи и четвертые входы которых соединены соответственно с информационными входами устройства, информационными выходами блока памяти, входом элемента НЕ, выходом элемента НЕ, управляющий вход блока коммутации подключен к третьему управляющему входу устройства, информационными выходами которого являются выходы блока коммутации.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1163358

+сю б 06 F 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3736111/24-24 (22) 29.04.84 (46) 23.06.85. Бюл. № 23 (72) В. С. Лупиков, С. С. Спиваков и В. В. Богданов (53) 681.327.6 (088.8) (56) Авторское свидетельство СССР № 822287, кл. G 11 С 9/00, 1981.

Авторское свидетельство СССР № 1049968, кл. G 11 С 9/00, 1983. (54) (57) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО, содержащее блок памяти, адресные входы которого подключены к выходам блока формирования адреса, инфор мационные входы блока памяти соединены с выходами блока коммутации, первый и второй входы блока формирования адреса являются первым и вторым управляющими входами устройства и соединены соответственно с входами первого и второго счетчиков, третий вход блока формирования адреса, вход управления блока памяти и вход элемента НЕ объединены и являются третьим управляющим входом устройства, выход элемента НЕ подключен к четвертому входу блока формирования адреса, отличающееся тем, что, с целью повышения надежности устройства, оно содержит две группы элементов И-ИЛИ, первые, вторые, третьи и четвертые входы элементов И-ИЛИ первой группы соединены соответственно с выходами первого счетчика, выходами второго счетчика, входом элемента НЕ, выходом элемента

НЕ, выходы элементов И-ИЛИ первой группы подключены к одним входам блока коммутации, другие входы которого соединены с выходами элементов И-ИЛИ второй группы, первые, вторые, третьи и четвертые входы которых соединены соответственно с информационными входами устройства, информационными выходами блока памяти, входом элемента НЕ, выходом элемента НЕ, управляющий вход блока коммутации подключен к третьему управляющему входу устройства, информационными выходами которого являются выходы блока коммутации.

1163358

Изобретение относится к вычислительной технике и может быть использовано при построении буферных запоминающих устройств в подсистемах ввода измерительной информации.

Цель изобретения — повышение надежности устройства.

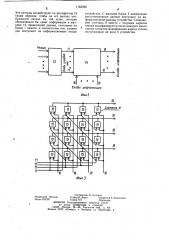

На фиг. 1 показана структурная схема предлагаемого устройства; на фиг. 2 структурная схема блока коммутации; на фиг. 3 — структурная схема матрицы элементов И.

Устройство содержит блок 1 памяти, блок 2 формирования адреса, блок 3 коммутации, первый управляющий вход 4 модификации адреса записи, второй управляющий вход 5 модификации адреса чтения, третий управляющий вход 6 задания режима, первый 7 и второй 8 счетчики, первую 9 и вторую 10 группу элементов И-ИЛИ, элемент HE 11, установочный вход 12 устройства.

Блок 2 формирования адреса выполнен по известной схеме и содержит счетчики адреса записи и чтения, выходы которых соединены с входами элементов И-ИЛИ по числу разрядов адреса, а другие входы элементов И-ИЛИ подключены прямо и через элемент НЕ 11 к управляющему входу 6.

Входы счетчиков адреса записи и адреса чтения подключены соответственно к управляющим входам 4 и 5 устройства.

Блок 3 коммутации содержит дешифратор 13 и матрицу 14 элементов И. Матрица 14 содержит n)(n элементов И 15 и имеет информационные входы 16, управляющие входы 17 и информационные выходы 18.

Значение и равняется разрядности ячейки блока 1 памяти. Одни входы и элементов

И 15 объединены и подключены к соответствующему входу 16. Выходы и элементов

И 15,соединенных с разными входами 16 и разными входами 17 подключены к одному и тому же выходу 18. Каждый из входов 17 также подключен к и элементам И 15. Причем к входу 17 с номером К подключаются другие входы элементов И 15, стоящих на пересечении выходов 18 с номером строки и входа 16 с номером столбца, при этом номера i, j и К связывает зависимость и — — (i+j), если i+j(n — 1

К=

2п — 1 — (i+j), если i+j)n — 1.

Модуль счета счетчиков 7 и 8 равен количеству слов по числу информационных каналов, размещаемых в одной ячейке блока 1 памяти. Входы 17 матрицы 14 подключены к выходам дешифратора 13 в порядке возрастания номеров, причем подключается к дешифратору каждый р-й вход 17, начиная с нулевого. Входы дешифратора.! 3 подключены к выходам элементов И-ИЛИ первой группы 9 и к третьему управляющему входу 6 задания режима соответственно. Информационные входы 16 матрицы 14 подключены к выходам элементов И-ИЛИ второй группы 10.

Устройство работает следующим образом.

Перед началом работы сигналом по входу 12 устанавливается в исходное (нулевое) состояние первый счетчик 7, второй счетчик 8, а также счетчики адреса записи и чтения блока 2 формирования адреса.

При записи информации на информационные входы устройства подается входное

10 слово, которое содержит данные от нескольких п/р измерительных каналов, причем все измерения представляются словами одинаковой разрядности р. Одновременно на вход 6 режима поступает сигнал, разрешающий выполнение операции записи. С помощью этого сигнала с выходов блока 2 формирования адреса на адресные входы накопителя блока 1 памяти подается адрес записи, после чего в выбранную ячейку памяти записывается входное слово, которое проходит через открытые для него элементы

И-ИЛИ второй группы 10 и блок 3 коммутации без преобразования, так как с выходов первого счетчика 7 через открытые для него элементы И-ИЛИ первой группы 9 на входы дешифратора 13 подается нулевой код в сопровождении сигнала на входе 6 задания режима. После этого сигналом модификации адреса, поступающим на вход 4, модифицируется адрес записи, формируемый блоком 2 формирования адреса, и содержимое первого счетчика 7. При записи следующего входного слова код счетчика 7 создает разрешающий сигнал на следующем (первом) выходе дешифратора 13 блока 3 коммутации,, который поступает на р-й вход 17 управления, разрешающий i прохождение информации с входных информационных шин устройства на выходы 18 матрицы 14 со сдвигом на р разрядов, т. е. данные первого канала занимают место данных последнего канала, а данные остальных каналов сдвигаются, занимая место данных предыдущего канала.

40 Если одно из разрядных сечений блока 1 памяти отказывает, то сечение проходит через данные нескольких каналов, упакованных в одно слово, а не через данные одного канала. Тем самым потери информации распределяются между несколькими

4 каналами.

При чтении информации из устройства производится восстановление исходного формата данных. Для осуществления этого используется блок 3 коммутации. При выполнении операции чтения считанная из блока 1 памяти по адресу, формируемому блоком 2 формирования адреса, информация поступает через открытые для нее элементы И-ИЛИ второй группы 10 на информационные входы 16 блока 3 коммутации. На входы дешифу ратора 13 при этом поступает через элементы И-ИЛИ первой группы 9 код с выхода второго счетчика 8 в сопровождении сигнала на управляющем входе 6 задания режима.

1163358

Эти сигналы воздействуют на дешифратор 13 таким образом, чтобы на его выходе возбуждался сигнал на той шине, которая обеспечивала бы сдвиг информации в матрице 14, приводящий данные, считанные из блока 1 памяти, в соответствие тем, какими они поступают на информационные входы

ЬадЫ ИНГРОРМаЦУИ

Фиг.2

Фиг. f Составитель В. Лупиков

Техред И. Верес Корректор А. Зимокосов

Тираж 7IO Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 l 3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Редактор В. Петраш

Заказ 4107/50

17

f7

17 устройства. С выходов блока 3 коммутации восстановленные данные поступают на информационные выходы устройства. Содержимое счетчика 8 вместе с текущим адресом чтения модифицируется после каждого цикла чтения сигналом модификации адреса чтения, поступающим на вход 5 устройства.