Операционное устройство микропроцессора

Иллюстрации

Показать всеРеферат

ОПЕРАЦИОННОЕ УСТРОЙСТВОМИКРОПРОЦЕССОРА , содержащее регистр состояний, блок регистров общего назначения, блок обмена информацией , регистр результата, сумматор, коммутатор, блок синхронизации, первый буферный регистр, регистр микрокоманд, вход которого являет .ся управляющим входом устройства, а выход соединен с входом дешифратора микрокоманд, входы-выходы регистра результата, блока регистров общего назначения, блока обмена-информацией соединены через внутреннюю магистраль с первым информационным входом и выходом коммутатора и сумматора соответственно, выход которого соединен с информационным входогрегистра состояний, второй информационный выход регистра результата соединен с вторым информационным входом коммутатора, выход регистра состояний соединен с входом первого буферного регистра, выход которого является выходом состояний устройства, о т л и ч а ю .щ е е с я тем, что, с целью повышения быстродействия, оно содержит регистр управляющего кода, второй буферный регистр, первый информационный йход которого соединен с выходом коммутатора, а синхронизирующий вход - с выходом блока синхронизации , информационный вход регистс ра управляющего кода соединен с вы (Л ходом дешифратора микрокоманд, выход второго буферного регистра соединен с вторым информационным входом сум . матора, выход блока синхронизации соединен с управляющим входом регистра упр-авляющего кода, управляюище входы регистра состояний, сумматора, 05 второго буферного регистра, коммута4iik тора, регистра результата, блока ре гистров общего назначения, блока синхI ронизации и блока обмена информаи(ией соединены с выходом регистра управсо ляющего кода.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„1164719

4(sl) G 06 F 15 00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

= ":-г

ПО ДЕЛАМ ИЗОБРЕТЕНИИ И OTHPblTMA

3С г: " - - .; -" .

ОПИСАНИЕ ИЗОБРЕТЕНИЯ 1

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 2817782/18-24 (22) 20.06.79 (46 ) 30 .06 .85 . Бюл . Р 24 (72) В.А.Бобков, С.Н.Тихомиров, Д.Н.Черняковский и В.А.Шиллер (53) 68!.323(088.8) (56) !. Авторское свидетельство СССР

В 647025, кл . G 06 F 15/16, 1979 .

2. Авторское свидетельство СССР

Р 644199, кл. G 06 F 15/16) 1978 (прототип). (54)(57) ОПЕРАЦИОННОЕ УСТРОЙСТВО .

МИКРОПРОЦЕССОРА, содержащее регистр состояний, блок регистров общего назначения, блок обмена информацией, регистр результата, сумматор, коммутатор, блок синхронизации, первый буферный регистр, регистр микрокоманд, вход которого является управляющим входом устройства, . .а выход соединен с входом дешифратора микрокоманц, входы †выхо регистра результата, блока регистров общего назначения, блока обмена информацией соединены через внутреннюю магистраль с первым информационным входом и выходом коммутатора и сумматора соответственно, выход которого соединен с информационным входог регистра состояний, второй информационный выход регистра результата соединен с вторым информационным входом коммутатора, выход регистра состояний соединен с входом первого буферного регистра, выход которого является выходом состояний устройства, о т л и ч а— ю.щ е е с я тем, что, с целью повышения быстродействия, оно содержит регистр управляющего кода, второй буферный регистр, первый информационный вход которого соединен с выходом коммутатора, а синхронизирующий вход — с выходом блока синхронизации, информационный вход регистра управляющего кода соединен с вы-ходом дешифратора микрокоманд, выход второго буферного регистра соединен с вторым информационным входом сум, матора, выход блока синхронизации соединен с управляющим входом регистра упр.авляющего кода, управляющие входы регистра состояний, сумматора, второго буферного регистра, коммута— тора, регистра результата, блока регистров общего назначения, блока синх. ронизации и блока обмена информацией . соединены с выходом регистра управляющего кода.!

164719

Изобретение относится к вычислительной технике, в частности к микропроцессорным вычислительным сНстемам.

Известна микропроцессорная вычисли5 тельная система, содержащая блок .+ арифметических операций, регистр результата, регистр состояния, регистр микрокоманд, дешифратор, микрокоманд, блоки обмена информацией, блоки регистров общего назначения, блок формирования внутреннего рабочего цикла, блок автономного управления асинхронным обменом, блок

15 расширения разрядности с соответствуищи я связяни (I) .

Недостатком этого устройства явля— ются падение быстродействия при расширении разрядности из-за необ20 ходимости формирования сигнала разрешения выдачи сформированных в блоке арифметических операций сигналов переноса и при выборе внутренних регистров для считывания и записи ин25 . формации, возникающее вследствие того, что времена выборки для различных регистров не одинаковые, а время на выборку, задаваемое блоком формирования внутреннего рабочего цикла, фиксировано. Кроме того, в этом устройстве неэффективно используются микрокоманды для задания режима его работы и отсутствует возможность обработки половины слова.

Наиболее близким к изобретению 35 по технической сущности является устройство, содержащее регистр состоя-, ний, блок регистров общего назначения, блок обмена информации, соединенные между собой двусторонними ин- 40 формационными связями и подключен— ные информационными выходами к информационному входу регистра результата, информационные входы регистров состояния и результата и блоков 45 обмена информацией и регистров обще— го назначения соединены с выходом сдвигателя, вход которого подключен к первому выходу блока арифметических и логических операций, второй 50 выход которого соединен с входом регистра состояний, выход которого через буферный регистр подключен к первому выходу устройства, управляющий вход которого через регистр микроко- 55 манд соединен с первым входом дешифратора микроопераций, выход которого подключен к управляющим входам регист ра состояний, сдвигателя, блока арифметических и логических операций, блока формирования рабочего цикла, регистра результата, блока регистров общего назначения, блока обмена информацией, блока автономного управления асинхронным обменом, блока расширения разрядности, буферного регистра, первый, второй и третий входы блока формирования рабо .его цикла подключены соответственно к второму, третьему и четвертому входам дешифратора микроопераций, четвертый выход соединен с входом синхронизации регистра микрокоманд, пятый и шестой выходы подключены соответственно к первому и второму входам блока автономного управления асинхронным обменом, седьмой выход соединен с вторым выходом устройства, а первый вход соединен с первым входом устройства, первый и второй выходы блока автономного управления асинхронным обменом соединены соответственно с первым и вторым входами блока обмена информацией, третьи и четвертые входы — к третьему и четвертому выходам устройства, четвертый вход .и пятый выход которого соединены соответственно с третьим входом и выходом блока обмена информацией, третий выход блока арифметических и логических операций соединен с первым входом блока расширения разрядности,:второй и третий входы которого соединены соответственно с пятым и шестым входами устройства а первый и второй выхо1

Ф ды подключены соответственно к шестому и седьмому выходам устройства, а также регистр режима и коммутатор, выход которого подключен к первому входу блока арифметических и логических операций, вход коммутатора соединен с выходом регистра результата, информационные входы коммутатора, регистр режима и блока формирования рабочего цикла соединены с информационными выходами блоков обмена информацией, регистров общего назначения, регистра состояния, сдвигателя, управляющие входы коммутатора и регистра режима подключены к выходу дешифратора микроопераций, пятый вход дешифратора микроопераций, четвертый вход блока расширения разрядности и второй вход блока формирования рабочего цикла подключены к выходу регистра режи7!9 4 мацией соединены с .выходом регистра управляющего кода.

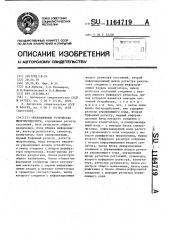

На чертеже представлена блок-схема предлагаемого устройства.

Схема содержит буферный регистр !, регистр .2 состояний, сумматор 3, второй буферный регистр 4, коммутатор 5, регистр 6 результата, блок 7 регистров общего назначения, .блок 8 обмена информацией, регистр 9 микрокоманд, дешифратор 10 микрокоманд, регистр 11 управляющего кода, блок

12 синхронизации, внутреннюю магистраль 13, выход 14 состояний, информационный вход-выход 15. В операциях над одним двоичным числом — операндом (инверсия, дополнение, сдвиги и т.п. i этот операнд поступает на первые информационные входы коммутатора 5 через внутреннюю магистраль

13 устройства из регистра 6 результата, либо из регистра блока 7 регистров.общего назначения, либо иэ блока

8 обмена информацией. В последнем случае операнд поступает в блок 8 обмена информацией через вход-выход 15.

В опер аци ях н ад двумя опер андаж (сложение, вычитание, логические операции и т.п.).первый операнд также поступает на первые информационные входы коммутатора 5, а в качестве второго операнда используется содержимое регистра 6 результата, которое поступает на вторые информационные входы коммутатора 5, где происходит первичное преобразование операндов и на выходах коммутатора 5 поразрядно формируются значения функций соответствующих микроопераций. Так, например, при выполнении микрокоманды сложения.операндов А и В на выходах P и 0 i-го разряда коммутатора формируются логическая сумма и произведение z.-х разрядов операндов:

Р=А+В; G--А В .

Информационные выходы коммутато" ра 5 поразрядно соединены с соответствующими информационными входами регистра 4, в котором преобразованные операнды сохраняются во время фазы исполнения микрокоманды, позволяя освободить внутреннюю магистрапь 13 от операнда и подготовить ее в это время к записи результата микрооперации.

Информационные выходы регистра 4 поразрядно подключены к информа3 I! 64 ма, третий .выход блока. ра.сширения разрядности соединен с вторым входом блока арифметических и логических операций, пятый вход и четвертый выход подключены соответственно к седьмому входу и восьмому выходу устройства, управляющий выход блока арифметических и логических операций соединен с соответствующим управляющим входом блока расширения О разрядностч (2) .

Недостатком устройства является малое быстродействие.

Цель изобретения — повышение бы!

5 стродействия.

Поставленная цель достигается тем, что устройство, содержащее регистр состояний, блок регистров общего назначения, блок обмена информацией, регистр результата, сумматор, 20 коммутатор, блок синхронизации, первый буферный регистр, регистр микрокоманд, вход которого является управляющим входом устройства а выход

25 соединен с входом дешифратора микрокоманд, входы-выходы регистра результата, блока регистров общего назначения, блока обмена информацией соединены ерез внутреннюю магистраль с первым информационным входом и выходом коммутатора и сумматора соот. ветственно, выход которого соединен с информационным входом регистра состояний, -второй информационный выход регистра результата соединен. с 35 вторым информационным входом коммутатора, выход регистра состояний соединен с входом первого буферного регистра, выход которого является выходом состояний устройства, содержит 40 регистр управляющего кода, второй буферный регистр, первый информационный вход которого соединен с выходом коммутатора, а синхронизирующий вход — с выходом блока синхрониза. — 45 ции, информационный вход регистра управляющего кода соединен с выходом дешифратора микрокоманд, выход второго буферного регистра соединен с вторым информационным входом сумма- 50 тора, выход блока синхронизации соединен с управляющим входом регистра управляющего кода, управляющие вхо- . ды регистра состояний, сумматора, второго буферного регистра, коммута-. 55 тора, регистра результата, блока регистров общего назначения, блока синхронизации и блока обмена инфор- . ционным входам сумматора 3, в котором завершается с учетом переносов иэ младших разрядов обработка операндов и форьыруется результат ьаюкрооперации, выдаваемый на первые информационные выходы сумматора 3, поразрядно подключенные к внутренней магистрали 13. В фазе записи результат микрооперации через двунаправленные выводы помещается в регистр 6 результата или в один из регистров блока 7 регистров общего назначения соответственно, либо через двунаправленные выводы выдается в блок В обмена информа- цией и далее через вход-выход 15 устройства в двунаправленную информационную шину данных микропроцессорной вычислительной системы.

По результату. выполнения микрооперации в сумматоре 3 формируется двоичный код признаков состоя. ния, в тоМ числе признаки равенства результата нулю, переполнения разрядной сетки, знаковый и т.п.

Признаки состояния выдаются из сумматора 3 по его вторым информационным выходам в регистр 2 состояния, а из последнего через блок 12 по вторым выводам устройства поступают íà выход 14.

Иикрокомандш, формируемые устройством микропрограммного управ1164719

Введение регистра управляющего

20 кода и регистра коммутатора позволяет сделать длительность цикла исполнения микрокоманды равной т -т +т +т „+т„; ь сЧ Иcn аП гЯ фз Дпительность цикла известного устройства выражается следующей зависимостью тц=т т„+т +т„+т„ +т, Отсюда видно, что цикл предлага- еМого устройства короче и, следовательно, оно более быстро-. действующее. б ления (не показан), поступают в регистр 9 микрокоманд и, далее, на входы дешифратора 10 микрокоманд . Дешифрированная микрокоманда (управляЗ ющий код) поступает на информационные входы регистра Il управляющего кода. Управляющий код очередной микрокоманды хранится в регистре 11 в течение фаз считывания, исполнения и записи, что позволяет в это же время принимать и дешифрировать следующую микрокомаиду. Синхронизация приема и выдачи информации в регистре 11 управляющего кода и регистре 4 осуществляется сигналами из блока 12 синхро-;. низации.

1164719

Составитель В.Евстигнеев

Техред М.Пароцай . Корректор Е. Сир охман

Редактор Л.Авраменко

Филиал ППП "Патент", г. Ужгород, ул . Проектная, 4

Закаэ 4188/46 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5