Элемент памяти (его варианты)

Иллюстрации

Показать всеРеферат

1. Элемент памяти,, содержащий триггер, первый и второй входы которого соединены со словарной шиной и шиной питания соответственно, элементы связи на транзисторах, затворы которых соединены с и инверсньм выходами триггера, и разрядные шины, о тличающийс я тем, что, с целью повышения быстродействия и надежности элемента , в него введен пороговый элемент на диоде, анод которого подключен к объединенным истокам транзисторов , катод - к дополнительной шине фиксированного потенциала, а стоки транзисторов соединены с соответ (Л ствукнцими разрядными шинами. а эо

СОЮЗ СОВЕТСКИХ

WWVIL1

РЕСПУБЛИК

4уц С 11 С 11/40

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИ в свтсссвссст сввсвсввьствт (21) 3551418/24-24 ° 3550730/24-24 3

3556579/24-24; 3554285/24-24 (22) 11 ° 02 Е3 (46) 30.06.85. Вюл. В 24 (72) В.А. Братов, Л.Н. Кравченко,:

В.И. Старосельский и В.И. Суэтинов (71) Московский институт электронной техники (53) 681.327.6 (088.8) (56) К. Ohvada, Мв Ino, Т. Mizutani

and K. Asai. "ОаАв 256-bit Static

КАИ" - ELECTR. LET., v. 18, 7, 1982.

О. Rert, J.-P. Noriu, G. NuziIIat, and G. Arnodo. High-Speed GaAs

Static ВАМ - IREE trans., ч. МТГ-ЗО,,У 7, 1982.

„„SU„„3 164787 А (54) ЭЛЕМЕНТ ПАМЯТИ (ЕГО ВАРИАНТЫ). (57) 1. Элемент памяти, содержащий триггер, первый и второй входы которого соединены со словарной шиной и шиной питания соответственно, элементы связи на транзисторах, затворы которых соединены с прямым и инверсным выходами триггера, и разрядные шины, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия и надежности элемента, в него введен пороговый элемент на диоде, анод которого подключен к объединенным истокам транзисторов, катод — к дополнительной шине фиксированного потенциала, а стоки транзисторов соединены с соответ ствующими разрядными шинами.

11

2. Элемент памяти, содержащий триггер, первый и второй входы которого соединены со словарной шиной и шиной питания соответственно, элементы связи на транзисторах, затворы которых соединены с прямым и инверсным выходами триггера, а стоки подключены к шине питания, и разрядные шины, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия и надежности элемента, в него введены пороговые элементы на диодах, аноды которых сое« динены с истоками соответствующих транзисторов, катоды — с соответствующими разрядными шинами.

3. Элемент памяти, содержащий триггер, первый и второй входы которого соединены со словарной шиной и шиной питания соответственно, элементы связи на транзисторах, затворы которых соединены с прямым и инверсным выходами триггера, и разрядные шины, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия и надежности элемента, в него введены пороговые эле64787 менты на диодах, катоды первого и второго диодов подключены к выходам триггера, аноды гретьего и четвертого диодов подключены к соответствующим разрядным шинам, объединенные аноды с катодами первого и третьего, второго и четвертого диодов подключены к стокам транзисторов, истоки которых подключены к словарной шине.

4. Элемент памяти, содержащий триггер, первый и второй входы которого соединены со словарной шиной и шиной питания соответственно, элементы связи на транзисторах, затворы которых соединены с прямым и инверсным выходами триггера, и разрядные шины, отличающийся тем, что, с целью повышения быстродействия и надежности элемента, в нем дополнительные затворы транзисторов,, расположенные между основными затворами и стоками, подключены к дополнительной шине, истоки транзисторов подключены к словарной шине, а стоки — к соответствующим разрядным шинам.

Изобретение относится к микроэлектронике и может быть использовано в интегральных схемах запоминающих устройств.

Цель изобретения — повышение 5 быстродействия и надежности элемента памяти.

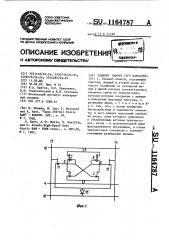

На фиг.1-4 изображены четыре варианта предлагаемого элемента памяти. S0

Элемент памяти по первому варианту содержит триггер на транзисторах 1 и 2, истоки которых подключены к первому входу триггера 3, соединенному со словарной шиной 4, а 15 стоки — к прямому 5 и инверсному 6 выходам триггера соответственно, к которым подключены также затворы транзисторов 2 и 1 соответственно, и объединенные затвор и исток 20 нагрузочных нормально открытых транзисторов 7 и 8 соответственно, подключенных стоками к второму входу триггера 9, соединенному с шиной питания 10, а также первый 11 и второй 12 нормально закрытые транзисторы связи, стоки которых подключены к первой 13 и второй 14 разрядным шинам соответственно, затворы— к выходам 5 и 6 соответственно, а объединенные истоки — к аноду дополнительного диода с барьерным переходом 15, катод которого подключен к дополнительной шине. 16, на которой поддерживается фиксированный (в. данном случае нулевой) потенциал.

В режиме хранения на словарной шине 4 поддерживается потенциал ОВ.

При этом на разрядных шинах 13 и 14 сохраняется потенциал 27 . Лля осуществления выборки необходимо повн« сить потенциал словарной шины 4 до величины V . При этом отпирается один из транзисторов 11, 12, подключенный к выходу триггера с более

1164787 4 величины не менее 2 V .Потенциал другой Разрядной шины не изменяется, Таким образом, потенциалы разрядных шин оказываются кратными величине

V>, что обеспечивает надежное считывание.

Для осуществления записи необходимо повысить потенциал словарной шины 4 до величины 2 Ч .и понизить и

10 потенциал требуемой разрядной шины до нуля. При этом отпираются соответствующий диод и переход затвор-исток соответствующего транзистора связи и происходит опрокидыва15 ние триггера. Если сигнал выборки отсутствует, то оба транзистора связи 11 и 12 остаются закрытыми и запись не происходит. высоким потенциалом, и потенциал соответствующей разрядной шины становится выше потенциала дополнительной шины 16 на величину Чв. На другой разрядной шине при этом сохраняется потенциал хранения. Таким образом, потенциалы разрядных шин оказываются кратными величине V,÷òo обеспечивает надежное считывание.

Для осуществления записи необходимо повысить потенциал словарной шины 4 до величины V и понизить потенциал требуемой разрядной шины до нуля, не меняя потенциала другой разрядной шины. При этом отпирается переход затвор-сток соответствующего транзистора связи и происходит опрокидывание триггера. Если сигнал выборки отсутствует, то оба транзистора связи ii и 12 остаются 2о закрытыми, а запись не происходит.

Элемент памяти по второму варианту (фиг.2) содержит триггер на транзисторах 1 и 2, истоки которых подключены к первому входу тригге- 25 ра 3, соединенному со словарной шиной 4, а стоки — к прямому 5 и инверсному 6 выходам триггера соответственно, к которым подключены также затворы транзисторов 2 и 1 зо соответственно, и объединенные затвор и исток нагрузочных нормально открытых транзисторов 7 и 8 соответственно, подключенных стоками к второму входу триггера 9, соединен35 ному с шиной питания 10, а также первый 11 и второй 12 нормально открытые транзисторы связи, стоки которых подключены к шине питания 10, затворы — к выходам 5 и 6 соответственно, а истоки - к первой 13 и второй 14 разрядным шинам соответственно посредством дополнительных первого 15 и второго 16 диодов с барьерным переходом, подключенных катодами к разрядным шинам, а анодами — к истокам транзисторов связи.

В режиме хранения на словарной шине 4 поддерживается нулевой потенциал, а на разрядных шинах 13 и

14 — потенциал V . При этом транзисторы связи 11 и 12 заперты.

Для осуществления выборки необходимо повысить потенциал словарной шины 4 до величины 2 V . При этом отпирается один из транзисторов связи и потенциал соответствующей разрядной шины повышается.до

Элемент памяти по третьему варианту {фиг.3) содержит триггер на транзисторах 1 и 2, истоки которых подключены к первому входу триггера 3, соединенному со словарной шиной 4, а стоки — к прямому 5 и инверсному 6 выходам триггера соответственно, к которым подключены также затворы транзисторов 2 и 1 соответственно, и объединенные затвор и исток нагрузочных нормально открытых транзисторов 7 и 8 соответственно, подключенных стоками к второму входу триггера 9, соединенному с шиной питания 10, а также первый

11 и второй 12 нормально закрытые транзисторы связи, истоки которых подключены к словарной шине 4, затворы — к выходам 5 и 6 соответственно, а стоки — к первой 13 и второй 14 разрядным шинам при помощи первого 15 и второго 16 пороговых элементов на диодах с барьерным переходом, у которых катоды первого

15 и второго 16 диодов подключены к выходам триггера, аноды третьего

17 и четвертого 18 диодов — к соответствующим разрядным шинам, а объединенные аноды с катодами первого и третьего, второго и четвертого диодов — к стокам соответствующих транзисторов связи.

В режиме хранения на словарной шине 4 поддерживается потенциал V

Д °

При э-ом на разрядных шинах 13 и

14 сохраняется потенциал 2 V .

Для осуществления выборки необходимо понизить. потенциал словарной шины до нуля. При этом потенциал одной из разрядных шин

1164787

tpuz, 2 снижается до величины Ч в реэульв тате отпирания соответствующего транзистора связи, а потенциал другой разрядной шины не изменяется. Таким образом, потенциалы разрядных шин оказываются кратными величине Ч, что обеспечивает надежное считывание.

Для осуществления записи необходимо понизить потенциал словарной шины 4 до нуля и lIoBbIcHTb IIo тенциал 1 ребуемой разрядной шины до величины ЗЧ . При этом через соответствующий пороговый элемент в

ЗП втекает ток и происходит опрокидывание триггера. Если сигнал выборки отсутствует, то оба пороговых элемента остаются закрытыми и запись не происходит.

Элемент памяти по четвертому варианту (фиг.4) содержит триггер на транзисторах 1 и 2, истоки которых подключены к первому входу триггера 3, соединенному со словарной шиной 4, а стоки - к прямому 5 и инверсному 6 выходам триггера соответственно, к которым подключены также затворы транзисторов 2 и 1 соответственно, и объединенные затвор и исток нагрузочных нормальнЬ открытых транзисторов.7 И 8 соответственно, подключенных стоками к второму входу триггера 9, соединенному с шиной питания 10 а также первый 11 и второй 12 нормально закрытые транзисторы связи, истоки которых подключены к словарной шине 4, стоки - к первой 13 и второй

14 разрядным шинам, основные затворы - к выходам 5 и 6 соответственно, а дополнительные затворы, размещенные между основными затворами и стоками — к дополнительной шине 19.

В режиме хранения на словарной шине 4 поддерживается потенциал Ч, на дополнительной шине 19 - нулевой потенциал, а на обеих разрядных шинах — потенциал 2Ч

Для осуществленйя выборки необ10 ходимо повысить потенциал дополнительной шины 19 до величины 2Ч .При этом отпирается один из транзисторов связи 11 и 12 и потенциал со- ответствующей разрядной шины по-

15 нижается до величины V Потенциал другой разрядной шины не изменяется.

Таким образом, потенциалы разрядных шин оказываются кратными величине Ч, что обеспечивает надежное

20 считывание.

Для осуществления записи необходимо повысить потенциал дополнительной шины 19 до величины У и понизить потенциал требуемой раз>5 рядной,шины до нуля. При этом отпирается переход дополнительный затвор-сток соответствующего транзистора связи и происходит опрокидывание триггера. Если сигнал

30 выборки отсутствует, то запись не происходит.

Проектирование предлагаемых устройств является совершенно новой областью, аналогичные отечественЗ5 ные разработки отсутствуют. В связи с этим выбрать базовый объект не представляет возможным.

Изобретение по сравнению с прототипом позволяет увеличить бы40 стродействие в 1 5-2 раза и коэффициент выхода гЬдных интегральных схем на 40-50%.

11647S7

Составитель В. Фокина

ТехредМ.Надь Корректор В. Бутяга

Редактор М. Дылин

Тараи 584 Подписное

ВИИИПИ Государственного комитета СССР по делам изббретеннй и открытий

113035, Москва, %-35, Раушская наб., д. 4/5

Заказ 4193/49

Филиал ППП "Патент", r. Уигород, ул. Проектная,4