Дельта-декодер с экспандированием

Иллюстрации

Показать всеРеферат

ДЕЛЬТА-ДЕКОДЕР С ЭКСПАНДИРОВАНИЕМ по авт. св. № 594583, отличающийся тем, что, с целью уменьшения шумов квантования в режиме молчания, 1з него введены резистор , повторитель напряжения, дополнительный ключ, выделитель постоянной составляющей, источник опорного напряжения и компаратор, выход интегратора через соедияенные последовательно резистор и повторитель напряжения подключен к выходу устройства , а объединенные выходы ключей соединены с входом выделителя постоянной составляющей, выход которого подключен к первому входу компаратора , второй вход которого соединен с источником опорного напряжения , а выход - с управляющим входом дополнительного ключа, вход и выход которого подключены соответственно к нулевой шине и входу повто (Л рителя напряжения.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

6

1

, В

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCKOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (61) .594583 (21) 3684676/24-24 (22) 04.01.84 (46) 30.06.85. Вюл. ¹ 24 (72) А.А.Зайцев, В.З.Магиденко и П.И.Чередников (71) Харьковский ордена Трудового

Красного Знамени институт радиоэлектроники им. акад. М.К.Янгеля (53) 621.376,56 (088.8) (56) 1. Авторское свидетельство СССР № 594583,.кл. Н 03 К 13/22, 02.07.76

{прототип). (54){57) ДЕЛЬТА-ДЕКОДЕР С ЗКСПАНДИРОВАНИЕМ по авт. св. № 594583, о т— л и ч а ю шийся тем, что, с целью уменьшения шумов квантования в режиме молчания, и него введены ре„„Я0„„1164887 А

4(51) H 03 M 3/02 H 03 К 13/22 зистор, повторитель напряжения, дополнительный ключ, выделитель постоянной составляющей, источник опорного напряжения и компаратор, выход интегратора через соединенные последовательно резистор и повторитель напряжения подключен к выходу устройства, а объединенные выходы ключей соединены с входом выделителя постоянной составляющей, выход которого подключен к первому входу компаратора, второй вход которого соединен с источником опорного напряжения, а выход - с управляющим входом дополнительного ключа, вход и выход которого подключены соответственно к нулевой шине и входу повторителя напряжения.

1164887 г

Изобретение относится к автоматике и вычислительной технике, а именно к цифровой обработке сигналов, и может быть использовано для построения кодеров и декодеров в. каналах связи с использованием дельта-модуляции, По основному авт. св. ¹ 594583 известен дельта-. декодер с экспандированием, содержащий формирователь .цифрового сигнала, первый и второй входы которого соединены с входами устройства, а выходы подключены к первым входам соответствующих элементов И и к соответствующим входам анализатора цифрового сигнала, первый и. второй выходы которого соеди"иены соответственно со счетным и управляющим входами двоичного реверсивного счетчика, выходы разрядов которого подключены к управляющим входам соответствующих ключей, входы которых соединены с соответствующими выходами генератора импульсных последовательностей, объединенные выходы ключей соединены с вторыми . входами элементов И, выходы которых подключены к соответствующим входам генератора тока, выход которого соединен с входом интегратора, подключенного своим выходом к выходу устройства 1 $, Недостатком этого дельта-декодера является повышенный уровень шу.ма в режиме молчания из-за неидеальности устройств преобразования исходного сигнала в цифровую последовательность.

Цепь изобретения — уменьшение шумов квантования в режиме молчания.

Поставленная цель достигается тем, что в дельта-декодер с экспан. дированием введены .резистор, повто- . ритель напряжения, дополнительный, ключ,. выделитель постоянной составляющей, источник опорного напряжения и компаратор, выход интегратора через соединенные последователь но резистор и повторитель напряже.ния подключен к выходу устройства, . а объединенные выходы ключей соеди-, нены с входом выделителя постоянной составляющей, выход которого подключен к первому входу компаратора, второй вход которого соединен с источником .опорного напряжения, а выход — с управляющим входом дополнительного ключа, вход и выход которого подключены соответственно к нуле5

15

25

Ъ вой шине и входу повторителя напряжения. г

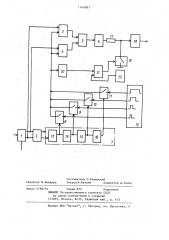

На чертеже показана блок-схема предлагаемого устройства.

Устройство содержит формирователь 1 цифрового сигнала, выходы которого подключены к входам анализатора 2 цифрового сигнала и к первым .входам соответствующих элементов 3

-и 4 И, выходы которых через генератор 5 тока подключены .к входу интегратора 6. Выходы анализатора 2 цифрового сигнала подключены также к счетному и управляющему входам двоичного реверсивного счетчика 7, выходы разрядов которого подключены к управляющим входам соответствующих ключей 8-11, сигнальные входы которых соединены с соответствующими входами генератора 12, импульс ных последовательностей, а выходы ключей 8-11 подключены ко вторым входам элементов 3 и 4 И, при этом двоичный реверсивный счетчик 7 состоит из цепочки триггеров 13 — 16.

Последовательно соединенные резистор 17 и повторитель 18 напряжения включены на выходе интегратора 6, между входом повторителя 18 и нулевой шиной включен дополнительный ключ 19. С выходами ключей 8-11 соединен .вход выделителя 20 постоянной составляющей, а .выход его соединен с первым входом компаратора 21, ко второму входу которого подключен источник 22 опорного напряжения, а выход компаратора 21 соединен с управляющим входом дополнительного ключа 19.

Устройство работает следующим образом.

Анализатор 2 анализирует двоичный сигнал на выходе формирователя l.

Если число подряд следующих единиц нли нулей не превышает четыре, то в двоичном реверсивном счетчике 7 взведен только триггер 13. Выходной сигнал триггера 13 отпирает ключ 8 и на интегратор 6 через генератор 5 тока и соответствующий элемент 3 или 4 И каждый интервал дискретизации проходят импульсы иэ последовательности, имеющей минимальную длительность. Если число подряд следующих единиц или нулей превышает четыре, то анализатор 2 выдает импульс55 ный сигнал, при котором триггер !3 приходит в исходное состояние, а триггер 14 вэводится. В результате ключ 8 залирается, а отпирается

3 I 164 ключ 9, пропуская на свой выход (и далее на интегратор 6 1 импульс с длительно стью в два раз а большей, чем длительность импульсов триггера 13.

Чем больше число, записанное в двоичный реверсивный счетчик, тем больше длительность импульса, приходящего на интегратор 6. Если крутизна исходного сигнала понижается, то анализатор 2 переводит двоичный реверсивный счетчик 7 в режим вычитания по управляющему входу и число в нем уменьшается с приходом сигнала на счетный вход.

В режиме молчания когда В точке соединения сигнальных выходов ключей 8-11 проходят импульсы минимальной длительности, на выходе выделителя 20 постоянной составляющей (в простейшем случае интегрирующая

РС-цепь ) присутствует напряжение минимальной величины. С появлением импульсов большей длительности на входе вьделителя 20 (что соответствует появлению информационной последовательности преобразования исходного сигнала ), на выходе последнего напряжение возрастает. Поэтому в режиме молчания напряжение на выходе вьделителя 20 принимается за порого 30 вое, при котором сраб атыв ает компара887 4 тор 21 и, следовательно, ключ 19 перекрывает выход декодера. При увеличении напряжения на выходе вьделителя 20 ключ 19 закрывается и не вносит влияния в работу декодера. Ус-, тановка порога срабатывания компаратора осуществляется источником 22 опорного напряжения. Повторитель 18 напряжения служит для преобразова ния выходного сопротивления декодера, которое увеличилось вследствие включения резистора 17.

Таким образом, введенные резистор, повторитель напряжения, дополнительный ключ, выделитель постоянной составляющей, источник опорного напряжения и компаратор фактически выполняют функции порогового шумо. подавляющего устройства, управляемого напряжением экспандирования, которое вьделяется с помощью вьделителя 20 постоянной составляющей иэ импульсной последовательности, велнчнна которого является объективным параметром состояния молчащего канала. Вследствие этого происходит увеличение отношения сигнал/шум на выходе декодера за счет уменьшения шума .квантования в режиме молчания.

I 164887

Составитель О.Ревинский

Редактор М.Бандура Техред М.Кузьма Корректор А. Тяско

Заказ 4198/54 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4