Устройство распределения сигналов управления комплектами для узлов коммутации с программным управлением

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО РАСПРЕДЕЛЕНИЯ СИГНАЛОВ УПРАВЛЕНИЯ КОМПЛЕКТАМИ ДЛЯ УЗЛОВ КОММУТАЦИИ С ПРОГРАММНЫМ УПРАВЛЕНИЕМ , содержащее последовательно соединенные блок сопряжения, регистр информации и блок управляющей памяти, выходы которого соединены с соответствующими первыми входами первого блока элементов И, выходы которого подключены к первому входу блока сравнения, выход которого соединен с входом блока сопряжения, второй выход которого соединен с входом регистра адреса, выход которого подключен к входу дешифратора, а второй вход блока сравнения соединен с первым выходом блока сопряжения, причем адресные входы блока управляющей памяти соединены с входами первого блока задержки, выходы которого подключены к вторым входам первого блока элементов И, отличающееся тем, что, с целью повышения точности распределения, в него введены второй, третий и четвертый блоки элементов И, первый и второй блоки триггеров, второй и третий блоки элементов задержки, входы которых подключены к выходам второго блока триггеров и к первым входам второго блока элементов И, вторые входы которого соединены с выходами блока управляющей памяти, адресные входы которого подключены к выходам второго блока элементов задержки, входы которого соединены с выходами дешифратора, установочными входами сл первого блока триггеров и первьо и входами третьего блока элементов И, вторые входы которого объединены и соединены с вторым выходом блока сравнения, а выходы третьего блока элементов И соединены с соответствующими входами сброса первого блока Од триггеров и установочными входами 4ik второго блока триггеров, входы сброСО са которого подключены к соответствуюпщм выходам четвертого блока элементов И, первые входы которого соединены с соответствующими выходами, первого блока триггеров, а вторые входы четвертого блока .элементов И соединены с соответствующими выходами третьего блока элементов эгщержки.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (5!)4Н 04 М 3/18

ОПИСАНИЕ ИЗОБРЕТЕНИ

H АВТОРСНОЬЮ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПР ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3675875/24-09 (22) 12.12.83 (46) 30.06.85. Бюл. № 24 (72) А.Я. Шалаев и Г.Г. Донда (71) Ленинградский электротехнический институт связи им. проф.

М.А. Бонч-Бруевича (53) 621.395.348(088.8) (56) Peripheral Divices for the

Unimal 4080 — РАВ Н.D. Siebel

Elektrical Communication, 1980, v, 53, Р 1, р. 57-62.

Патент ФРГ ¹ 2813291, кл. Н 04 Q 3/54, 1976. (54)(57) УСТРОЙСТВО РАСПРЕДЕЛЕНИЯ

СИГНАЛОВ УПРАВЛЕНИЯ КОМПЛЕКТАМИ ДЛЯ

УЗЛОВ КОММУТАЦИИ С ПРОГРАММНЫМ УПРАВЛЕНИЕМ, содержащее последовательно соединенные блок сопряжения, регистр информации и блок управляющей памяти, выходы которого соединены с соответствующими первыми входами первого блока элементов И, выходы которого подключены к первому входу блока сравнения, выход которого соединен с входом блока сопряжения, второй выход которого соединен с входом регистра адреса, выход которого подключен к входу дешифратора, а второй вход блока сравнения соединен с первым выходом блока сопряжения, причем адресные входы блока управляющей памяти соединены с входами первого блока задержки, выходы кото„„Я0„„1164904 A рого подключены к вторым входам первого блока элементов И, о т л и ч аю щ е е с я тем, что, с целью повышения точности распределения, в него введены второй, третий и четвертый блоки элементов И, первый и второй блоки триггеров, второй и третий блоки элементов задержки, входы которых подключены к выходам второго блока триггеров и к первым входам второго блока элементов И, вторые входы которого соединены с выходами блока управляющей памяти, адресные входы которого подключены к выходам второго блока элементов задержки, входы которого соединены с выходами дешифратора, установочными входами первого блока триггеров и первьвчи входами третьего блока элементов И, С вторые входы которого объединены и соединены с вторым выходом блока сравнения, а выходы третьего блока элементов И соединены с соответству щими входами сброса первого блока 1esl триггеров и установочными входами Cb второго блока триггеров, входы сбро- аф са которого подключены к соответст- {, ф вующим выходам четвертого блока Ю элементов И, первые входы которого ф соединены с соответствующими выходами. первого блока триггеров, а вторые входы четвертого блока элементов И соединены с соответствующими выходами третьего блока элементов задержки.

1164904

Изобретение относится к электросвязи и может быть использовано в электронных узлах коммутации с программным управлением.

Целью изобретения является пбвыше- 5

4 ние точности распределения °

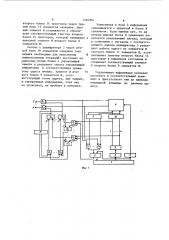

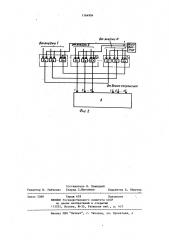

На фиг. 1 приведена структурная схема устройства распределения сигналов управления комплектами для узлов коммутации с программным управлением;10 на фиг.2 — функциональная схема первого блока элементов И.

Устройство содержит блок 1 сопряжения, регистр 2 адреса, дешифратор

3, блок 4 управляющей памяти, регистр15

5 информации, первый блок 6 элементов задержки, первый блок 7 элементов И, блок 8 сравнения, второй блок 9 элементов И, второй блок 10 элементов задержки, третий блок 11 элементов И,20 первый блок 12 триггеров, четвертый блок 13 элементов И, второй блок 14 триггеров, третий блок 15 элементов задержки.

Первый блок 7 элементов И (фиг ° 2) 25 содержит п групп по элементов И, в каждой группе, где п — число .ячеек памяти блока 4 управляющей памяти, k — - количество разрядов в каждой ячейке. 30

Устройство работает следующим образом.

По адресным и информационным шинам из устройства управления (не показано) в блок 1 сопряжения поступает 35 команда, содержащая информационную и адресную части. Адресная часть поступает в регистр 2 адреса. Она определяет адрес ячейки блока 4 управляющей памяти, управляющей работой 40 комплекта, которому адресована данная информация, содержащаяся в информационной части команды.

После дешифрации адреса на одном из выходов дешифратора 3 появляется сигнал, который через второй блок 10 элементов задержки поступает на ад ресный вход блока 4 управляющей памяти и управляет записью в соответствующую ячейку ийформации, содержащейся в регистре 5 информации.

Далее возможны два случая работы устройства.

Первый случай характеризуется тем,что запись информации по данному адресу происходит первый раз по отношению к исходному состоянию всего устройства. При этом в исходном состоянии соответствующий триггер второго блока 14 триггеров (например 14„) находится в состоянии О, т.е. с его выхода на соответствующий второй вход элемента И второго блока

9 элементов И поступает запрещающий сигнал, который блокирует информацию из соответствующей ячейки блока 4 управляющей памяти в управляемый комплект. Записанная в этой ячейке информация поступает через одну из п схем И первого блока 7 элементов И, открытую через первый блок 6 элементов задержки в блок 8 сравнения, где сравнивается с информацией, поступающей на второй вход блока 8 сравнения иэ блока 1 сопряжения.

При обнаружении ошибки блок сравнения 8 вырабатывает на выходе, связанном с блоком 1 сопряжения, соответствующий сигнал, которыи передается в устройство управления. Если блок 8 сравнения не обнаруживает ошибки, то на его втором выходе появляется разрешающий сигнал, который в сочетании с соответствующим сигналом с выхода дешифратора 3 (в рассматриваемом примере с выхода 1), вызывает переключение в единичное состояние триггера второго блока 14 триггеров через соответствующий элемент третьего блока 11 элементов И.

Выходной сигнал триггера открывает соответствующий поступающему адресу один из элементов И второго блока 9 элементов И. Управляющая информация из соответствующей ячейки блока 4 оказывается подключенной к входу комплекта. Устройство управления, не получив сигнала об ошибке в течение сеанса обмена, переходит к выдаче следующей команды.

Второй случай характеризуется тем, что информация записывается по адресу, по которому уже осуществляется выдача управляющей информации.

Устройство в этом случае работает следующим образом.

После дешифрации адреса на первом выходе дешифратора 3 появляется единичный сигнал. Этот сигнал поступает на установочный вход соответствующего триггера первого блока 12 триггеров, единичный выходной сигнал которого стробирует соответствующий элемент И четвертого блока 13 элементов И, на втором входе которого уже имеется единичный сигнал с выхода

1164904

<5 Управляющая информация начинает поступать в соответствующий комплект и присутствует там до прихода очередной команды по данному адресу. второго блока 14 триггеров через третий блок 15 элементов задержки. Данный элемент И открывается и сбрасывайт соответствующий триггер второго блока 14 триггеров, который закрывает S выходной элемент И второго блока 9 элементов И.

Сигнал с дешифратора 3 через второй блок 10 элементов задержки (задержка необходима для выполнения .О вышеуказанных операций) поступает на адресные входы блока 4 управляющей памяти и разрешает запись управляющей информации в соответствующую принятому адресу ячейку. Элемент И второго блока 9 элементов И, соответствующий этому адресу, уже закрыт, и управляющая информация, пока она не проверена, не пройдет в комплект.

Записанная в блок 4 информация сравнивается с принятой в блоке 8 сравнения. Если ошибки нет, то на втором выходе блока 8 сравнения появляется разрешающий сигнал, который в сочетании с сигналом с соответствующего выхода дешифратора 3 разрешает работу одного из элементов И третьего блока 11 элементов И, устанавливает триггер второго блока 14 триггеров в единичное состояние и открывает соответствующий элемент

И второго блока 9 элементов И.

1164904

Pm медки N

Тираж 659 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5060

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель В. Паницкий

Редактор И. Рыбченко Техред С.Мигунова Корректор А. Обручар