Устройство для определения момента изменения свойств случайного процесса

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОМЕНТА ИЗМЕНЕНИЯ СВОЙСТВ СЛУЧАЙНОГО ПРОЦЕССА, содержащее первый элемент задержки, квадратор, блок вычитания, первый сумматор и блок сравнения, отличающееся тем, что, с целью расширения класса решаемых задач и повышения точности и быстродействия , в него введены блок буферной памяти , формирователь адреса, два элемента задержки, второй сумматор, два блока постоянной памяти, четыре накапливающих сумматора, четыре блока умножения, два регистра константы, блок деления и генератор тактовых импульсов, вход которого объединен с входом первого элемента задержки , первым входом первого сумматора и является входом устройства, выход генератора тактовых импульсов соединен с тактовыми входами первого и второго накапливающих сумматоров, тактовым входом блока буферной памяти и входом формирователя адреса, выход которого соединен с адресными входами блоков постоянной памяти и блока буферной памяти, информационный вход которого подключен к выходу первого элемента задержки, выход блока буферной памяти подключен к I первым входам первого и второго блоков умножения, вторые входы которых подклю (Л чены соответственно к выходам первого и второго блоков постоянной памяти, выходы первого и второго блоков умножения соединены соответственно с информационными входами первого и второго накапливающих сумматоров, выход первого из которых соединен с вторым входом первого сумматора, выход которого соединен с первым входом а третьего блока умножения, второй вход коOi торого объединен с входом квадратора и подключен к выходу второго накапливающего сумматора, выход третьего блока умножения через последовательно соединенные тре«х тий накапливающий сумматор и второй элемент задержки подключен к первому информационному входу второго сумматора , второй информационный вход которого подключен к выходу четвертого блока умножения , управляющий вход второго сумматора объединен с управляющими входами четвертого блока умножения, блока деления и подключен к управляющему выходу блока вычитания, выход второго сумматора соединен с первым входом блока сравнения, второй вход которого подключен к выходу первого регистра константы, выход блока

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

4 511 G 06 G 752

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3680772/24-24 (22) 29.11.83 (46) 07.07.85. Бюл. № 25 (72) С. Э. Воробейчиков, Ю. М. Гармаш и В. В. Конев (71) Сибирский физико-технический институт им. В. Д. Кузнецова при Томском государственном университете им. В. В. Куйбышева (53) 621.3 (088.8) (56) Линейка А. Об определении моментов изменения свойств авторегрессионной последовательности. Сб. Статистические проблемы управления», вып. 39, Вильнюс, !979, с. 9 — 24.

Авторское свидетельство СССР № 324633, кл. G 06 G 7/52, 1970.

Вальд А. Последовательный анализ. М., Физматгиз, 1960.

Андерсон Т. Статистический анализ временных рядов. М., «Мир», 1976, с. 446.

Справочник по теории вероятностей и математической статистике. Под ред, В. С. Королюка. Киев, Наукова думка. 1978, с. 248.

Воробейчиков С. Э. Конев В. В. К обнаружению моментов разладки случайных процессов. — В кн., «Математическая статистика и ее приложения». Вып. 8, Томск, ТГУ, 1982, с. 20 — 34. (54) (57) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОМЕНТА ИЗМЕНЕНИЯ

СВОЙСТВ СЛУЧАИНОГО ПРОЦЕССА, содержащее первый элемент задержки, квадратор, блок вычитания, первый сумматор и блок сравнения, отличающееся тем, что, с целью расширения класса решаемых задач и повышения точности и быстродействия, в него введены блок буферной памяти, формирователь адреса, два элемента задержки, второй сумматор, два блока постоянной памяти, четыре накапливающих

„„SU„„1166149 A сумматора, четыре блока умножения, два регистра константы, блок деления и генератор тактовых импульсов, вход которого объединен с входом первого элемента задержки, первым входом первого сумматора и является входом устройства, выход генератора тактовых импульсов соединен с тактовыми входами первого и второго накапливающих сумматоров, тактовым входом блока буферной памяти и входом формирователя адреса, выход которого соединен с адресными входами блоков постоянной памяти и блока буферной памяти, информационный вход которого подключен к выходу первого элемента задержки, выход блока буферной памяти подключен к первым входам первого и второго блоков умножения, вторые входы которых подключены соответственно к выходам первого и второго блоков постоянной памяти, выходы первого и второго блоков умножения соединены соответственно с-информационными входами первого и второго накапливающих сумматоров, выход первого из которых соединен с вторым входом первого сумматора, выход которого соединен с первым входом третьего блока умножения, второй вход которого объединен с входом квадратора и под— ключен к выходу второго накапливающего сумматора, выход третьего блока умножения через последовательно соединенные третий накапливающий сумматор и второй элемент задержки подключен к первому информационному входу второго сумматора, второй информационный вход которого подключен к выходу четвертого блока умножения, управляющий вход второго сумматора объединен с управляющими входами четвертого блока умножения, блока деления и подключен к управляющему выходу блока вычитания, выход второго сумматора соединен с первым входом блока сравнения, второй вход которого подключен к выходу первого регистра константы, выход блока

1166149 сравнения является выходом устройства, первый информационный вход четвертого блока умножения подключен к выходу третьего блока умножения, второй информационный вход четвертого блока умножения подключен к выходу блока деления, первый информационный вход которого подключен к выходу третьего элемента задержки, второй информационный вход блока деления

Изобретение относится к технической кибернетике и может быть использовано для определения момента скачкообразного изменения вида корреляционной функции случайного процесса в опознающих устройствах различного назначения, системах управления и линиях связи.

Целью изобретения является расширение класса решаемых задач и повышение быстродействия и точности определения момента разладки.

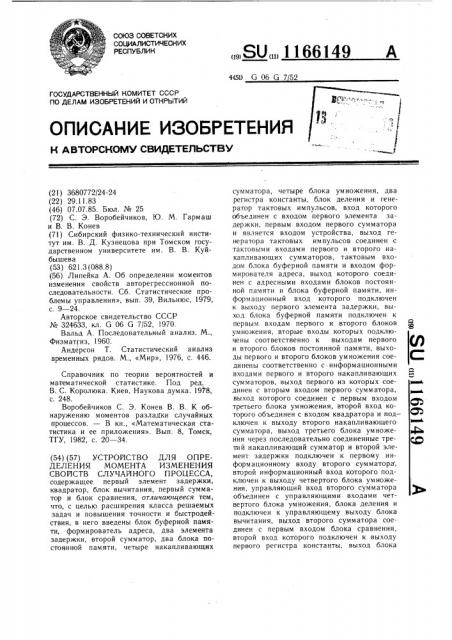

На чертеже представлена блок-схем а устройства.

Устройство содержит генератор 1 тактовых импульсов, первый элемент 2 задержки, блок 3 буферной памяти, формирователь 15

4 адреса, первый сумматор 5, первый накапливающий сумматор 6, первый блок 7 умножения, первый блок 8 постоянной памяти, второй блок 9 постоянной памяти, второй блок 10 умножения, второй накапливающий сумматор 11, третий блок 12 умножения, квадратор 13, третий накапливающий сумматор 14, первый регистр 15 хранения константы, второй регистр 16 хранения константы, второй элемент 17 задержки, третий элемент 18 задержки, блок 19 вычи- 25 тания, четвертый накапливающий сумматор 20, блок 21 сравнения, второй сумматор

22, блок 23 умножения и блок 24 деления.

Входом предлагаемого устройства является вход генератора 1 тактовых импульсов, объединенного с первым входом перзо вого сумматора 5 и входом элемента 2 задержки, подсоединенного своим выходом к информационному входу блока 3 буферной памяти. Выход генератора 1 тактовых импульсов подключен к тактовому входу блока 3 буферной памяти, к входу формирователя 4 адреса, к тактовому входу первого накапливающего сумматора 6 и к тактовому входу второго накапливающего сумматора 11, выход блока 3 буферной памяти подключен к первому информационному входу первого блока 7 умножения и к перобъединен с входом четвертого накапливающего сумматора и подключен к выходу квадратора, выход четвертого накапливающего сумматора соединен с первым входом блока вычитания, второй вход которого подключен к выходу второго регистра константы, информационный выход блока вычитания соединен с входом третьего элемента задержки. вому информационному входу второго блока 1 умножения, выход формирователя 4 адреса подключен к управляющему входу блока 3 буферной памяти, к адресному входу первого блока 8 постоянной памяти и к адресному входу второго блока 9 постоянной памяти, выход первого блока 8 постоянной памяти подсоединен к второму информационному входу первого блока 7 умножения, выход которого подключен к информационному входу первого накапливающего сумматора 6, выход которого подключен к второму входу первого сумматора 5, выход второго блока 9 постоянной памяти подсоединен к второму информационному входу второго блока 10 умножения, выход которого . подключен к информационному входу второго накапливающего сумматора

11, выход которого подключен к входу квадратора 13 и к соответствующему информационному входу третьего блока 12 умножения, подключенного другим информационным входом к выходу первого сумматора 5, выход квадратора 13 подсоединен с одному из информационных входов блока 24 деления и к входу четвертого накапливающего сумматора 20, выход которого подключен к первому информационному входу блока

19 вычитания, подсоединенного вторым информационным входом к выходу соответствующего регистра 5 хранения константы, управляющий выход блока 19 вычитания подключен к управляющему входу блока

24 деления, другой информационный вход которого подключен через второй элемент

18 задержки к информационному выходу блока 19 вычитания, к управляющему входу четвертого блока 23 умножения и к управляющему входу второго сумматора 22, выход блока 24 деления подключен к соответствующему информационному входу четвертого блока 23 умножения, выход третьего блока 12 умножения подсоединен к входу третьего накапливающего сумматора

14 и к другому информационному входу

11бб149 четвертого блока 23 умножения, выход которого подсоединен к одному из информационных входов второго сумматора 22, другой информационный вход которого через другой элемент 17 задержки подключен к выходу третьего накапливающего сумматора 14, выход второго сумматора 22 подключен к первому информационному входу блока 21 сравнения, подключенного вторым информационным входом к выходу первого регистра 15 хранения константы.

В основу работы предложенного устройства положен следующий алгоритм.

Известно (4), что любой стационарный случайный процесс можно описать рекуррентным уравнением порядка Р, на этом основании поступающий на вход предлагаемого устройства случайный процесс опишем уравнением

<(+1. Ф1+ЛР3-i+-"+Л Х g ð+ Kj,ps)(8, до момента разладки t = 9 и уравнением

"> =) "j Ó Й- " 3Р +1-р+1у+1, i 8 после момента разладки t = 9 (отметим, что, как указано в (5), порядок процесса р на практике не превышает двойки, т.е.

P42). Здесь отсчеты шума ; независимы, имеют нулевое среднее значение и дисперсию 6„,, причем вероятностное распределение произвольно, два набора известных значений параметров Л1 ..., Л, и P,, ..., р характеризуют корреляционную функцию случайного процесса соответственно до и после момента разладки 8 х) - j-é отсчет случайного процесса.

Для обнаружения разладки случайного процесса применяется такая модификация метода наименьших квадратов, когда длительность каждого отдельного интервала наблюдения, завершающегося вынесением решения о наличии или отсутствии разладки, не фиксируется заранее, а определяется (последовательно, в ходе наблюдения процесса) величиной, характеризующей различия статистической структуры процесса. до и после разладки. Процедура обработки наблюдений (выборочных значений случайного процесса) является последовательной процедурой типа Вальда (3), при этом, как и у Вальда, используется два постоянных порога, предназначенных для выполнения другой роли, чем в процедуре Вальда. Первый порог Н служит для определения либо необходимости проведения еще одного наблюдения (или нескольких наблюдений) случайного процесса, либо достаточности имеющегося числа наблюдений для того, чтобы перейти к этапу вынесения решения о наличии либо отсутствии разладки случайного процесса. Собственно решение о наличии разладки случайного процесса выносится при превышении второго порога д, если же второй порог не превышен, выносится решение об отсутствии разладки.

Моменты 1,1, i =0,1,2,..., в которые может быть принято решение о разладке, опреде5 ляются последовательно в процессе наблюдения случайного процесса по следующим соотношениям гь, = p, +(K Li-> 1., 1 11) >Н) (.Г +1 где (1)+1 б11)Xj +--+ (p Лр) Xjig-ð, Н>0 — постоянный порог, определяемый допустимым запаздыванием момента обнаружения разладки, которое определяется вероятностью пропуска сигнала, Р», и допустимой величиной вероятности ложной тревоги Р»т.

В момент 1 определяется величина 1

) С

Y;=Б с(й)9111(xj.г ю

, если Г;, < .1 й(3) =

CH -, f (j)) / 1" Я;), ети 1=-ti

25 при превышении которой порога Ю, т.е. при

yz>3; выносится решение о наличии разладки, в противном же случае (при у; B) выносится решение об отсутствии разладки случайного процесса, поступившего на вход устройства.

Значения порогов Н и Б определяются из следующих соотношений (6) Работа устройства основана на том, что среднее значение величин у1 изменяется после разладки на известную величину

Н (т е с - — 11 — до разладки на +

2 3 после разладки), а дисперсия величин у; не превосходит H 6„, (8). Знание величины Н изменения среднего значения и верхней границы дисперсии последовательности jy;J, i= 1.2... позволяет выбрать такое пороговое

45 значение 3 из интервала (- - вЂ, ), что превышение величинами у; выбранйого таким образом порога С1 будет происходить достаточно редко до разладки (это эквивалентно малому числу ложных тревог) и достаточно часто после разладки (это эквивалентно большой вероятности правильного обнаружения разладки) исследуемого случайного процесса. Такой выбор порогов Н и Е обеспечивает по сравнению с предлагаемым устройством более надежное обнаружение одной или нескольких разладок расширенного класса случайных процессов, а также большую быстроту и точность нх обн а ружен и я.

1166149

Большая быстрота и точность обнаружения разладок предлагаемым устройством обеспечивают тем, что требуемой точности обнаружения разладки соответствует вполне определенная длительность интервала наблюдения, выражающаяся в тех различиях статистических характеристик (до разладки и после разладки) случайного процесса, которые нужно накопить для достижения требуемой точности.

В известном устройстве выбор малого интервала наблюдения обеспечивает быстрое обнаружение разладки, но и обуславливает малую величину накапливаемых различий статистических характеристик исследуемого процесса, что ведет к увеличению числа ложных срабатываний и, следовательно, к ухудшению точности, для увеличения же точности необходимо выбирать интервал наблюдения неопределенно большим, что уменьшает быстроту обнаружения разладки случайного процесса.

Устройство работает следующим образом.

Квантованные по времени и уровню входные реализации наблюдаемого случайного процесса (СП), x> J = 0,1,2... запускают генератор 1 тактовых импульсов (фиг. 1) и одновременно поступают на вход первого элемента 2 задержки и на первый информационный вход первого сумматора 5. Входные сигналы х задерживаются первым элементом 2 задержки на один такт, приобретая вид Х,, j = 1,2... и поступают с его выхода на информационный вход блока 3 буферной памяти 7, представляющего собой сдвигающий регистр, где последовательно записывается в р числовых ячеек сдвигающего регистра, запись осуществляется на каждом такте по тактовым импульсам, поступающим с выхода генератора 1 тактовых импульсов на тактовый вход блока 3 буферной памяти. По мере поступления сигналов X>, j =0,1.2..., в р числовых ячеек блока 3 буферной памяти, эти сигналы подаются с выхода блока 3 буферной памяти на первые информационные входы первого и второго. блоков 7 и 10 блоков умножения, на вторые информационные входы которых поступают выходные сигналы соответственно с блоков 8 и 9 постоянной памяти. Таким образом, сигнал U в регистре блока 3 буферной памяти на (j + 1)-ом такте имеет следующий вид (при чтении слева направо, когда крайняя левая ячейка сдвигающего регистра всегда содержит старший разряд) х, ..., Х +, j = 0,1,2...

В каждом из блоков 8 и 9 постоянной памяти имеется р-разрядный регистр, в ячейки которых соответственно записываются следующие априорно известные наборы (при чтении слева направо) р,-л„..., у;л, ° -- - — *, ..., - — - -, 5 причем наборы констант Я„..., Л, и)4,...РР известны заранее и характеризуют параметры корреляционной функции СП поступающего на вход устройства соответственно до и после разладки.

Выходные сигналы U< блока 4 формирования адреса, запускаемого по входу импульсами с выхода генератора 1 тактовых импульсов, являются адресными и поступают на адресные входы блока 3 буферной памя15 ти блоков 8 и 9 постоянной памяти. После поступления адресных сигналов Uq формируются выходные сигналы U, U> и причем сигналы U > .и U перемножаются в первом блоке 7 умножения, а сигналы Uz и Ug перемножаются Во втором блоке 10 умножения. После окончания умножений выходные сигналы U< и U указанных блоков умножения поступают соответственно на информационные входы накапливающего сумматора 6 и накапливающего сумматора

25 11, в которых осуществляется последова-. тельное суммирование на каждом такте, причем в конце каждого такта накапливаю щие сумматоры 6 и 11 должны быть приведены в исходное состояние, соответствующее

30 нулевым выходным сигналам Uq и U«.На (j+1)-м такте сигналы U, и Ц, имеют сдедующий вид

11 =Х - — — (-1+1); -1 2

55 р

U„„— г (-il;+pi ) х .

31

Так как первый сумматор 5 осуществляет параллельное суммирование сигналов

5 х, и U поступающих соответственно на его первый и второй информационные входы, то на первый информационный вход третьего. блока 12 умножения поступает сигнал следующего вида

3 3

Ц =х . + Us ° причем на второй информационный вход блока 12 умножения поступает сигнал U

Одновременно сигнал U поступает на вход

3 квадратора 13, где перемножается сам .на себя и в виде выходного сигнала 11 1= (U )

41 одновременно поступает на вход четвертого накапливающего сумматора 20 и на соответствующий информационный вход блока

24 деления. Накапливающий сумматор 20 в процессе последовательного суммирования входных сигналов формирует, например, на (1+1)-ом такте сигнал U = (Ц ) который поступает на первый вход блока

1166149

- Uzo.

Составитель А. Иванова

Редактор Н. Пушненкова Техред И. Всрес Корректор И. Эрдейи

Заказ 4313/46 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

19 вычитания, на второй информационный вход которого подается значение константы Н, хранящейся во втором регистре 16 константы. С помощью порогового значения

Н последовательно формируются интервалы наблюдений, завершающиеся вынесением решения о наличии или отсутствии раз ладки. Сигнал с информационного выхода блока 19 вычитания имеет на (j+1)-ом такте следу ощий вид

Сигнал U » после задержки на один такт вторым элементом 12 задержки подается на сбответствующий информационный вход блока 24 деления, который срабатывает при поступлении на его управляющий вход незадержанного сигнала U,д с выхода блока 19 вычитания.

Одновременно управляющие сигналы

U,z поступают на управляющие входы четвертого блока 23 умножения и второго сумматора 22 для их запуска. Сигнал Uz+ с выхода блока 24 деления поступает на соответствующий информационный вход четвертого блока 23 умножения, на другой информационный вход которого поступает сигнал U» с выхода третьего блока 12 умножения, причем сигнал L q поступает также на вход третьего накапливающего сумматора 14. Сигнал Li, с выхода третьего накапливающего сумматора 14 через второй элемент 17 задержки подается на первый информационный вход второго сум.латора 22 осуществляющего параллельное суммирование, причем на второй информационный вход второго сумматора 22 поступает сигнал L; с информационного выхода четвертого блока

1О

3 умножения, сигнал L: с выхода сумматора 22 поступает на первый информационный вход блока 21 сравнения. на второй информационный вход которого подается значение константы с) . хранящейся в первом ре15 гистре 15 хранения константы, причем к началу следующего такта сигналов Upg долж1о быть осуществлено приведение в исходное состояние (сброс третьего и четвертого накапливающих сумматоров 14 и 20), соответствующее нулевым выходным сигналам Lö и 11ао. Сигнал-решение появляется на выходе блока 21 сравнения лишь в тот момент, когда сигнал U превышает значение о, появ.пение сигнала L а, означает принятие устройством решения о наличии

25 разладки случайного процесса, поступающего на его Bxo",.