Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

ДИФФЕРЕНЦИАЛЬНЫЙ УСШШТЕЛЬ, содержащий первый входной дифферен- ; циальный каскад, выполненный понас-; кадной схеме, имеющий первый, вто-т ; рой, третий и четвертый выходы, являклциеся попарно противофазными, соединенные с входами соответственно первого, второго, третьего и четвертого отражателей тока, вьгаоды питания которых подключены к первой и второй шинам источника питания соответственно, и генератором тока в токозадающей цепи, вьшолненным на пятом и шестом отражателях тока, выходы которых объединены и являются выходом генератора тока, а выводы питания подключены соответственно к первой и второй шинам источника пи- , тания, отличающийся тем, что, с целью повышения коэффициента подавления синфазного сигнала, параллельно первому входному дифференциальному каскаду введен второй входной дифференциальный кпскад,. выполненный по каскадной схеме, токозадающая цепь которого соединена с выходом генератора тока, и имеющий первьш, второй, третий и четвертый выходы, являющиеся попарно противофазными , соединенные соответственно с вторым, первым, четвертым и третьим выходами.первого входного дифференциального каскада, атакже введены первьй, второй, третий и четвертый дополнительные транзисторы, (Л коллекторы которых являются попарно противофазными выходами дифференциального усилителя, базы подключены к выходам соответственно первого, второго, третьего и четвертого отражателей тока, причем эмиттеры первого и второго дополнительных транзис05 Од торов объединены и подключены к входу пятого отражателя тока, а эмиттеto ры третьего и четвертого дополниvl тельных транзисторов объединены и подключены к входу шестого отражателя тока. . ,

СОЮЗ СОВЕТСКИХ . СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

4(s1) Н 03 F 3/45 !

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3596139/24-09 (22) 19.05.83 (46) 07.07.85. Бюп. Р 25 (72) Л.П.Домнин, А.Я.Гаршин, А.В.Грибанов, В,M.Ïèòîëèí, .П.А,Арутюнов и С.Н.Смагин (53) 621.375.024 (088.8) (56) Авторское свидетельство СССР

Р 1062852, кл. Н 03 F 3/45,03.09.82.

Авторское свидетельство СССР

У 736119, кл. G 06 G 7/12,25.05.77. (54) (57) ДИФФЕРЕНЦИАПЬНЬЙ УСИЛИТЕЛЬ, содержащий первый входной дифферен-., циальный каскад, выполненный по кас-:: . кадной схеме, имеющий первый, вто-. рой, третий и четвертый выходы, являющиеся попарно противофазными, соединенные с входами соответственно первого, второго, третьего и четвертого отражателей тока, выводы питания которых подключены к первой и второй шинам источника питания соответственно, и генератором тока в токозадающей цепи, выполненным на пятом и шестом отражателях тока, выходы которых объединены и являются выходом генератора тока, а выводы питания подключены соответственно к первой и второй шинам источника пи„„SU„„3 166271 А

:-тания, отличающийся тем, что, с целью повышения коэффициента подавления синфазного сигнала, параллельно первому входному дифференциальному каскаду введен второй входной дифференциальный к",скад,. выполненный по каскадной схеме, токозадающая цепь которого соединена с выходом генератора тока, и имеющий первый, второй, третий и четвертый выходы, являющиеся попарно противофазными, соединенные соответственно с вторым, первым, четвертым и третьим выходами. первого входного дифференциального каскада, а также введены первый, второй, третий и четвертый дополнительные транзисторы, коллекторы которых являются попарно противофазными выходами дифференциального усилителя, базы подключены к выходам соответственно первого, второго, третьего и четвертого отражателей тока, причем эмиттеры первого и второго дополнительных транзисторов объединены и подключены к входу пятого отражателя тока, а эмиттеры третьего и четвертого дополнительных транзисторов объединены и подключены к входу шестого отражателя тока.

1166271

Изобретение относится к вычисли тельной технике и технике связи и может использоваться в аналоговых вычислительных машинах, в системах автоматики и телемеханики. 5

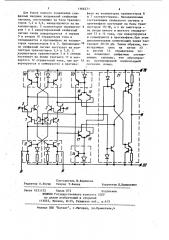

Цель изобретения — повьппение коэффициента подавления синфаэного сигнала, На чертеже представлена принципиальная электрическая схема пред10 лагаемого устройства.

Дифференциальный усилитель содержит первый входной дифференциальный каскад, выполненный на .транзисторах

1-4, второй нходн 1й дифференциальный каскад, ныполненнь и на транзисторах

5 — 8, первый 9, вт ой 10, третий 11, четвертый 12 отраж гели тока, генератор тока, выполненный на пятом 13 и шестом 14 отражателях тока, а также первый 15, второй 16, третий 17, четвертый 18 дополнительные транзисторы, первую 19 и вторую 20 шины источника питания, при этом четыре попарно протинофаэных выхода диффе4 ренциального усилителя соединены с каскадом 21 с несимметричным выходом.

Устройство работает следующим образом.

Дифференциальный сигнал, поданный на базы транзисторов 1 и 2, усиливается и инвертируется на их коллекторах. Затем усиливаемый сигнал поступает с коллектора транзистора 1 на вход первого отражателя 9 тока, а с 3$ коллектора транзистора 2 — на вход . второго отражателя 10 тока. На выходах первого 9 и второго 10 отражателей тока сигнал инвертируется и складывается в фазе с усилинаемым сигна- 40 лом на коллекторах соответственно транзисторов 6 и 5. С эмиттеров транзисторов 1,2 и 5 6 усиливаемый дифференциальный сигнал поступает в эмиттеры транзисторов 3 и 4 и в эмиттеры 45 транзисторов 7 и 8, включенных по схе" ме с общей базой, где усиливается.

С коллекторов транзисторов 3 и 4 усиливаемый сигнал поступает соответственно на входы третьего 11 и четвертого 12 отражателей тока, на выходах которых инвертируется и складывается в, фазе с сигналом на коллекторах транзисторов соответственно 8 и 7.

Таким образом, осуществляется сложе- Я ние усиливаемых сигналов. При этом суммируемые усиливаемые сигналы на коллекторах транзисторов 5 и 6, 7 и

8 находятся попарно между собой в про.тивофазе, база транзистора 1 является инвертирующим нходом дифференциального усилителя, а база транзистора 2 = его неинвертирующим входом.

Далее усилинаемый сигнал поступает на базы второго 16, первого 15, четвертого 18 и третьего 17 дополнительных транзисторов. При подаче возрастающего уровня сигнала на входы дифференциального усилителя соответственно увеличивается уровень сигнала на базах первого 15, второго 16, третьего 17 и четвертого 18 дополнительных транзисторов, что определяет соответственное увеличение тока в их эмиттерах, а это вызывает увеличение тока на выходах пятого 13 и шестого

14 отражателей тока и, следовательно, приводит к увеличению базовых токов транзисторов 3,4,7,8 и эмиттерных токов транзисторов 1,2,5,6, т.е. приводит к увеличению тока, потребляемого первым и вторым входными дифференциальными каскадами дифференциального усилителя. Вследствие этого улучшается линейность вольт-амперных характеристик, входящих в него активных элементов, что приводит к значительному. уменьшению коэффициента нелинейных искажений дифференциального усилителя и амплитуды боковых составляющих частот передаваемого сигнала.

Дифференциальный сигнал, поступающий на базы первого 15, нторого 16, третьего 17 и четвертого 18 дополнительных транзисторов, усиливается, инвертируется на их коллекторах и поступает на каскад 21.

Синфазные входные напряжения в значительной мере подавляются эа счет большого дифференциального сопротивления пятого 13 и шестого 14 отражателей тока токозадающей цепи, выходы которых включены в базовую цепь транзисторов 3,4,7 и 8. Однако такое подавление синфазных сигналов (порядка — 50-60 дБ) является недостаточным для надежного функционирования дифференциального усилителя в режиме компариронания и в условиях большого уровня помех, определяемого допустимым уровнем и величиной поданления синфазных помех, абсолютная величина которой должна быть сравнима или превышать величину коэффициента усиления дифференциального сигнала.

1166271

Составитель И.Водяхина

Редактор О.Бугир Техред Т.Фанта Корректор Л.Пилипенко

Заказ 4321/52 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открьггий

113035, Москва, R-35, Раушская наб., д.4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная,4

Для более полного подавления синфазных входных напряжений синфазные сигналы, поступающие на базы транзисторов 1,2 и 5,6, инвертируются на их коллекторах. С коллекторов транзисторов 1 и 2 инвертированный синфазный сигнал снова инвертируется в первом

9 и втором 10 отражателях тока и складывается в противофазе .на коллекторах транзисторов 6 и 5. Одновременно синфазный сигнал поступает на коллекторы транзисторов 3,4 и 7,8. С коллекторов транзисторов 3 и 4 сигнал поступает на входы третьего 11 и четвертого 12 отражателей тока, где инвертируется и суммируется в противо4 фазе на коллекторах транзисторов 8 и 7 соответственно. Неподавленные составляющие синфазного сигнала в противофазе поступают на базы тран

5 эисторов 15-18, а с их эмитт ровна входы пятого и шестого отражателей 13 и 14 тока, где инвертируются и суммируются в противофазе.При этом дополнительная компенсация помех составляет 20-30 дБ. Таким образом, токозадающая цепь на пятом !3 и шестом 14 отражателях тока подавляет синфазные составляющие сигналы, что обусловле-!

5 но противофаэной компенсацией сигналов помех.