Распределитель

Иллюстрации

Показать всеРеферат

РАСПРЕДЕЛИТЕЛЬ, содержаш ,ий дешифратор, счетчик, первый элемент И и RS-триггер, S-вход которого соединен с входом запуска, а единичный выход - с первым входом первого элемента И, второй вход которого подключен к первому входу распределителя, а выход - соединен с входом счетчика, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены блок ключей, второй и третий элементы И, расширительимпульсов , m соединенных последовательно двоично-десятичных счетчиков, (т-1) дешифраторов , коммутатор, блок элементов И и блок RS-триггеров, выходы счетчика соединены с соответствующими входами блока ключей, выходы которого через второй элемент И подключены к входу расширителя импульсов, выход которого соединен с вх.одом сброса счетчика и с входом первого двоично-десятичного счетчика, выходы m двоично-десятичных счетчиков через соответствующие дешифраторы соединены с соответствующими входами коммутатора, выходы которого подключены к входам соответствующих элементов . И блока и входам третьего элемента И, другие входы которых соединены с вторым входом распределителя, i выходы элементов И блока через соответ (Л ствуюш,ие триггеры подключены к выходным шинам распределителя, а выход третьего элемента И соединен с R-входом RS-триггера.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPGHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ. КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3666731/24-21 (22) 23.11.83 (46) 07.07.85. Бюл. № 25 (72) А. В. Щербак и Н. Г. Батовская (53) 621.382 (088.8) (56) Авторское свидетельство СССР № 1057936, кл. Н 03 К 17/62, 30.11.83.

Майоров С. А. и Новиков Г. И. Принципы организации цифровых машин. Л., «Машиностроение», 1974, с. 279, рис. 7 — 29. (54) (57) РАСПРЕДЕЛИТЕЛЬ, содержащий дешифратор, счетчик, первый элемент

И и RS-триггер, S-вход которого соединен с входом запуска, а единичный выход с первым входом первого элемента И, второй вход которого подключен к первому входу распределителя, а выход — соединен с входом счетчика, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены блок ключей, второй и третий элементы И, расширитель..,Я0„„1166294 A

4(59 Н 03 К 17 62 импульсов, m соединенных последовательно двоично-десятичных счетчиков, (m — 1) дешифраторов, коммутатор, блок элементов И и блок RS-триггеров, выходы счетчика соединены с соответствующими входами блока ключей, выходы которого через второй элемент И подключены к входу расширителя импульсов, выход которого соединен с входом сброса счетчика и с входом первого двоично-десятичного счетчика, выходы m двоично-десятичных счетчиков через соответствующие дешифраторы соединены с соответствующими входами коммутатора, выходы которого подключены к входам соответствующих элементов . И блока и входам третьего элемента И, другие входы которых соединены с вторым входом распределителя, выходы элементов И блока через соответствующие триггеры подключены к выходным шинам распределителя, а выход третьего элемента И соединен с R-входом RS-триггера.

1166294

Изобретение относится к импульсной технике и может быть использовано в различных вычислительных и автоматических системах.

Цель изобретения — расширение функциональных возможностей.

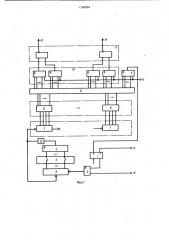

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 — циклограмма получения двух импульсов при использовании двух двоично-десятичных счетчиков и двух дешифраторов; на фиг. 3— пример соединения дешифраторов и элементов И с помощью коммутатора для организации циклограммы фиг. 2.

Распределитель содержит (фиг. 1) RSтриггер 1, первый элемент И 2, к-разрядный счетчик 3, второй элемент И 4, блок

5 ключей, третий элемент И 6, m двоична-десятичных счетчиков 7, m дешифраторов

8, коммутатор 9, блок 10 элементов И, блок 11 RS-триггеров, расширитель 12 импульсов, первый и второй входы 13 и 14, вход 15 запуска и выходы 16 распределителя.

Вход 13 через первый элемент И 2, другой вход которого соединен с прямым выходом RS-триггера 1, подключен к входу к-разрядного счетчика 3, выходы через соединенные последовательно блок 5 ключей и второй элемент И 4 подключены к входу расширителя 12 импульсов, выход которого соединен с входом сброса счетчика 3 и входом первого счетчика 7, выходы m двоично-десятичных счетчиков 7 через соответствующие дешифраторы 8 подключены к входам коммутатора 9, выходы которого через соединенные последовательно блоки 10 элементов И и блок 11 RS-триггеров подключены к соответствующим выходам 16, причем соответствующие выходы коммутатора

9 соединены с третьим элементом И 6, выход которого подключен к R-входу RSтриггера 1.

Устройство работает следующим образом.

На вход 15 распределителя подается запускающий импульс (фиг. 2 а), который устанавливает в единичное состояние RSтриггер 1. В результате этого снимается блокировка с сигнала по входу 13 и синхронизирующие импульсы начинают поступать на вход к-разрядного счетчика 3 (фиг. 2 б), при этом последний начинает переключаться в состояния 1, 2, ....

По достижении состояния, определенного ключами блока 5 ключей, на выходе второго элемента И 4 формируется импульс (фиг. 2 в) и через расширитель 12 импульсов поступает на вход первого из m двоично-десятичных счетчиков 7. Этим же импульсом приводится в исходное состоя10

45 ние к-разрядный счетчик 3. Далее процесс переключения состояний счетчика 3 повторяется.

Импульсами с выхода расширителя 12 импульсов первый из m двоично-десятичных счетчиков 7 последовательно переключается в состояние 1, 2, ...., 9, которые выделяет первый из m дешифраторов 8 (фиг. 2 г, н), а десятым импульсом первый из m двоично-десятичных счетчиков 7 устанавливается в исходное состояние и формирует на своем выходе импульс счета для следуюIlJeI 0 из m двоично-десятичных счетчиков 7.

Процесс счета импульсов и выделения состояния следующих двоично-десятичных счетчиков 7 следующими дешифраторами 8 аналогичен приведенному выше (фиг. 2 п, р, с) с учетом того, что частота переключений последующего из m двоично-десятичных счетчиков 7 в 10 раз ниже предыдущего. К входам блока 10 элементов И подключаются через коммутатор 9 определенные выходы m дешифраторов 8, причем к входу каждого из элементов И блока 10 может быть подключен только один из десяти выходов каждого из m дешифраторов 8.

При совпадении единичных состояний выходов m дешифраторов 8, подключенных к входам элементов И блока 10, и наличии стробирующего сигнала на входе 14 на выходах элементов И блока 10 формируются импульсы (фиг. 2 т — х), которые устанавливают и сбрасывают в заданные моменты времени RS-триггеры блока 11, а также при совпадении единичных состояний выходов

m дешифраторов 8, подключенных к третьему элементу И 6, формируется на его выходе последний импульс (фиг. 2 cu), устанавливающий в нуль RS-триггер 1, выходной сигнал последнего блокирует прохождение входного синхронизирующего сигнала по шине 13.

На этом работа распределителя прекращается. Повторный пуск распределителя осуществляется подачей импульса с входа 15.

На фиг. 2 представлена циклограмма распределителя для формирования двух импульсов при использовании двух двоичнодесятичных счетчиков 7 и двух дешифраторов 8.

Изменение циклограммы импульсов достигается сменой коммутатора 9, а необходимое подключение выходов дешифратора

8 к входам элементов И блока 10 можно задать, разбив циклограмму на одинаковые участки и пронумеровав их.

Для приведенной на фиг. 2 циклограммы необходимо в коммутаторе 9 обеспечить соединения согласно фиг. 3 и замкнуть ключи для обеспечения деления синхронизирующего сигнала на входе 13 на три.

1166294

1166294 и и

Ц

Ш

00 01 02 03 04 05 Об 07 08 О 10 11 Q 13 14 !5 1b 17 18 19 20 21 22

Фиг.2

1166294

Составитель Л. Захарова

Редактор О. Бугир Техред И. Верес Корректор М. Демчик

Заказ 4322/53 Тйраж 872 Подписное

ВНИИПИ, Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Рву шская наб., д. 4/5

Филиал ППП <Патент», r. Ужгород, ул. Проектная, 4