Устройство для определения знака разности фаз

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (! 9) (3 3) (51)4 4л 01 R 25/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3597537/24-21 (22) 30.05.83 (46) 15.67,85. Бюл. М 26 (72) М.М.Бойко, Е.С.Вальшонок, Н.П.Курносенков, В,И.Кустов и

В.Д.Митин (53) 621.317.77(088.8) (56) Авторское свидетельство СССР

В 700843, кл. (j 01 R 25/00, 1977.

Авторское свидетельство СССР

И 1065785, кл. Gi 01 R 25/ОО, 1982. (54)(57) 1. УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАКА РАЗНОСТИ ФАЗ, содержаЩее первый, второй и третий формирователи импульсов, входы которых .соединены с соответствующими входами устройства, и блок сравнения, выход которого соединен-с выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности за счет уменьшения динамической погрешности, в него введены генератор импульсов, счетчик импульсов и два регистра, при этом первый вход счетчика импульсов соединен с генератором импульсов, второй вход соединен с выходом третьего формирователя импульсов, а выход соединен с информационными входами первого и второго регистров, управляющие входы которых соединены с выходами соответствующих формирователей импульсов, а выходы соединены с первым и вторым входами блока срав- «© нения соответственно.

2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что блок сравнения ,содержит цифровой компаратор, сумматор и запоминающий элемент, при этом выход цифрового кампаратора соединен с выходом блока сравнения и входом запоминающего элемента, 167524 выход которого соединен с первым входом сумматора, соединенного вторым входом с первым входом блока сравнения, а выходом — с первым входом цифрового компаратора, второй вход которого соединен с вторым входом блока сравнения.

Изобретение относится к измерительной технике и может быть использовано в измерительных приборах и системах. Цель изобретения — повышение точ- . 5 ности за счет уменьшения динамической погрешности.

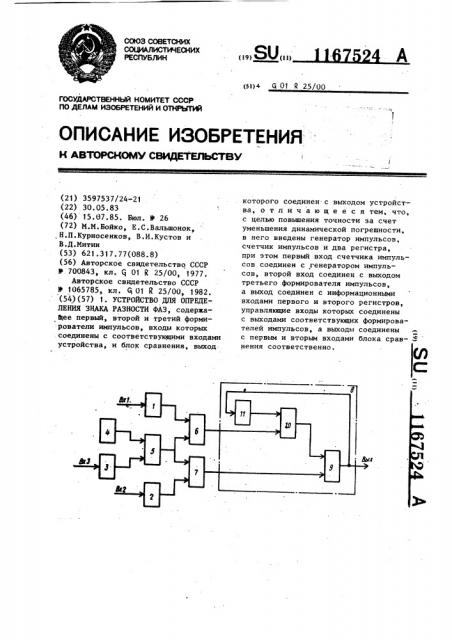

На чертеже приведена схема устройства.

Устройство содержит формирователи

1, 2 и 3 импульсов, генератор 4 импульсов, счетчик 5 импульсов, регистры 6 и 7 и блок 8 сравнения, состоящий из цифрового компаратора 9, сумматора 10 и запоминающего элемента 11, при этом входы формирователей

1, 2 и 3 импульсов соединены с соот- ветствующими входами устройства, выходом которого является выход блока 8 сравнения, первый вход счетчика 20

5 импульсов соединен с выходом генератора 4 импульсов, второй вход соединен с выходом формирователя 3 импульсов, а выход соединен с информационными входами регистров 6 и 7, управляющие входы которых соединены с выходами формирователей 1 и 2 импульсов соответственно, а выходы соединены с соответствующими входа ми блока 8 сравнения. В блоке 8 срав-З0 кения выход цифрового компаратора

9 соединен с выходом устройства и входом запоминающего элемента 11, выход которого соединен с первым входом сумматора 10, соединенного вторым входом с первым входом блока 8, а выходом подключенного к первому входу цифрового компаратора 9, вто" рой вход которого соединен с вторым входом блока 8.

Устройство работает следующим образом.

На первый и второй входы устрой- ства поступают сигналы, знак разности фаз которых необходимо определить, на третий вход устройства поступает опорный сигнал, задающий начало отсчета фазового сдвига. На выходе счетчика 5 устанавливаются коды в соответствии с числом импульсов, поступивших на его тактовый вход от генератора 4 после поступления на установочный вход импульса сброса от формирователя 3. С поступлением импульсов от формирователей

1 и 2 на управляющие входы регистров 6 и 7 в последние вводятся коды, определяющие сдвиги по фазе сигналов на первом и втором входах по отношению к опорному сигналу. Коды фазовых сдвигов поступают на входы цифрового компаратора 9 от регистра 7 непосредственно, а от регистра 6 через сумматор 10.

На выходе цифрового компаратора 9 формируется сигнал, определяющий знак разности фаз. Устойчивость сигнала на выходе устройства обеспечивается тем, что код регистра 6 увеличивается на единицу младшего разряда, если в предыдущий момент времени фазовый сдвиг сигнала на первом входе устройства превышал

ЮЪ фазовый сдвиг сигнала на его втором входе. Это осуществляется подачей на сумматор 10 от запоминающего злемента 11, управляемого цифровым компаратором 9, соответствующего када.

Таким образом, в устройстве обеспечивается устойчивость сигнала на выходе при высоком быстродействии, которое в данном случае ограничивается только частотой входных сигналов.

Составитель Н.Агеева

Техред Л.Микеш Корректор Л.Бескид

Редактор И.Рыбченко

Заказ 4431/43 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 з 1167524 4

Предлагаемое устройство обеспечи-- использования в измерительных сисвает уменьшение динамической по- темах с повышенной скоростью измегрешности, что позволяет расширить нения фазового сдвига входных сигобласть его применения за счет налов.