Самонастраивающаяся следящая система

Иллюстрации

Показать всеРеферат

САМОНАСТРАИВАЮЩАЯСЯ СЛЕДЯЩАЯ СИСТЕМА, содержащая последовательно соединенные блок задержки, первьв) умножитель, перлый интегратор , первый усилитель, второй умножитель , сумматор, последовательно соединенные эталонную модель, .первый блок сравнения, третий умножитель, второй интегратор, второй усилитель, четвертый умножитель, выход объекта .регулирования соединен с вторыми входами первого блока сравнения, третьего и четвертого умножителей, выход первого блока сравнения подключен ко второму входу первого умножителя , выход блока задержки соединен с вторым входом второго умножителя, выход четвертого умножителя подключен к второму входу сумматора , выход которого соединен с входом объекта регулирования, выход которого подключен к входу блока задержки, отличающаяся тем, что, с целью повьшения точности работы cиcтe в l, в нее введены последовательно соединенные второй блок сравнения, пятни умножитель, третий интегратор, третий усилитель, шестой умножитель, вход второго блока сравнения соединен с выходом объекта регулирования, второй вход пятого умножителя подключен к выходу первого блока сравнения, выход второго блока сравнения соединен с вторым входом шестого умножителя, did выход которого соединен с третьим входом сумматора. ел 00 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТ ИЧЕСНИХ

РЕСПУБЛИК (19) О 1J (5 l ) 4

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ::К ABTOPCHOIVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3533960/24-24 (22) 03.01.83 (46) 15.07.85. Бюл. Ф 26 (72) А.П.Крывчак и А.М.Цыкунов (71) Фрунзенский политехнический ,институт (53) 62-50(088 ° 8) (56) 1. Авторское свидетельство СССР

У 327448, кл. С 05 В 13/02, 1972.

2. Авторское свидетельство СССР

Ф 648947, кл. С 05 В 13/02, 1979.

3. Авторское свидетельство СССР

В 634235, кл. С 05 В 15/00, 1978 (прототип). (54) (57) .САМОНАСТРАИВАЮЩАЯСЯ СЛЕДЯЩАЯ CHCTEHh, содержащая последовательно соединенные блок задержки, первый умножитель, первый интегратор, первый усилитель, второй унножитель, сумматор, последовательно . соединенные эталонную модель, .первый блок сравнения, третий уиножитель, второй интегратор, второй усилитель, четвертый уиножитель, выход объекта регулирования соединен с вторыми входами первого блока сравнения, третьего и четвертого умножителей, выход первого блока сравнения подключен ко второму входу первого умножителя, выход блока задержки соединен с вторым входом второго умножителя, выход четвертого умножителя подключен к второму входу сумматора, выход которого соединен с входом объекта регулирования, выход которого подключен к входу блока задержки, отличающаяся тем, что, с целью повышения точности работы системы, в нее введены последовательно соединенные второй блок сравнения, пятый умножитель, третий интегратор, третий усилитель, шестой уиножитель, вход второго блока сравнения соединен с выходом объекта регулирования, второй вход пятого уиножителя подключен к выходу первого блока сравнения, выход второго блока сравнения соединен с вторым входои шестого умножителя, выход которого соединен с третьии входом сумматора. 1 1167

Изобретение относится к технической киберн .тике и может быть использовано в системах автоматического регулирования объектами с запаздыванием, причем параметры объекта неизвестны или медленно меняются во времени. Такими системами являюТся, например, системы автоматического управления летательными аппаратами, системы регулирования ядерных реак- 10 торов и тепловых котлов, системы сушки и т.д.

Цель изобретения — повышение точности работы системы с объектами управления, параметры которых изменяются в широких пределах.

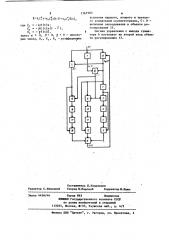

На чертеже представлена блок-"схема предлагаемой системы.

Система содержит блок 1 задержки, первый умножитель 2, первый ин- 2б тегратор 3, первьп усилитель 4, второй умножитель 5, сумматор 6,эталонную модель 7, первый блок сравнения 8, третий умножитель 9, второй интегратор 10 второй усили- 25 тель 11, четвертый умножитель 12, объект регулирования 13, второй блок сравнения 14, пятый умножитель

15, третий интегратор 16, третий усилитель 17 и шестой умножитель 18. 30

Система функционирует следующим образом, На вход объекта регулирования 13 подается входное задающее воздействие f(t), которое объект регулиро- ÇÇ вания 13 должен отработать.Одновременно входное задающее воздействие .< поступает на вход эталонной модели

7 и вход второго блока сравнения l4.

Сигнал с выхода объекта регулирова- 40 ния 13 поступает на вход первого блока сравнения 8, вход блока 1 задержки, входы умножителей 9 и 12.

В блоке 1 задержки происходит задержка сигнала с выхода объекта ре- 45 гулирования 13 на время, равное за-. паздыванию в объекте регулирования

13. На второй вход первого блока сравнения 8 поступает сигнал с выхода эталонной модели 7, который является сигналом отработки моделью

7 входного задающего воздействия

f(t)-. В первом блоке сравнения 8 происходит сравнение сигнала с выхода объекта регулирования 13 и сиг- 55 нала с выхода эталонной модели 7, т.е. вырабатывается сигнал рассогласования Я(С), который подается на

583 г вторые входы умножителей 2, 9, 15.

Сигнал с выхода объекта регулирования 13 также подается на второй вход второго блока сравнения 14, где происходит его сравнение с входным задающим сигналом f(t), т.е. вырабатывается сигнал рассогласования о (t), который подается на входы умножителей 15 и 18. Сигнал с выхода блока 1 задержки поступает на первый вход умножителя 2, где умножается на сигнал рассогласования

E(t). Сигнал с выхода умножителя 2 поступает на вход первого интеграто" ра 3, где интегрируется. Сигнал с выхода первого интегратора 3 поступает на вход первого усилителя, ., где усиливается до необходимой величины. Сигнал с выхода первого усилителя 4 поступает на второй вход умножителя 5, где умножается на сигнал с выхода блока 1 задержки, Сигнал с выхода умножителя 5 подается на первый вход сумматора 6. В умножителе 9 происходит умножение сигнала с выхода объекта регулирования 13 на сигнал рассогласования E(t). Сигнал с выхода умножителя 9 поступает на вход второго интегратора 10, где интегрируется. Сигнал с выхода второго интегратора 10 поступает на вход второго усилителя 11; где усиливается до нужной величины. Сигнал с выхода второго усилителя l1 поступает íà второи вход умножителя 12, где происходит его умножение на сигнал с выхода объекта регулирования 13. Сигнал с выхода умножителя 12 поступает на второй вход сумматора 6. В умножителе 15 происходит умножение сигнала рассогласования 3 (t) на сигнал рассогласования E:(t). Сигнал с выхода умножителя, 15 поступает на вход третьего интегратора 16,. где интегрируется. Сигнал с выхода третьего интегратора 16 поступает на вход третьего усилителя, где усиливается до необходимой величины. Сигнал с выхода третьего усилителя 17 поступает на второй вход умножителя 18 где умножается на сигнал рассогласования

S(t). Сигнал с выхода умножителя 18 поступает на третий вход сумматора

6, где происходит его сложение с сиг. налами с выходов умножителей 5 и 12.

Таким образом, на выходе сумматора

6 получается сигнал управления

167583 э 1

"«ф k СЯх(1-i)+ k>C 3 8 (1) ) Составитель П.Кудрявцев

Редактор С.Тимохин@ - Техред М,йароцай Корректор M. Боже

Тираж 863 Ноднисное

ВНИИПИ Государственного коинтета СССР но делам изобретеы и и открытий

113035, Иосква, Ж-35, Рауиская наб., д. 4/5

Заказ 4436/46

Филиал ПНП "Патент", г. Ужгород, ул. Проектная, 4 где С = — 06E (t)x

c, = — pE (t)x(t — ), c, = — ук(с)6, здесь > О, О, Π— некоторые числа, К, К» К, — коэффициенты усиления первого, второго и третьего усилителей соответственно, +c 0— величина запаздывания в объекте регулирования 13.

Сигнал управления с выхода сумматора 6 поступает на второй вход объекта регулирования 13.