Конвейерное устройство для вычисления тригонометрических функций

Иллюстрации

Показать всеРеферат

КОНВЕЙЕРНОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ТРИГОНОМЕТРИЧЕСКИХ ФУНКЦИЙ, содержащее входной регистр, два блока памяти, два сумматора , четыре промежуточных регистра и выходной регистр, информационный вход которого соединен с выходом первого сумматора , выход старших разрядов входного регистра соединен с вхбдом младших разрядов адреса первого блока памяти и информационным входом первого промежуточного регистра, выход которого соединен с информационным входом второго промежуточного регистра, выход которого соединен с входом младших разрядов адреса второго блока памяти, выход второго сумматора соединен с информационным входом третьего промежуточного регистра , отличающееся тем, что, с целью упрощения устройства, оно содержит квадратор , три триггера и блок синхронизации, причем выход входного регистра соединен с первым входом второго сумматора, второй вход которого соединен с выходом первого блока памяти, вход старшего разряда адреса которого соединен с выходом первого триггера и информационным входом второго триггера, выход которого соединен с информационным входом третьего триггера , выход которого соединен с входом старшего разряда адреса второго блока памяти , выход которого соединен с первым входом первого сумматора, второй вход которого соединен с инверсным выходом четвертого промежуточного регистра со сдвигом на два разряда в сторону старших разрядов, информационный вход которого через квадратор соединен с выходом третьего промежуточного регистра, причем блок синхронизации содержит генератор импульсов, элемент И, регистр сдвига и управляющий триггер, вход синхронизации и прямой выход которого соединены соответственно с прямым выходом генератора импульсов и информационным входом регистра сдвига, установочный вход которого соединен с входом сброса блока синхронизации и установочным входом управляющего триггера, информационный вход которого соединен с выходом элемента И, первый и второй входы которого подключены соответственно к входу пуска блока синхронизации и инверсному выходу управляющего триггера, инверсный выход О5 генератора импульсов соединен свходом 00 синхронизации регистра сдвига, выход тьего разряда которого соединен с входами со синхронизации входного регистра и первого триггера, входы синхронизации первого и третьего промежуточных регистров и второго триггера соединены с выходом пятого разряда регистра сдвига, выход седьмого разряда которого соединен с входами синхронизации второго и четвертого промежуточных регистров и третьего триггера, выход девятого разряда регистра сдвига соединен с входом синхронизации выходного регистра.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1168931 (51)4 G 06 F 7/548

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,", Е

Р

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 3718318/24-24 (22) 06.01.84 (46) 23.07.85. Бюл. № 27 (72) Н. В. Черкасский, В. М. Крищишин и Г. Ф. Криворучко (71) Львовский ордена Ленина политехнический институт им. Ленинского комсомола и Институт прикладных проблем механики и математики АН Украинской ССР (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 907546, кл. G 06 F 7/548, 1980.

Авторское свидетельство СССР № 922734, кл. G 06 F 7/548, 1980. (54) (57) КОНВЕЙЕРНОЕ УСТРОЙСТВО

ДЛЯ ВЫЧИСЛЕНИЯ ТРИГОНОМЕТРИЧЕСКИХ ФУНКЦИЙ, содержащее входной регистр, два блока памяти, два сумматора, четыре промежуточных регистра и выходной регистр, информационный вход которого соединен с выходом первого сумматора, выход старших разрядов входного регистра соединен с вхЬдом младших разрядов адреса первого блока памяти и информационным входом первого промежуточного регистра, выход которого соединен с информационным входом второго промежуточного регистра, выход которого соединен с входом младших разрядов адреса второго блока памяти, выход второго сумматора соединен с информационным входом третьего промежуточного регистра, отличающееся тем, что, с целью упрощения устройства, оно содержит квадратор, три триггера и блок синхронизации, причем выход входного регистра соединен с первым входом второго сумматора, второй вход которого соединен с выходом первого блока памяти, вход старшего разряда адреса которого соединен с выходом первого триггера и информационным входом второго триггера, выход которого соединен с информационным входом третьего триггера, выход которого соединен с входом старшего разряда адреса второго блока памяти, выход которого соединен с первым входом первого сумматора, второй вход которого соединен с инверсным выходом четвертого промежуточного регистра со сдвигом на два разряда в сторону старших разрядов, информационный вход которого через квадратор соединен с выходом третьего промежуточного регистра, причем блок синхронизации содержит генератор импульсов, элемент

И, регистр сдвига и управляющий триггер, вход синхронизации и прямой выход которого соединены соответственно с прямым вы- Я ходом генератора импульсов и информационным входом регистра сдвига, установочный вход которого соединен с входом сброса блока синхронизации и установочным вхо- С дом управляющего триггера, информационный вход которого соединен с выходом эле- ф мента И, первый и второй входы которого подключены соответственно к входу пуска блока синхронизации и инверсному выходу >ь управляющего триггера, инверсный выход генератора импульсов соединен с входом синхронизации регистра сдвига, выход третьего разряда которого соединен с входами CO синхронизации входного регистра и первого триггера, входы синхронизации первого и третьего промежуточных регистров и второго триггера соединены с выходом пятого разряда регистра сдвига, выход седьмого разряда которого соединен с входами синхронизации второго и четвертого промежуточных регистров и третьего триггера, выход девятого разряда регистра сдвига соединен с входом синхронизации выходного регистра.

1168931

Изобретение относится к вычислительной технике и предназначено для использования в универсальных и специализированных вычислительных устройствах при обработке больших массивов данных.

Целью изобретения является упрощение устройства.

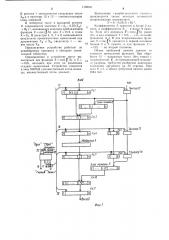

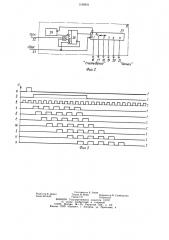

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 — схема блока синхронизации; на фиг. 3 — временные диаграммы работы устройства.

Устройство (фиг. 1) содержит входной регистр 1, блок 2 памяти, сумматор 3, промежуточные регистры 4 и 5, квадратор 6, промежуточные регистры 7 и 8, блок 9 памяти, сумматор 10, выходной регистр 11, триггеры 12 — 14 и блок 15 синхронизации с выходами 16 †.21 и входами 22 и 23.

Блок синхронизации (фиг. 2) содержит генератор 24 тактовых импульсов, элемент И

25, управляющий триггер 26 и сдвиговый регистр 27.

Квадратор может быть выбран любым, обладающим достаточным быстродействием.

В частности, в качестве квадратора может быть использован быстродействующий перем нож ител ь.

Промежуточные регистры 4, 5, 7 и 8 предназначены для кратковременного запоминания результатов промежуточных вычислений и для обеспечения конвейерного способа обработки.

Вычисление функций У = cos(x) от аргумента X(0 «.X (1) и У=ФХ (0,5<Х <1) производится на основе метода сегментной аппроксимации выражением вида У = А— — 0,25(Х+В), где константы А и В выбираются из условия минимизации абсолютной погрешности.

Диапазон изменения аргумента разбивается на интервалы, количество которых определяется требуемой точностью, причем границы интервалов соответствуют К старшим двоичным разрядам аргумента.

На разных интервалах константы А и В имеют различные значения.

Константы В хранятся в блоке 2 памяти, а константы А — в блоке 9 памяти. Адресация к каждому блоку памяти осуществляется по К старшим разрядам аргумента, которые определяют, в каком интервале находится аргумент. Разрядность блоков 2 и 9 памяти определяется требуемой точностью вычисления функций, а разрядность блока

9 памяти больше разрядности входных чисел на один бит, так как константы А имеют целую часть, равную единице.

Устройство работает следующим образом.

Перед началом работы устройства по сигналу «Сброс», поступающему на вход 23 блока 15 синхронизации (фиг.3,а), триггер

26 и сдвиговый регистр 27 устанавливаются в исходное состояние. По сигналу «Пуск» (фиг. Зб), приходящему на вход 22, элемент

И 25 пропускает сигнал с инверсного выхода триггера 26 на информационный вход этого же триггера. Триггер 26 работает в режиме деления частоты генератора 24 тактовых импульсов на два (фиг. 3, в,г). По заднему фронту сигнала генератора 24 информация с выхода триггера 26 заносится в сдвиговый регистр 27. В результате работы устройства на выходах 16 — 21 блока 15 вырабатывается «лесенка» импульсов управления внутренних регистров устройства и внешних схем памяти. При этом выход 16 «Считывание» (фиг Зд) используется для управления считыванием очередного слова данных из внешней памяти, выход 17 (фиг. Зе) — для управления занесением числа в регистр 1 и триггер 12, выход 18 (фиг. фк) для управления занесением числа в регистры 4 и 5 и триггер 13, выход 19 (фиг. Зз) — для управления занесением чисел в регистры 7 и 8 и триггер 14, выход 20 (фиг. Зи) — для управления занесением числа в регистр ll, а выход 21 «Запись» — для управления записью результата во внешнюю память.

После снятия сигнала «Пуск» блок 15 синхронизации прекращает вырабатывать сигналы управления, начиная с верхних ступеней конвейера.

Таким образом, обеспечивается корректное завершение обработки операндов, находящихся во внутренних регистрах устройства во время снятия сигнала «Пуск».

В первом такте работы устройства в регистр 1 поступает аргумент Х, а в триггер

12 — код операции КОП. С выхода регистра 1 значение аргумента Х поступает на сумматор 3. Одновременно из блока 2 памяти по адресу, указанному К старшими разрядами аргумента Х, и кодом операции, выбирается константа В, и также поступает на сумматор 3. В сумматоре 3 вырабатывается сумма Х +В,.

Во втором такте Х +В записывается в регистр 4 и возводится в квадрат в блоке 6.

В том же такте значение К старших разрядов аргумента Xi записывается в регистр 5, сигнал КОП переписывается в триггер 13, в регистр 1 поступает следующее значение аргумента Х, а в триггер 12 — новый сигнал кода операции КОП.

В третьем такте значение (Х +В ) записывается в регистр 7 и с инверсных выходов этого регистра поступает на вход сумматора 10 со сдвигом на два разряда вправо.

Одновременно в регистр 8 переписывается из регистра 5 значение К старших разрядов аргумента Х, а в триггер 14 из триггера 13— сигнал кода операций КОП. Содержимое триггера 13 и регистра 8 образует адрес константы А . Эта константа поступает из блока 9 памяти на второй вход сумматора 10, где и производится выработка значения А —

0,25(Х,+В ) . В этом же такте в регистр 4 записывается значение Х +В, а в регистр 5— значение К старших разрядов аргумента Х .

116893) гггр Г иггер 13

flyc

22 баггер И! б

Сч

В регистр 1 записывается следующее число

X>,а в триггеры 12 и 13 — соответствующие коды операций.

В четвертом такте в выходной регистр

11 записывается значение У =А вЂ,25(X +

+ В ), являющееся искомым приближением функции У=cos(X) или У=th-Х, в точке

Х=Х . В регистры 4, 5, 7 и 8 записываются результаты промежуточных вычислений над аргументами Х> и Х>, as регистр 1 — новое число Х .

Предлагаемое устройство работает по конвейерному принципу и обладает значительной гибкостью.

Одновременно в устройстве могут вычисляться две функции Y = cos(X) и У =

= ФХ, находясь при этом на различных стадиях вычисления. Устройство относится к типу МКМД (множественный поток команды, множественный поток данных).

Вычисление гиперболического тангенса производится также методом сегментной аппроксимации выражением

У =А — 0,25(Х+ В) .

Коэффициенты А хранятся в блоке 2 lIaмяти, а коэффициенты  — в блоке 9 памяти. Если код операции У= cos(+X) равен

«О», а код операции Y = thX — «1»,.то коэффициенты А и В для аппроскимации функции У =сов — Х хранятся в первой половине

% 4 блоков 2 и 9 памяти, а для функции Y=

= thX — во второй половине.

Объем требуемой памяти зависит от точности вычислений функций. При обработке 15 — разрядных чисел (без знака) с погрешностью Я, не превышающей младшего разряда, требуется разбиение диапазона изменения аргумента на 32 отрезка. При этом К=5, а объем требуемой памяти равен

1984 бит.

1168931

Фиг. Я

Редактор В. Данко

Заказ 4614/42

Р д

Г

1 е

Ж

Ll

1á 17 «/8 19 20 21

"СцИ пы5иииЕ" Запись

Составитель А. Зорин

Техред И. Верес Корректор М. Самборская

Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5 филиал ППП «Патент», r. Ужгород, ул. Проектная, 4