Сигнализатор наличия пламени

Иллюстрации

Показать всеРеферат

1. СИГНАЛИЗАТОР НАЛИЧИЯ ПЛАМЕНИ, содержащий фотоприемник, выход которого через последовательно соединенные усилитель и вход детектора соединен с первыми входами первого и второго ключей, выходы которых соединены с первыми входами соответственно первого и второго запоминающих блоков, блок управления , первый, второй, третий, четвертый вы-ходы которого соединены соответственно с вторыми входами первого и второго ключей и первого и второго запоминающих блоков. сумматор, отличающийся тем, что, с целью расширения динамического диапазона измерений и повыщения помехозащищенности сигнализатора, в него введены буферный каскад, делитель напряжения на первом и втором резисторах, блок обработки информации и третий и четвертый ключи, первые входы которых соединены с выходами соответственно первого и второго запоминающих 6.ЛОКОВ, вторые - с вторым и первым выходами блока управления соответственно, а выходы - с входом буферного каскада, выход которого соединен с входом делителя напряжения, выход которого соединен с первым входом сумматора, выход которого соединен с первым входом блока обработки инi формации, второй вход сумматора соединен с выходом усилителя и входом блока управ (Л ления, пятый выход которого соединен с вторым входом блока обработки информации, выход которого является выходом устройства .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

G 08 В 17/12 (59 +

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3708335/24-24 (22) 28.12.83 (46) 23.07.85. Бюл. № 27 (72) И. В. Милашенко, Г. П. Попов, А. Ю. Романенко и И. В. Северин (53) 654.9 (088.8) (56) Заявка ФРГ № 2108296, кл. 74а, 33, опублик. 1972.

Заявка ФРГ № 2051640, кл. 74а, 33, опублик. 1972. (54) (57) 1. СИГНАЛИЗАТОР НАЛИЧИЯ

ПЛАМЕНИ, содержащий фотоприемник, выход которого через последовательно соединенные усилитель и вход детектора соединен с первыми входами первого и второго ключей, выходы которых соединены с первыми входами соответственно первого и второго запоминающих блоков, блок управления, первый, второй, третий, четвертый вы-ходы которого соединены соответственно с вторыми входами первого и второго ключей и первого и второго запоминающих блоков, „„яц„„68992 д сумматор, отличающийся тем, что, с целью расширения динамического диапазона измерений и повышения помехозащищенности сигнализатора, в него введены буферный каскад, делитель напряжения на первом и втором резисторах, блок обработки информации и третий и четвертый ключи, первые входы которых соединены с выходами соответственно первого и второго запоминающих блоков, вторые — с вторым и первым выходами блока управления соответственно, а выходы — с входом буферного каскада, выход которого соединен с входом делителя напряжения, выход которого соединен с первым входом сумматора, выход которого соединен с первым входом блока обработки информации, второй вход сумматора соединен у с выходом усилителя и входом блока управления, пятый выход которого соединен с вторым входом блока обработки информации, выход которого является выходом устройства. \

I I 68992

2. Сигнализатор по п. 1, отличающийся тем, что блок обработки информации выполнен на первом и втором счетчиках, элементе

И, инверторе, первом и втором резисторах, первом и втором конденсаторах, счетный вход первого счетчика является первым входом блока, выход первого счетчика соединен с первым входом элемента И, выход которого является выходом блока обработки информации, счетный вход второго счетчика является вторым входом блока, выход второго счетчика через первый конденсатор соединен с вторым входом элемента И, с первым выводом первого резистора и с входом инвертора, выход которого через второй конденсатор соединен с объединенными входами установки в «О» первого и второго счетчиков и с первым выводом второго резистора, входы запрета первого и втоИзобретение относится к пожарной сигнализации.

Цель изобретения — расширение динамического диапазона измерения и повышения помехозащищенности устройства. 5

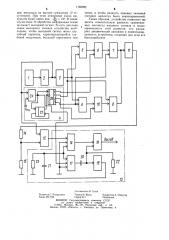

На чептеже приведена функциональная схема устройства.

Оно содержит фотоприемник 1, селективный усилитель 2, детектор 3, блок 4 управления, электронные ключи 5 — 8, запоминающие блоки 9 и 10, буферный каскад 11, сумматор 12 и блок 13 обработки информации, резисторы 14 и 15 делителя напряжения.

Блок 13 обработки информации может 15 содержать счетчики 16 и 17, элемент И 18, инвертор 19, конденсаторы 20 и 21 и резисторы 22 и 23.

Блок 4 управления может состоять из компаратора 24, триггера 25 и дешифратора

26. Один из входов компаратора 24 служит входом блока 4 управления, а на второй вход компаратора подается опорное напряжение U (нулевой уровень), которое из соображений повышения помехозащищенности выбрано равным 0,1 В. Выход компаратора 24 соединен со счетным входом триггера 25, с входом первого разряда дешифратора 26, а также служит выходом 5 блока 4 управления. Выход триггера связан с входом второго разряда дешифратора 26, выходы 1 — 4 которого являются выходами блока 4 уп р а влени я. рого счетчиков и вторые выводы первого и второго резисторов соединены с общим проводом.

3. Сигнализатор по п. 1, отличающийся тем, что, блок управления выполнен на дешифраторе, триггере и компараторе, первый вход которого является входом блока управления, а выход — пятым выходом блока управления и соединен с первыми входами дешифратора и триггера, инверсный выход которого соединен с вторым входом триггера, прямой выход которого соединен с вторым входом дешифратора, первый, второй, третий, четвертый выходы которого являются соответственно первым, вторым, третьим, четвертым выходами блока управления, второй вход компаратора соединен с клеммой опорного напряжения.

Схема работает следующим образом.

При возникновении мерцающего пламени на выходе фотоприемника 1 появляется электрический сигнал, который поступает на вход селективного усилителя 2, работающего в заданном диапазоне частот мерцания (например, 2 — 20 Гц). С выхода усилителя 2 сигнал поступает на вход блока 4 управления, на первый вход сумматора 12 и выпрямленный детектором 3 — на первые входы электронных ключей 5 и 6. Блок 4 управления предназначен для формирования импульсов, управляющих работой электронных ключей 5 — 8 и запоминающих блоков 9 и 10, а также для формирования цикла измерения. С приходом первой положительной полуволны с выхода усилителя 2 на вход блока 4 управления в компараторе 24 происходит сравнение величины этого сигнала с заданным нулевым уровнем 0,1 В (U<>Q. В случае превышения входным сигналом нулевого уровня компаратор 24 формирует выходной импульс, который, поступив на вход дешифратора 26, вызовет появление на его выходе, соответствующем выходу 1 блока 4 управления, уровня логической единицы, приводит к замыканию электронных ключей 5 и 8, чем обеспечивается запись пикового значения амплитуды сигнала с выхода пикового детектора 3 через электронный ключ 5 в запоминающий блок 9 и подключение выхода запоминающего устройства 10 через электронный ключ 8, буферный каскад 11 и делитель, состоящий из резисторов 14 и 15, к второму входу сумматора 12.

ll з

По заднему фронту сформированного компаратором 24 импульса триггер 25 устанавливается так, что на его выходе появляется уровень логической единицы, при этом дешифратор 26 формирует уровень логической единицы на выходе 1 блока 4 управления. Появление логической единицы вызывает обнуление запоминающего блока

10 управления устройства. В момент прихода второй положительной полуволны с выхода усилителя 2 компаратор 24 формирует выходной им пульс, что соответствует появлению на первом и втором входах дешифратора уровень логической единицы, в результате чего дешифратор формирует уровень логической единицы на выходе 2 блока 4 управления, что приводит к замыканию электронных ключей 6 и 7, чем обеспечивается запись пикового значения амплитуды с выхода детектора 3 на запоминающий блок 10 и подключение выхода запоминающего блока 9 через буферный каскад 11 и делитель, состоящий из резисторов 14 и 15, к второму входу сумматора 12. По заднему фронту импульса на выходе компаратора 24 триггер

25 устанавливается в состояние, соответствующее появлению уровня логичеСкого нуля на его выходе. При этом дешифратор 26 переходит в состояние, соответствующее появлению уровня логической единицы на выходе 3 блока 4 управления, чем обеспечивается обнуление запоминающего устройства 9. При поступлении последующих положительных амплитуд с выхода усилителя 2 цикл работы блока 4 управления повторяется.

Буферный каскад 11 предназначен для обеспечения работы запоминающего устройства 9 и 10 на низкоомную нагрузку — делитель. Делитель напряжения на резисторах 14 и 15 предназначен для задания порогового значения глубины модуляции входного сигнала, при превышении которого сумматор 12 формирует выходной сигнал.

Таким образом, сумматор 12 в момент прихода первой положительной полуволны сигнала на выходе усилителя 2 сравнивает по амплитуде два сигнала: выходной сигнал усилителя 2 и сигнал с выхода запоминающего устройства 10.

При выполнении условия — Π— ) "г (1), где U< — измеряемая амплитуда, U> — записанное в запоминающем блоке значение, предыдущей амплитуды; — коэффициент, задающий пороговую глубину модуляции, сумматор 12 формирует сигнал, который записывается на счетчик 16. При этом сигнал с выхода 5 блока 4 управления, соответствующий переходу входным сигналом нулевого уровня, записывается на счетчик

17.

В момент прихода второй положительной полуволны сумматор 12 сравнивает ее амплитудное значение со значением преды68992

5

20 душей амплитуды с выхода запоминающего устройства 9.

Таким образом, на входах сумматора 12 сравниваются сигналы с выхода усилителя

2 и записанное в памяти значение предыдущей амплитуды с коэффициентом, учитывающим пороговую глубину модуляции, заданную делителем на резисторах 14 и 15. При выполнении условия (1) сумматор 12 также формирует выходной сигнал записи на счетчик 16. Если условие (1) не выполняется, то сигнал с выхода сумматора 12 отсутствует

По окончании второй положительной полуволны входного сигнала блок 4 управления переводит запоминающий блок 9 в нулевое положение, подготавливая его для записи третьей полуволны входного сигнала. Таким образом, и роисходит обработка си гн ала в течение цикла измерения. В предлагаемом варианте сигнализатора цикл измерения задан количеством сравниваемых амплитуд входного сигнала, в данном случае — четырьмя амплитудами. По окончании четвертой амплитуды с выхода счетчика 17 дифференцирующей цепью, состоящей из конденсатора

20 и резистора 22, <формируется импульс разрешения на выдачу информации с выхода счетчика 16. Сигнал с выхода счетчика 16 пройдет через элемент И 18 в том случае, когда за цикл измерения отношения числа импульсов, накопленных счетчиком 17, к числу импульсов с выхода счетчика 16 будет больше 1,2. Коэффициент 1,2 выбран из соображений улучшения помехозащищенности сигнализатора.

Дифференцированный импульс с выхода счетчика 17 инвертируется инвертором 19 и дифференцируется цепью, состоящей из конденсатора 21 и резистора 23. Этот импульс предназначен для обнуления счетчиков 16 и

17, чем обеспечивается подготовка их к новому циклу измерения. Таким образом, устройство обработки информации производит сравнение импульсов с выхода блока 4 управления и с выхода сумматора 12. Выходной сигнал формируется лишь в том случае, когда выполняется условие (1), т.е. сигнал на входе устройства знакопеременен и глубина модуляции его больше заданной.

Знакопеременность выражается в отличии числа импульсов на выходе счетчика

16 (n ) от числа импульсов на выходе счетчика 17 (n ). Так, при воздействии на вход устройства регулярного сигнала или сигнала с нарастающей амплитудой отношение числа импульсов — = 1, поскольку каждый последующий импульс больше или равен предыдущему. При воздействии на вход сигнализатора сигнала с убывающей амплитудой если разность пиковых значений соседниi амплитуд больше заданной глубины модуля1168992

5 ции, импульсы на выходе сумматора 12 отсутствуют. При этом отношение числа импульсов будет иметь вид: — L = CO. В таком случае блок 13 обработки информации также не выдаст выходной сигнал. То есть для появления выходного сигнала устройства необходимо, чтобы выходной сигнал носил случайный характер, характеризующийся глубиной модуляции, большей порогового значения, и чтобы разность пиковых значений соседних амплитуд была знакопеременной.

Таким образом, устройство позволяет выделять относительную разность сравниваемых амплитуд входного сигнала и знакопеременность этой разности, что расширяет динамический диапазон и помехозащищенность устройства, сохранив при этом его быстродействие.

Составитель В. Гусев

Редактор С. Патрушева Техред И. Верес Корректор А. Обручар

Заказ 4617 45 Тираж 611 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4