Устройство для подключения блоков памяти к источнику питания

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ БЛОКОВ ПАМЯТИ К ИСТОЧНИКУ ПИТАНИЯ, содержащее первую и вторую группу элементов И, причем первый вход каждого элемента И первой группы соединен с первым входом соответствующего элемента И второй группы и является соответствующим входо.м первой группы устройства, первую и вторую группы триггеров , причем S-вход каждого триггера первой группы соединен с выходом соответствующего элемента И первой группы, а S-вход каждого триггера второй группы соединен с выходом соответствующего элемента И второй группы, первую -и вторую группы ключей, причем выход каждого ключа первой группы соединен с выходом соответствующего ключа второй группы, выводом питания соответствующего триггера первой и второй группы и является соответствующим выходом устройства, выход каждого из триггеров первой и второй групп соединен с входом соответствующего ключа второй группы, отличающееся тем, что, с целью снижения потребляемой устройством мощности. Оно содержит дешифратор и дополнительный ключ, выход которого подключен к входам ключей первой группы, выводам питания элементов И первой и второй групп и выводу питания дешифратора, входы которого являются входами второй группы устройства, вход с дополнительного ключа является управляющим входом устройства, выходы дешифра (Л тора соединены с вторым входом соответствующего элемента И первой и второй групп. R-вход каждого триггера первой группы соединен с S-в.ходом соответствующего триггера второй группы, R-вход каж- 3 дого триггера второй группы соединен с S-входом соответствующего триггера первой группы. о: со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„„Я1) „„1169019 с!!,, G 11 С 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3695734/24-24 (22) 20.01.84 (46) 23.07.85. Бюл. № 27 (72) В. Г. Псарев, К. Р. Бурик, А. И. Кись и B. П. Тищенко (53) 681.327.6 (088.8) (56) Авторское свидетельство СССР № 781973, кл. G 11 С 11/00, 1978.

Авторское свидетельство СССР № 888205, кл. G 11 С 11/00, 1980. (54) (57) УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ БЛОКОВ ПАМЯТИ К ИСТОЧНИКУ ПИТАНИЯ, содержащее первую и вторую группу элементов И, причем первый вход каждого элемента И первой группы соединен с первым входом соответствующего элемента И второй группы и является соответствующим входом первой группы устройства, первую и вторую группы триггеров, причем S-вход каждого триггера первой группы соединен с выходом соответствующего элемента И первой группы, а S-вход каждого триггера второй группы соединен с выходом соответствующего элемента И второй группы, первую и вторую группы ключей, причем выход каждого ключа первой группы соединен с выходом соответствующего ключа второй группы, выводом питания соответствующего триггера первой и второй группы и является соответствующим выходом устройства, выход каждого из триггеров первой и второй групп соединен с входом соответствующего ключа второй группы, отличающееся тем, что, с целью снижения потребляемой устройством мощности, OHQ содержит дешифратор и дополнительный ключ, выход которого подключен к входам ключей первой группы, выводам питания элементов И первой и второй групп и выводу питания децшфратора, входы которого являются входами второй группы устройства, вход дополнительного ключа является управляющим входом устройства, выходы ден ифратора соединены с вторым входом соответствующего элемента И первой и второй груши R-вход каждого триггера первой группы соединен с S-входом соответствующего триггера второй группы, R-вход каждого триггера второй группы соединен с

S-входом соответствующего триггера первой группы.

1169019

Составитель Г. Бородин

Техред И. Верес Корректор В. Бутяга

Тираж 584 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4

Редактор И. Николайчук заказ 4620 46

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано при разработке вычислительных машин параллельного действия, к которым предъявляются требования повышенных надежности, ресурса и экономичности.

Целью изобретения является снижение потребляемой устройством мощности.

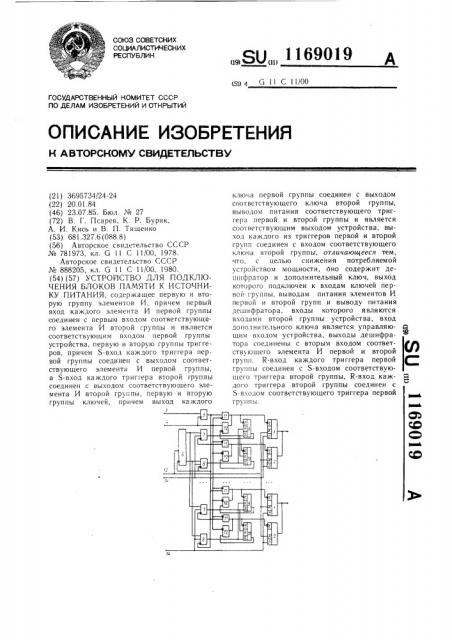

На чертеже представлена функциональная схем а устройства для переключения блоков памяти.

Схема содержит основные 1 и дополнительные 2 блоки памяти, управляющий вход 3 устройства, шину 4 питания, дополнительный ключ 5, дешифратор 6, элементы И 7 первой группы, элементы И 8 вто ",кг","! 9 пс )во" группы, триггеры 10 второй группы, ключи 11 первой группы, ключи 2 второй группы, адресные входы 13 и входы 14 устройства.

Устройство может работать в трех режимах: с основными блоками 1 памяти; с дополнительными блоками 2 памяти; с замещением отказавших основных 1 на дополнительные 2 блоки памяти (количество замешенных разрядов 1 — Il, где п — количество разрядов).

При подготовке к работе питание с шины 4 подастся на ключи 5, 11 и 12. При наличии сигнала на входе 3 питание через ключ 5 подается на элементы И 7 и 8 и дешифратор 6. Одновременно сигнал с выхода ключа 5 поступает на входы ключей 11.

Питание подается на триггеры 9 и блоки 1 и трип ерь. 10 и блоки 2.

Для установки устройства в режим работы с блоками 1 по входам 14 подается код 1! I ... I. а по входу 13 — фиксированный адрес ФЛ I. При этом на первом выходе дешифратора 6 образуется разрешающий сигнал. а на втором — запрещающий.

Сигнал с выхода элемента И устанавливает тр :!l .,ы 9 в единичное состояние, а триггеры 10 — — в нулевое. Выходной сигнал триг. < в 9 открывает кл1очи 2, и через

40 них питание с шины 4 подается на триггеры 9 и блоки 1. После этого сигнал с выхода 13 снимается, ключ 5 отключает питание с дешифратора 6 и элементов И 7 и 8 и снимает управляющие сигналы с ключей 11.

Для установки устройства в режим работы с блоками 2 по входам 14 также подается код 111...11, а по шине 13 — фиксированный адрес ФА2. При этом на первом выходе дешифратора 6 образуется запрещающий сигнал, а на втором — разрешающий. Выходной сигнал элементов И 8 устанавливает триггеры 9 в нулевое состояние, а триггеры 10 — в единичное. Выходной сигнал триггеров 10 открывает ключи 12, и питание с шины 4 через ключи 2 подается на триггеры 10 и блоки 2. После этого управляюгций сигнал с входа 3 снимается, ключ 5 отключает питание с дешифратора 6 и элементов И 7 и 8, управляющие сигналы с ключей 11 и 12 снимаются, и они отключаются, и питание на триггеры 9 и блок 1 не подается. Триггеры 10 и блок 2 остаются запитанными через соответствующие ключи 12.

Для установки устройства в режим замещения его переводят сначала в режим работы с блоками 1, затем по входу 3 подается управляющий сигнал, а по входам 14 — код с единицами в тех разрядах, в которых необходимо провести замещение блока 1 на блок 2. После этого на вход 13 поступает ФА2, образующий разрешающий сигнал на втором выходе дешифратора 6.

Выходной сигнал тех элементов И 8, которые определены единицами по входам 14, изменяет состояние триггеров 9 на нулевое, а триггеров 10 — на единичное. Выходные сигналы триггеров 10 открывают клкзчи 12, а трип еров 9 — закрывают ключи 12 соответствующих разрядов. После снятия сигнала с входа 13 прекращается подача питания на дешифратор 6 и элементы И 7 и 8, в замещенных разрядах питание на триггеры 10 и блок 2 подается через соответствующие ключи 12.