Цифровое устройство для управления широтно-импульсным регулятором переменного напряжения

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я(/„„ 1169110 (513 } 11 0 > М 5/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ „

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ 21 } 3699339/24-07 (22) 08.02.84 (46) 23.07.85. Бюл. ¹ 27 (72) A. В. Абрамов, В. M. Яров, В. A. Гордеев, В. Г. Герасимов и С. П. Игнатьев (71) Чувашский государственный университет им. И. H. Ульянова (53) 621.316.727 (088.8) (56} Авторское свидетельство СССР .х 877784, кл. Н 02 P 13/30, 1981.

Специальные вопросы электротермии

ЧГУ. Чебоксары, !981, с. 95 -97. (54) (57) ЦИФРОВОЕ УСТРОИСТВО ДЛЯ

У11РАВЛЕНИЯ ШИРОТНО-ИМПУЛЬСНЫМ РЕГУЛЯТОРОМ ПЕРЕМЕННОГО

НАПРЯЖЕНИЯ, содержащее датчик фазы напряжения с пятью выходами, соответствующими прямоугольным импульсам, совпадающим с положительными и отрицательными полуволнами синусоиды напряжения сети и с второй половиной каждого полупериода, и коротким импульсам в моменты времени соответствующие фазе сетевого напряжения

90 и 270 эл. град., пятый выход подключен к входу генератора тактовых импульсов, четвертый выход — к входу двоичного счетчика, преобразователь напряжение — частота, выход которого через первый формирователь импульсов подключен к одному из входов элемента совпадения, к другому входу которого через первый ключ подключены выход второго формирователя и пятый выход датчика фазы напряжения, выходной усилитель, к входу которого подключен блок согласования, один из входов второго ключа через третий формирователь импульсов подключен к выходу двоичного счетчика, другой вход через второй формирователь импульсов к выходу генератора тактовых импульсов, отличаяи(ееея тем, что, с целью улучшения энергетических показателей и повышения надежности регулятора, оно снабжено блоком фазирования, первый вход которого подключен к выходу первого ключа, второй, третий и четвертый входы подклк>чсны к первому, второму и третьему выходам датчик; > фазы напряжения, пятый вход подключен к выходу Второго ключа>, выход — и входу блока согласования, при этом блок фазирования содержит Tpw элс мента И вЂ” НЕ 11 один элемент И вЂ” ИЛИ вЂ” HE, первый и второй входы второго элемента И вЂ” НЕ являются первым и вторым входами блока фазирования, к второму входу третьего элемента

И вЂ” HE подключены третьи входы первого и второго элементов И вЂ” HE, к третьему входу подключен первый вход первого элемента ИНЕ, к четвертому входу — - первый вход элемента И вЂ” ИЛИ вЂ” -НЕ, второй, третий и четвертый входы третьего элемспr;> И-- HI . являются третьим, четвертым и пятым входами блока фазирования, выход первого элемента И вЂ” HE через первый формирователь импульсов по фронту входного сигнала соединен с входами S» R первого и второго триггеров и через первый элемент HF -- с вторым входом элемента И вЂ” ИЛИ--НЕ, третий и четвсртый входы которого подключены к прямому выходу второго триггера и к пер вому входу третьего элемента И вЂ” НЕ, выход которого соединен с входом S третьего триггера, инверсный выход которого через третий формирователь импульсов по фронту входного сигнала соединен с входом R псрвого триггера, инверсный выход которого подключен к третьему входу первого элемента И вЂ” НЕ, прямой выход третьего триггера соединен с пятым входом элемента

И вЂ И---HE, шестой вход которого через второй элемент HE подключен к выходу второго элемента И вЂ” НЕ, к входу R третьего триггера и к входу второго формирователя импульсов по фронту входного сигнала, выход которого соединен с входом S второго триггера, инверсный выход которого подключен к седьмому и восьмому входам элемента И вЂ” ИЛИ вЂ” HE, выход которого является выходом блока фазирования.

1169110

Изобретение относится к электротехнике в частности к регулированию напряжения и мощности электрических печей сопротивления, включаемых в сеть через трансформатор с помощью встречно-параллельно соединенных тиристоров.

Цель изобретения — улучшение энергетических показателей и повышение надежности регулятора.

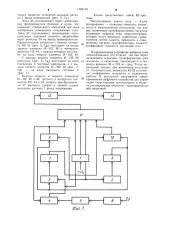

На фиг. 1 приведена функциональная схе- 10 ма предлагаемого устройства с цифровой системой широтно-импульсного управления; на фиг. 2 и 3 — принципиальные схемы блоков системы управления; на фиг. 4 и 5— временные диаграммы.

Цифровое устройство содержит датчик

1 фазы напряжения, генератор 2 тактовых импульсов, двоичный счетчик 3, элемент 4 совпадения, формирователи 5 — 7 импульсов, преобразователь 8 напряжение — частота, ключи 9 и 10, блок 11 фазирования, блок 12 согласования и выходной усилитель 13.

Предположим, что система управления должна обеспечить подключение нагрузки на время, равное двум периодам питающей сети, а весь период регулирования содержит четыре периода напряжения сети. Период ре гулирования задается генератором 2 тактовых импульсов, представляющим собой двоичный счетчик, пересчитывающий импульсы с фазовым углом 270 эл. град. (фиг. 1)

С преобразователя 8 напряжение — частота в двоичный счетчик 3 через элемент 4 совпадения поступает число импульсов, соответствующее периодам напряжения сети, которые необходимо пропустить к нагрузке.

Преобразование напряжения задания U> в число импульсов осуществляется в прямом коде. Меньшему напряжению задания Uz соответствует меньшее число импульсов (за интервал времени tz — gz, фиг. 4) на выходе преобразователя. Эти импульсы поступают в двоичный счетчик 3 за время t> — tg (фиг. 4). Импульсами, соответствующими фазе сетевого напряжения 90 эл. град., которые поступают с второго выхода датчика

1 фазы напряжения двоичный счетчик 3 доводится до полного заполнения. После заполнения двоичного счетчика 3 сигнал с его выхода через третий формирователь 7 импульсов размыкает второй ключ 10 (момент 1 ), разрешающий работу выходного усилителя 13, а блок 11 фазирования выдает этот сигнал с задержкой на 180 эл.град. с фазовым углом 270 эл. град. (момент tq, фиг. 4). По приходу четвертого импульса с первого выхода датчика 1 фазы напряжения генератор 2 тактовых импульсов выдает импульс запрета (момент ty-), закрывающий второй ключ 10, и блок 12 согласования запрещает работу выходного усилителя 13.

Двоичный счетчик 3 устанавливается в нулевое состояние, а первый ключ 9 замыка15

55 ется. Весь цикл работы двоичного счетчика 3 начинается сначала.

На выходе блока 11 фазирования сигнал на выключение появляется с задержкой на

180 эл. град. (момент t<). После перехода напряжения питающей сети через нуль блок

11 фазирования с задержкой на 90 эл. град. выдает сигнал на кратковременное ювторное включение выходного усилителя 13 с фазовым углом 270 эл. град. (момент t ). В момент времени нагрузка отключается от питающей сети.

Следующий цикл работы регулятора начинается с фазовым углом 90 эл.град. (момент ty), после прихода импульса с выхода двоичного счетчика 3. В момент времени tio генератор 2 тактовых импульсов запрещает работу выходного усилителя. Нагрузка отключается от питающей сети. После перехода напряжения питающей сети через нуль блок 11 фазирования с задержкой на 90 эл. град. выдает сигнал на кратковременное повторное включение выходного усилителя 13 с фазовым углом 90 эл. град. (момент tyi).

Таким образом, блок 11 фазирования формирует угол задержки момента включения выходного усилителя 13 в первом периоде каждого интервала включенного состояния поочередно величиной 90 и 270 эл. град. (моменты t, t9, ty2), а после окончания интервала включенного состояния кратковременно повторно включает выходной усилитель 13 с задержкой момента повторного включения на 90 эл. град. относительно последнего момента перехода напряжения питающей сети через нуль на интервале включенного состояния (моменты 1, 1,tyy, tyy )

Электрическая схема блока фазирования (фиг. 2) имеет трехвходовые элементы И—

HE 14 и 15, четырехвходовой элемент И—

НЕ 16, формирователи 17 — 19 импульсов по фронту входного сигнала, элементы HE

20 и 21, RS-триггеры 22 — 24, восьмивходовой элемент И вЂ” ИЛИ вЂ” НЕ 25.

Блок фазирования работает следующим образом.

Предположим, что в момент времени ts (фиг. 5) генератор 2 тактовых импульсов выдает импульс запрета, закрывающий второй ключ 10, с выхода которого уровень логического нуля поступает на третий вход третьего элемента И вЂ” НЕ 16 и восьмой вход элемента И вЂ” ИЛИ вЂ” НЕ 25. При этом на выходе последнего появляется уровень логической единицы, запрещающий работу выходного усилителя 13. В момент времени

t> уровень логической единицы устанавливается одновременно на всех входах второго элемента И вЂ” НЕ 15, поступающий с выхода первого ключа 9, с третьего и четвертого выходов датчика 1 фазы напряжения. На выходе второго элемента И вЂ” НЕ 15 появляется уровень логического нуля, который ин. вертируется вторым элементом НЕ 21 и по1169110 ступает на пятый вход элемента И вЂ” ИЛИ—

HE 25, с выхода которого низкий логический уровень разрешает работу выходного усилителя 13 с фазовым углом 90 эл. град. В момент t второй элемент И вЂ” НЕ 15 закрыЬ 5 вается уровнем логического нуля, поступающим с третьего и четвертого выходов датчика 1 фазы напряжения, на его выходе устанавливается уровень логической единицы.

При этом элемент И вЂ” ИЛИ вЂ” НЕ 25 запрещает работу выходного усилителя 13, а на выходе второго формирователя 18 импульсов по фронту входного сигнала формируется короткий импульс, который устанавливает

25 второй триггер 23 в единичное состояние.

Импульсами с фазовым углом 90 эл. град., которые поступают от датчика 1 фазы напряжения, двоичный счетчик 3 доводится до полного заполнения.

После заполнения двоичного счетчика

3 сигнал с выхода третьего формирователя

7 импульсов размыкает второй ключ 10 (мо мент tz), на выходе которого появляется уровень логической единицы. В момент времени t4 одновременно на всех входах третьего элемента И вЂ” НЕ 16 устанавливается уровень логической единицы, поступающий с неинверсного выхода второго триггера 23, с четвертого и пятого выходов датчика 1 фазы напряжения и с выхода ворого ключа

10. Короткие импульсы с выхода третьего элемента И вЂ” НЕ 16 устанавливают третий триггер 24 в единичное состояние. При этом на выходе элемента И вЂ” ИЛИ вЂ” НЕ 25 появляется уровень логического нуля, который разрешает работу выходного усилителя 13 с фазовым углом 270 эл. град.

Очередным импульсом запрета (момент t>) генератор 2 тактовых импульсов закрывает второй ключ 10, на выходе которого появляется уровень логического нуля, запрещающий работу выходного усилителя

13, а на выходе элемента И вЂ” ИЛИ вЂ” НЕ 25 этот сигнал (уровень логической единицы) появляется в момент времени t6, когда короткий импульс с выхода второго элемента

И вЂ” НЕ 15 возвращает третий триггер 24 в нулевое состояние. Одновременно с этим короткий импульс с выхода формирователя 19 импульсов по фронту входного сигнала устанавливает триггер 22 в единичное состояние.

В момент времени t одновременно на всех входах первого элемента И вЂ” НЕ 14 устанавливается уровень логической единицы, поступающий с четвертого и пятого выходов датчика 1 фазы напряжения с инверсного выхода первого триггера 22. На выходе первого элемента И вЂ” НЕ 14 появляется уровень логического нуля, который инвертируется первым элементом НЕ 20 и поступает на первый вход элемента

И вЂ” ИЛИ вЂ” HE 25, с выхода которого уровень логического нуля разрешает работу

55 выходного усилителя с фазовым уг,н>м

270 эл. град. В момент tg первый элемент

И вЂ” HE 14 закрывается уровнем логического нуля, поступающим с четвертого и пятого выходов датчика 1 фазы напряжения. и на выходе устанавливается уровень логич< ской единицы. При этом элемент И вЂ” ИЛИ--1!Е

25 запрещает работу выходного усил;<толя

13, а первый формирователь !7 импульсов по фронту входного сигнала своим кз ротким импульсом возвращает первый и второй триггеры 22 и 23 в исходное состоянне.

Следующий цикл работы регулятора начинается с фазовым углом 90 эл. град. (момент ty) .

Принципиальная схема датчика 1 фазы напряжения, формирующего прямоугольные импульсы, совпадающие с положительными и отрицательными полуволнами синусоиды напряжения сети, а короткие импульсы в моменты времени, соответствующие фазе сетевого напряжения 90 и

270 эл. град., приведена на фиг. 3. Датчик

1 фазы напряжения содержит двухполупериодный выпрямительный мост 26, резис торы 27-34, стабилитрон 35, диоды 36 и 37, конденсатор 38, однопереходный транзистор

39, транзистор 40, инверторы 41 — 44, формирователь 45 прямоугольных импульсов по фронту входного сигнала, преобразова тели 46 и 47 высокого логического уровня в низкий, логические элементы И--НЕ 48 и 49.

Датчик 1 фазы напряжения работас следующим образом.

Напряжение синхронизации пост пае! на входы выпрямительного моста 26 и формирователя импульсов на транзисторе 40, элементах НЕ 43 и 44, рсзилорах 30--31, диодах 36 37. После двухполупериодного выпрямления напряжения синхронизации мостом 26 пульсирующее напряженис с удвоенной частотой промышленной сети поступает на вход релаксационного генератора на однопереходном транзисторе 39, резисторах 27 — 29, стабилитроне 35 и конденсатор

38. С базы однопереходного транзистора

39 прямоугольные импульсы, задние фронты которых соответствуют моментам времени

90 и 270 эл. град., поступают на вход первого элемента HE 41, с выхода которого сигнал поступает на входы формирователя

45 импульсов по фронту входного сигнала и второго элемента НЕ 42. С выхода формирователя 45 импульсов Ilo фронту входноп сигнала отрицательные импульсы с частотой следования 100 Гц через первый преобразователь 46 высокого уровня в низкий воздействуют на входы первого и второго элемента И вЂ” НЕ 48 и 49, а с выхода второго элемента НЕ прямоугольные импульсы поступают на вход второго преобразова1зля 47 высокого уровня в низкий, выход ко1169110 торого является четвертым выходом датчика 1 фазы напряжения (фиг. 5, Up).

Диод 36 устанавливает порог срабатывания формирователя близким к нулю, что повышает стабильность показаний при скачкообразных изменениях напряжения сети.

Диод 37 ограничивает прохождение отрицательных полуволн входного напряжения через резистор 34 на выход формирователя.

Прямоугольные импульсы с выхода элемента HE 43 (фиг. 5, Ug) поступают на входы первого элемента И вЂ” НЕ 48 и четвертого элемента НЕ 44, с выхода которого поступают на вход второго элемента И вЂ” НЕ 49.

С выхода второго элемента И вЂ” HE 49 импульсы (фиг. 4, Uq) поступают на вход генератора 2 тактовых импульсов, а с выхода первого элемента И вЂ” НЕ 48 (фиг. 4, Ug) — на вход двоичного счетчика 3 (фиг. 1).

Выходы второго и первого элементов

И вЂ” HE 49 и 48, третьего и четвертого эле20 ментов НЕ 43 и 44, второго преобразователя 47 высокого уровня в низкий служат выходами датчика 1 фазы напряжения.

Ключи представляют собой RS-триггеры.

Использование нового узла — блока фазирования — позволяет повысить надежность и энергетические показатели, так как при включении трансформаторной нагрузки возникают выбросы тока намагничивания, которые могут вызывать ошибочные срабатывания систем защиты, приводить к повышенному нагреву трансформатора, снижать коэффициент мощности питающей сети.

В предлагаемом устройстве выбросы тока намагничивания отсутствуют, так как перед включением сердечник трансформатора размагничен, а включение производится в моменты времени 90 и 270 эл. град. Тогда переходный процесс при включении отсутствует. Следовательно, повысится КПД установки, коэффициент мощности и надежность работы. В результате расширится сфера применения цифрового устройства для управления тиристорными контакторами в области регулирования объектов с трансформаторной нагрузкой.

1169110

Puz Z!!69!!О

Uñ

U»

24н

Ф22г 4

Ui4 226

22/6

2222

Риг .т

Редактор Е. 11апп

Заказ 4626/5!

Ug

U 7

U2 о6

Ug

U2

Uio

»s

«s

U2O

U21

22

Ьз

222Я

U24

1226

Составитель О. Г1арфенова

Техред И. Верес Корректор А. Тяско

Тираж 646 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035. Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная. 4