Цифровой фильтр

Иллюстрации

Показать всеРеферат

1. ЦИФРОВОЙ ФИЛЬТР, содержащий генератор импульсов, первый и ... второй управляемые делители частоты, первьш формирователь коротких импульсов , вход .которого является информационным входом цифрового фильтра , и элемент И, отличающий с я тем, что, с целью расширения функциональных возможностей, введены второй и третий формирователи коротких импульсов, блок привязки , первый и второй блоки вьщеления большей и меньшей частоты и элемент ИЛИ, при .этом вход второго .формирователя коротких импульсов подключен к прямому выходу генератора импульсов, а выход - к входам лервого и второго управляемых делителей частоты, вход третьего формирователя коротких импульсов подключен к инверсному выходу генератора импульсов, а выход - к синхронизирующему входу блока привязки, информационный вход которого соединен с выходом первого формирователя коротких импульсов, а выход - с первыми входами первого и второго блоков выделения большей и меньшей частоты, вторые входы которых подключены к выходам соответственно первого и второго управляемых делителей частоты, при этом первый выход первого блока вьщеления большей и меньшей частоты соединен с первым входом элемента И и является первым выходом цифрового фильтра, второй выход соединен с первым входом элемента ИЛИ и является вторым выходом цифрового фильтра, первый выход второго блока выделения большей и меньшей частоты 1О соединен с вторым входом элемента (Л ИЛИ, выход которого является третьим .. выходом цифрового фильтра,и является с: четвертым выходом цифрового фильтра,а второй выход является пятым выходом цифрового фильтра и соединен с втог рым входом элемента И, выход кото-, рого является шестым выходом цифрового фильтра. О5 2. Фильтр Но п. 1, отличаюсо 4 щийся тем, что каждьй блок вьщеления большей и меньшей частоты содержит два элемента И, элемент 2ИО ) ИЛИ, элемент ИЛИ-и два триггера, при этом первый вход первого элемента И объединен с первым входом элемента 2И-ИЛИ и является первым входом блока выделения большей и меньшей чacтoты вторым входом которого являются объединенные первый вход второго элемента И и второй вход элемент-а 2И-ИЛИ, выход первого элемента И соединен с единичным входом первого триггера и с первым входом элемента ИЛИ, выход которого является первым-выходом

(OIO3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (! 9) (! )) (s))4 Н 03 Н 17/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬПИЙ

ОЛИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMV СВИДЕТЕЛЬСТВУ

С

) (21) 3558065/24-09 (22) 17.02.83 (46) 23.07.85. Бюл. Ф 27 (72) А.А. Столяров (71) Тернопольский финансово-экономический институт (53) 621.396.6(088.8) (56) Авторское свидетельство СССР

N 469208, кл. Н 03 Н 11/00, 1971.

Авторское свидетельство СССР

))- 894849, кл. Н 03 К 5/19, 1980.

Авторское свидетельство СССР

М - 985939, кл. Н 03 Н 17/00, 1980. (54) (57) 1. ЦИФРОВОЙ ФИЛЬТР, содержащий генератор импульсов, первый и второй управляемые делители частоты, первый формирователь коротких импульсов, вход .которого является информационным входом цифрового фильтра, и элемент И, о т л и ч а ю— шийся тем, что, с целью расширения функциональных возможностей, введены второй и третий формирователи коротких импульсов, блок привязки, первый и второй блоки вьщеления большей и меньшей частоты и элемент ИЛИ, при этом вход второго .формирователя коротких импульсов подключен к прямому выходу генератора импульсов, а выход — к входам первого и второго управляемых делителей частоты, вход третьего формирователя коротких импульсов подключен к инверсному выходу генератора импульсов, а выход — к синхронизирующему входу блока привязки, информационный вход которого соединен с вы ходом первого формирователя коротких импульсов, а выход — с первыми входамй первого и второго блоков вьделения большей и меньшей частоты, вторые входы которых подключены к выходам соответственно первого и второго управляемых делителей частоты, при этом первый выход первого блока вьделения большей и меньшей частоты соединен с первым входом элемента И и является первым выходом цифрового фильтра, второй выход соединен с первым входом элемента ИЛИ и является вторым выходом цифрового фильтра, первый выход второго блока выделения большей и меньшей частоты соединен с вторым входом элемента

ИЛИ, выход которого является третьим выходом цифрового фильтра,и является четвертым выходом цифрового фильтра, а второй выход является пятым выходом цифрового фильтра и соединен с вто-, рым входом элемента И, выход кото-. рого является шестым выходом цифрового фильтра.

2. Фильтр поп. 1, отличаю- © шийся тем, что каждый блок вьде- (© ления большей и меньшей частоты содержит два элемента И, элемент 2И- )44

ИЛИ, элемент ИЛИ и два триггера, при ф,) этом первый вход первого элемента И объединен с первым входом элемента

2И-ИЛИ и является первым входом блока вьщеления большей и меньшей частоты фв вторым входом которого являются объединенные первый вход второго элемента И и второй вход элемента 2И-ИЛИ, выход первого элемента И соединен с единичным входом первого триггера и с первым входом элемента ИЛИ, выход которого является первым выходом

1169146 блока выделения большей и меньшей частоты, выход второго элемента И соединен с единичным входом второго триггера и с вторым входом элемента

ИЛИ, выход элемента 2И-ИЛИ соединен с нулевыми входами первого и второго триггеров и является вторым входом блока вьщеления большей и меньшей чаИзобретение относится к импульсной и вычислительной технике и может исполвзоваться при построении устройств обработки информации, представленной в виде частотно-модулиро- 5 ванных импульсных сигналов.

Цель изобретения — расширение функциональных возможностей.

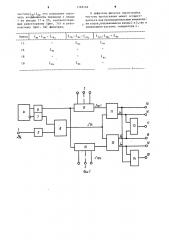

На фиг. 1 изображена структурная электрическая схема цифрового филь- 10 тра, на фиг. 2 — структурная электрическая схема блока вьщеления большей и меньшей частоты, на фиг.

3 — структурная электрическая схема блока привязки, на фиг. 4 — времен- 15 ные диаграммы, поясняющие работу блока привязки, на фиг. 5 — структурная электрическая схема формирователя коротких импульсов, на фиг; 6 — временные диаграммы, поясняющие работу 20 формирователя коротких импульсов, на фиг. 7 — графики, поясняющие функциональные возможности цифрового фильтра.

Цифровой фильтр (фиг. 1) содержит 25 информационный вход 1, управляющие входы 2 и 3, генератор 4 импульсов, Э первый 5, второй 6 и третий 7 формирователи коротких импульсов, блок 8 привязки, первый 9 и второй 10 управля- З0 емые делители частоты (УДЧ), блоки

11 и 12 выделения большей и меньшей частоты, элемент ИЛИ 13, элемент

И 14, первый 15, второй 16, третий

17, четвертый 18, пятый 19 и шестой ,20 выходы.

Блок выделения большей и меньшей частот (фиг. 2) содержит первый 21 и второй 22 входы, первый 23 и вто.—. рой 24 элементы И, элемент 2И-.ИЛИ

25, первый 26 и второй 27 триггеры, стоты, прямой выход первого триггера подключен к третьему входу элемента

2И-ИЛИ, инверсный выход — к второму входу второго элемента И, прямой выход второго триггера — к четвертому входу элемента 2И-ИЛИ, а инверсный выход — к второму входу первого элемента И. элемент ИЛИ 28, первый 29 и второй 30 выходы, Блок привязки (фиг, 3) содержит ,информационный вход 31, синхронизирующий вход 32, триггер.33 и элемент И 34, выход 35.

Формирователь коротких импульсов (фиг. 5) содержит вход 36, инверторы 37-39 элемент И 40, выход 41.

Цифровой фильтр работает следую-.. щим образом.

На вход 1 устройства подается фильтруемая последовательность импульсов, а на входы 2 и 3 управляющие коды, задающие коэффициент де-

° ления УДЧ 9 и 10, частоты, формирующих первую 1, и вторую1 частоты сре9 Э за.

Генератор 4 импульсов вырабатыва- . ет последовательность импульсов частотой 1г ъ 4 в гд в àñ o à по вторения импульсов во входной последовательности, и скважностью Д = 2.

В связи с тем, что второй и третий формирователи 6 и 7 коротких импульсов соединены с прямым и инверсным выходами генератора 4, на их выходах вьщеляются последовательности не со- . впадающих во времени коротких импульсов с частотами, равными частоте повторения импульсов на выходах генератора 4 импульсов. Работа первого, второго и третьего формирователей

5-7 импульсов объяснена временными диаграммами (фиг. 6); откуда видно, что каждый из формирователей выделя ет короткий импульс по переднему фрбнту входного сигнала, где . входной сигнал на входе 36 показан на фиг.б, а выходной сигнал инвертора 39 — на фиг. бб, выходной сигнал элемента И 40 (выход 41) — на фиг. 6 в.

11 691

Блок 8 привязки осуществляет привязку импульсов с выхода первого формирователя 5 к импульсам, выделяющимся на выходе третьего формирователя

7, Триггер 33 устанавливается. в единичное состояние по переднему фронту импульсом последовательности, поступающей на информационный вход 1 устройства (фиг. 4 б в), разрешая при этом прохождение через элемент И 34 после- 1О дующего за этим импульса последовательности с выхода первого формирователя 5 на вход блока 8 привязки (фиг.

4 а, в, г). Каждым выходным импульсом триггер 33 устанавливается в на- 15 чальное состояние (фиг. 4 в, г). Так как» )) 5ш,, то на выходе элемента .

И 34, выделяется последовательность коротких импульсов с .частотой 1 „, привязанная во времени к заднему 20 фронту импульсов, выделяемых на прямом выходе генератора 4, что обеспечивается связью синхронизирующего входа блока 8 привязки через третий формирователь 7 с инверсным вы- 25 ходом генератора 4.

В связи с тем, что на входы УДЧ

9 и 10 поступают короткие импульсы, соответствующие переднему фронту импульсов на прямом выходе генера- щ тора 4, на выходах УДЧ 9 и 10 выделяются последовательности коротких импульсов с частотами 2 ср1 35 ср 7 ю где К, К о — коэффициенты деления управляемых делителей 9 40 и 10 частоты, причем эти импульсы не совпадают во времени с импульсами, выделяемыми на выходе блока 8 привязки.

Первый и второй блоки 11 и 12 вы- 45 деления большей и меньшей частоты работают следующим образом.

Пусть|,ъ| а первый и второй триггеры 23 и 27 установлены в состо» янии 1, запрещающем прохождение им- 50 пульсов через элемент 2И-ИЛИ 25 и разрешающем прохождение импульсов через первый и второй элементы И 23 и

24. Если на первом входе 21 импульсов появляется раньше, чем На втором 55 входе 22, то он устанавливает второй триггер 27 в единичное состояние, разрешающее прохождение последую46 4 щего импульса на первом входе 21 через элемент 2И-ИЛИ 25 на входы первого и второго триггеров 26 и 27. С приходом этого импульса второй триг-. гер 27 установится в нулевое состояние. Таким образом, на выходе элемента И 24 выделяется большая частота ».,р,, а на выходе первого элемента И 23 — f, т.е. меньшая частота. ср э

При 1 <,р переключение первого тригге2 ра 26 обеспечивает выделение на втором выходе 30 меньшей, а на г ервом выходе 29 большей из входных частот.

Если частота входных сигналов равны .р. = 1ср, блоки 11 и 12 выделения большей и меньшей из входных частот обеспечивают выделение последовательностей с меньшей (выход 29) и большей (выход 30) фазой.

В связи с тем, что первые входы первого и второго блоков 11 и 12 выделения большей и меньшей частоты объединены и на них подается последовательность импульсов, частота которых соответствует частоте входного сигнала, а на другие входы подаются последовательности импульсов с частотами, равными частотам среза

1ср и f ср, на BbIxopÿõ этих блоков выделяются последовательности с частотами 1, в соответствии с таблицей.

Таким образом, по выходам 16 и

19 устройство работает как фильтр нижних частот относительно первой

fñð (фиг. 7б) и второй fc (фиг.7г) частот среза, а по выходам 15 и 18 как фильтр верхних частот относительно» и с (фиг. 7а,в). ср, срz

Соединение выхода меньшей частоты первого блока 11 с первым. входом элемента ИЛИ 13 и выхода большей частоты второго блока 12 с вторым его входом обеспечивает получение коэффициента передачи устройства с входа 1 на выход 17, соответствующего характеристике полосового заграждающего фильтра (фиг. 7е).

Подача импульсов с выхода большей частоты первого блока 11 и с выхода меньшей частоты второго бло-. ка 12 на входы элемента И 14 обеспечивает получение коэффициента переда-. чи, соответствующего полосовому пропускающему фильтру (фиг. 7д).

Прш близких управляющих кодах на выходах УДЧ 9 и 10 выделяются

1169146 Bx

8х

18

19 частоты 1,р, f, что позволяет получить коэффицйенты передачи с входа

1 на выходы 17 и 20, соответствующие режекторному (фиг. 7з) и резонансному (фиг. 7ж) фильтрам.

В цифровом фильтре перестройка частоты пропускания может осущест-.. вляться какпропорциональным изменением кодов, подаваемых на входы 2 и 3, так и изменением частоты генератора 4.

1169146

Фиг.2

1169146

Фиг 4

Фиг.5

1169146

Составитель Т. Афанасьева

Техред А.Бабинец Корректор М.Розман

Редактор А . Сабо

Заказ 4628/53 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4