Цифровой накопитель

Иллюстрации

Показать всеРеферат

ЦИФРОВОЙ НАКОПИТЕЛЬ, содержащий генератор тактовых импульсов, входной и выходной регистры и сумматор , первые входы которого соединены с выходами выходного регистра и выходной шиной, а входы входного регистра подключены к первой входной шине, отличают; ий с я тем, что, с целью расширения функциональных возможностей, в него введены управляющий рёгиср, переключатель кодов, RS-триггер и элемент ИЛ1, выход генератора тактовых импульсов. подключен к R-входу RS -триггера и первому входу элемента ИЛИ, второй вход которого объединен с S-входом триггера и соединен с выходом переполнения сумматора, вторые входы которого подключены к выходам переключателя кодов, а выходы сумматора соединены с входами выходного регистра, вход синхронизации которого подключен к выходу элемента ИЛИ, выходы триггера соединены с соответствующими управляющими входами переключателя кодов, перto вые и вторые кодовые входы кото (Л рого подключены к выходам соответственно входного регистра и управляющего регистра, входы которого соединены.с второй входной шиной.

00IO3 СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 Н 03 К 25/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ(СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ .И ОТКРЫТИЙ (21) 3733734/24-24 (22) 06.02.84 (46) 23.07.85. Вюл Р 27 (72) В.И.Никифоров (53) 621.374(088,8) (56) Патент США - 3582810, кл. 331/10, опублик 1979. "Sdelovaci technika ", 1973, У 6, с.224-225. (54)(57) ЦИФРОВОЙ НАКОПИТЕЛЬ, содержащий генератор тактовых импульсов, входной и выходной регистры и сумматор, первые входы которого соединены с выходами выходного регистра и выходной шиной, а входы входного регистра подключены к первой входной шине, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены управляющий региср, переключатель

„„SU„„» ям A кодов, RS-триггер и элемент ИЛИ, выход генератора тактовых импульсов, подключен к R âõîäó PS -триггера и первому входу элемента ИЛИ, второй вход которого объединен с S-входом триггера и соединен с выходом переполнения сумматора, вторые входы которого подключены к выходам переключателя кодов, а выходы сумматора соединены с входами выходного регистра, вход синхронизации которого подключен к выходу элемента ИЛИ, выходы триггера соединены с соответствующими управляющими входами переключателя кодов, первые и вторые кодовые входы которого подключены к выходам соответственно входного регистра и управляющего регистра, входы которого соединены.с второй входной шиной.

1 1169

Изобретение относится .к вычислительной технике и может быть использовано в качестве формирователя дискретной сетки частот с каналом компенсации накапливаемой фазовой погрешности.

Цель изобретения — расширение функциональных возможностей цифрового накопителя.

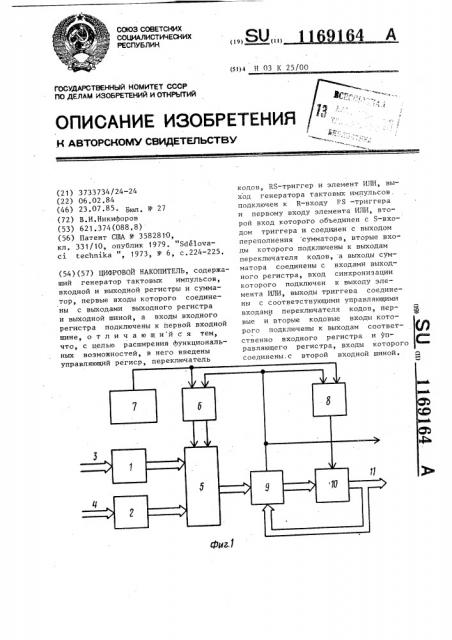

На фиг. 1 показана функциональная 1Р схема цифрового накопителя; на фиг. 2 — временные диаграммы работы устройства.

Устройство содержит входной регистр 1, управляющий регистр 2, вхо- 15 ды которых соединены соответственно с первой и второй входными шинами

3 и 4 записи числа, а выходы подключены к кодовым входам переключателя

5 кодов, управляющие входы которого 2О соединены с выходами RS-триггера 6, R-вход которого соединен с выходом генератора 7 тактовых импульсов и первым входом элемента ИЛИ 8, второй вход которого подключен к

S-входу RS -триггера 6 и выходу переполнения сумматора 9, другие входы которого соединены с выходами соответственно переключателя 5 кодов, выходного регистра 10 30 и выходной шиной t1. Входы регистра

10 соединены с выходами сумматора 9, а вход синхронизации подключен к выходу элемента ИЛИ 8.

На фиг. 2 приведены временные 35 диаграммы работы накопителя, где обозначено: а — последовательность тактовых импульсов с частотой следрвания fo ; б — изменение цифрового значения на выходе переклю- gp чателя 5 кодов ; в — изменение информации на выходах регистра 10; г — процесс накопления информации на выходах сумматора 9; д — импульсы переполнения со средней частотой следования f на выходе переполнения сумматора 9; е — последовательность импульсов на входе синхронизации регистра

10; ж — выход RS-триггера 6, уп- 5О равляющего включением числа, поступающего с шины 3 на выход переключателя 5 кодов.

Устройство работает следующим образом. 55

При подаче на R-вход RS-триггера 6 тактовых импульсов с генератора 7 на его инверсном выходе

Изменяя число любые дискретные (А), получают значения средней

164 2 устанавливается значение "1" и переключатель 5 кодов пропускает на вход сумматора 9 число, записанное в регистр 1 по шине 3. Тактовые импульсы с частотой следования f поступают с выхода генератора 7 через элемент ИЛИ 8 на вход регистра 10 и синхронизируют запись результатов суммирования сумматором 9 в регистр 10 через равные интервалы времени. Суммарный результат возрастает каждый период тактовой частоты fz на постоянную величину, равную значению числа на входных шинах

3 (А). В момент переполнения емкости сумматора 9, равной 2

Н где n — - число выходных двоичных разрядов сумматора 9, на выходе сумматора 9 появляется импульс переполнения, который, поступая через элемент ИЛИ 8 на вход регистра 10, производит запись разницы между результатом суммирова-. ния и значением "2" в регистр

10 и, одновременно поступая на

S-вход RS -триггера 6, устанавливает значение "1" на прямом выходе RS -триггера, что является командой переключателю 5 кода на включение числа с входной шины 4 (В) на входы сумматора 9, который осуществляет сложение числа, поступающего по шине 4, с записанной в регистр 10 разницей. Первый тактовый импульс, приходящий вслед за импульсом переполнения, производит запись результата суммирования числа, поступившего по шине 4, одновременно переводит триггер 6 в исходное состояние и обеспечивает подачу числа, поступившего по шине 3 на вход сумматора 9 до прихода следующего импульса переполнения.

Дополнительное суммирование числа по шине 4 в момент переполнения сумматора 9 эквивалентно снижению емкости накопителя без изменения характера процесса накопления. Выбирая различные значения числа (В) можно изменять рабочую емкость (Р) накопителя в широких пределах

P =Q-В, где Q = 2 — полная емкость нако- п пителя. где à — шаг сетки частот;

К = 1,2,... = целое положительное число ° д е

Фиг 2

Составитель Л.Захарова

Техред А. Бабинец Корректор М.Максимишинец

Редактор Аг.111андор

Заказ 4628/53 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

3 1169164 . 4 частоты следования импульсов переполнения с шагом ((F ) в соот-. ветствии с выражением

А А Ео. сР - Р л

В В этом режиме коэффициент делеПри наличии двоичного и -раз- ния устройства равен отношению рядного сумматора 9 несложно сформи- (В/А). Выбрав фиксированное десяровать дискретное множество частот тичное значение числа .(A) и изменяя в десятичной системе счисления. Дпя число (В), получим коэффициент дезтого достаточно выполнить условие 1Î ления накопителя, равный коэшфициенgF== =10 ту делителя с дробным переменным

Q- В Р коэффициентом деления.