Электронные вторичные часы с цифровой индикацией

Иллюстрации

Показать всеРеферат

1. ЭЛЕКТРОННЫЕ ВТОРИЧНЫЕ ЧАСЫ С ЦИФРОВОЙ ИНДИКАЦИЕЙ, содержащие соединенные между собой селектор импульсов и декаду регистра, запоминающее устройство и блок индикации, адресные входы которых соединены соответственно с первым и вторым выходами формирователя адреса, и дешифратор, отличающиеся тем, что, с целью повышения надежности отображения временной информации , в них введены последовательно соединенные генератор импульсов, делитель частоты , формирователь сигнала «Счет, счетная декада и коммутатор, счетчик принятых разрядов и схема сравнения, выход которой соединен с тактовым входом счетчика принятых разрядов и с третьим входом коммутатора , первый информационный вход которого соединен с выходом декады регистра , а выход - с информационным входом запоминаюшего устройства, выход которого соединен с информационным входом счетной декады и через дешифратор - с входом блока индикации, при этом выход счетной декады соединен с вторым информационным входом коммутатора и вторым входом формирователя сигнала «Счет, третий вход которого соединен с третьим выходом формирователя адреса, четвертый выход которого соединен с входом параллельной записи счетной декады, причем первый выход формирователя адреса соединен с первым информационным иродом схемы сравнения, второй информационный вход которой соединен с выходом счетчика принятых разрядов , установочный вход которого соединен с вторым выходом селектора импульсов, третий выход которого соединен с установочным входом делителя частоты и с входом стробирования схемы сравнения. 2. Часы по п. 1, отличающиеся тем, что формирователь сигнала «Счет содержит де шифратор, первый и второй триггеры, генератор одиночного импульса, схему совпадения , дешифратор переноса и индикатор аварии, причем выход дешифратора соедиi нен с установочным входом первого триггера , тактовый вход которого соединен с вхо (Л дом дешифратора и является первым входом блока, а выход - с входом индикатора аварии и с первым входом генератора одиночного импульса, первый выход которого соединен с установочным входом второго триггера, выход которого соединен с первым входом схемы совпадения, второй вход которой соединен с вторым выходом генератора одиночного импульса, тактовый о вход которого, соединенный с входом дешифратора переноса, одновременно с третьим входом схемы совпадения является третьим входом блока, вторым входом блока служи1 второй вход дешифратора переноса, первый выход которого соединен с информационным входом второго триггера, тактовый вход которого соединен с выходом схемы совпадения , который с вторым выходом дешифратора переноса является выходом блока.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (594 G 04 С 13 02

; „в

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ЙЬЛВУ Д;щ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3664614/24-10 (22) 24.11.83 (46) 30.07.85. Бюл. № 28 (72) Е. А. Борин и В. П. Кутасевич (53) 681.11(088.8) (56) Авторское свидетельство СССР № 785839, кл. G 04 С 11/00, 1979.

Авторское свидетельство СССР № 550615, кл. G 04 С 13/02, 1975. (54) (57) 1. ЭЛЕКТРОННЫЕ ВТОРИЧНЫЕ

ЧАСЫ С ЦИФРОВОЙ ИНДИКАЦИЕЙ, содержащие соединенные между собой селектор импульсов и декаду регистра, запоминающее устройство и блок индикации, адресные входы которых соединены соответственно с первым и вторым выходами формирователя адреса, и дешифратор, отличающиеся тем, что, с целью повышения надежности отображения временной информации, в них введены последовательно соединенные генератор импульсов, делитель частоты, формирователь сигнала «Счет», счетная декада и коммутатор, счетчик принятых разрядов и схема сравнения, выход которой соединен с тактовым входом счетчика принятых разрядов и с третьим входом коммутатора, первый информационный вход которого соединен с выходом декады регистра, а выход — с информационным входом запоминающего устройства, выход которого соединен с информационным входом счетной декады и через дешифратор — с входом блока индикации, при этом выход счетной декады соединен с вторым информационным входом коммутатора и вторым входом формирователя сигнала «Счет», третий вход которого соединен с третьим выходом формирователя адреса, четвертый выход ко

„„SU„„1170417 А торого соединен с входом параллельной записи счетной декады, причем первый выход формирователя адреса соединен с первым информационным входом схемы сравнения, второй информационный вход которой соединен с выходом счетчика принятых разрядов, установочный вход которого соединен с вторым выходом селектора импульсов, третий выход которого соединен с установочным входом делителя частоты и с входом стробирования схемы сравнения.

2. Часы по п. 1, отличающиеся тем, что формирователь сигнала «Счет» содержит дешифратор, первый и второй триггеры, генератор одиночного импульса, схему совпадения, дешифратор переноса и индикатор аварии, причем выход дешифратора соеди нен с установочным входом первого триггера, тактовый вход которого соединен с входом дешяфрвторв я является первым входом (/) блока, а выход — с входом индикатора аварии и с первым входом генератора \ одиночного импульса, первый выход которого соединен с установочным входом вто- ф рого триггера, выход которого соединен с первым входом схемы совпадения, второй вход которой соединен с вторым выходом генератора одиночного импульса, тактовый ) вход которого, соединенный с входом дешифратора переноса, одновременно с третьим входом схемы совпадения является третьим входом блока, вторым входом блока служиг второй вход дешифратора переноса, первый выход которого соединен с информационным входом второго триггера, тактовый вход которого соединен с выходом схемы совпадения, который с вторым выходом дешифратора переноса является выходом блока.

:В

1170417

Изобретение относится к хронометрии и предназначено для использования при управлении территориально-разнесенными объектами, требующими временного взаимодействия.

Целью изобретения является повышение надежности отображения временной информации.

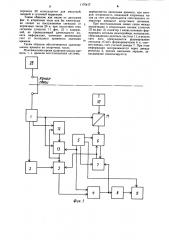

На фиг. 1 приведена структурная схема электронных вторичных часов; на фиг. 2-временные диаграммы, поясняющие работу. предлагаемых часов; на фиг. 3 — пример реализации формирователя адреса; на фиг. 4 — временные диаграммы, поясняющие работу формирователя адреса, на фиг. 5 — вариант выполнения формирователя сигнала «Счет»; на фиг. б — временные диаграммы, поясняющие работу формирователя «Счет».

Вторичные часы содержат селектор импульсов 1, декаду регистра 2, коммутатор

3, запоминающее устройство 4, формирователь адреса 5, форм ирователь сигнала

«Счет» б, счетную декаду 7, дешифратор 8, блок индикации 9, генератор импульсов 10, делитель частоты 11, счетчик принятых разрядов 12 и схему сравнения 13.

Первый выход селектора импульсов 1 соединен с входом декады регистра 2, выход которой через коммутатор 3 соединен с информационным входом запоминающего устройства 4, адресные входы которого соединены с первым выходом формирователя адреса 5. Выход запоминающего устройства

4 через дешифратор 8 соединен с первым входом блока индикации 9, второй вход которого соединен с вторым выходом формирователя адреса 5.

Генератор 10 соединен с первым входом делителя частоты 11, второй установочный вход которого соединен с третьим выходом селектора импульсов 1, к которому подключен и вход стробирования схемы сравнения 13. Выход делителя частоты 11 соединен с выходом формирователя сигнала

«Счет» 6, выход которого соединен с тактовым входом счетной декады 7, информационный вход которой соединен с выходами запоминающего устройства 4. Вход строба параллельной записи счетной декады

7 соединен с четвертым выходом формирователя адреса 5, третий выход которого соединен с третьим входом формирователя сигнала «Счет» 6, второй вход которого соединен с выходами счетной декады 7, которые соединены с вторым входом коммутатора 3, третий вход которого соединен с выходом схемы сравнения 13, соединенным с тактовым входом счетчика принятых разрядов 12, установочный вход которого соединен с вторым выходом селектора импульсов 1, а выход — соединен с вторым входом схемы сравнения 13, первый выход которой соединен с первым выходом формирователя адреса 5.

Каждый пакет информации начинается маркерным сигналом и содержит в себе разделенные межсерийными интервалами последовательности импульсов десятичных разрядов текущего времени, причем первый передаваемый разряд информации — младший.

Для примера рассмотрим работу устройства с передачей информации один раз в секунду — секундные метки приведены на фиг. 2.1. На диаграмме фиг. 2.2 (участки

I, 111) показана огибающая сигналов, поступающих на вход вторичных часов — участок I I соответствует отсутствию входных сигналов. Поступающий на вторичные часы сигнал поступает на вход селектора импульсов 1, где происходит выделение маркерного сигнала, соответствующего началу пакета передаваемой информации, импульсов

Формирователь сигнала «Счет» 6 содержит дешифратор 14, первый 15 и второй

16 триггеры, индикатор аварии 17, генератор одиночного импульса 18, схему совпа. дения 19 и дешифратор переноса 20.

Динамический вход триггера 15 соединен с выходом делителя частоты 11 и объединен с входом дешифратора 14, выход которого соединен с установочным входом

10 первого триггера 15, выход которого соединен с входом индикатора аварии 17 и с первым входом генератора одиночного импульса 18, первый выход которого соединен с установочным входом второго триггера 16, выход которого соединен с первым входом схемы совпадения 19, второй вход которой соединен с вторым выходом генератора одиночного импульса 18, тактовый вход которого соединен с выходом старшего разряда формирователя адреса 5, выход младшего разряда которого соединен с входом дешифра20 тора переноса 20. 1 ретий вход схемы совпадения соединен с выходом сигнала счетного такта формирователя адреса 5, а ее выход соединен с динамическим входом второго триггера 16 и с тактовым входом счетной декады 7, установочный вход которой соединен с вторым входом дешифратора переноса 20, второй вход которого соединен с выходами счетной декады 7, а первый выход — соединен с информационным входом второго триггера 16.

Пример реализации формирователя адреса 5 представляет собой последовательно соединенные генератор 21, распределитель тактов 22, счетчик 23 и дешифратор 24.

Вход селектора импульсов 1 вторичных часов через канал связи соединен с первичными часами 25.

Электронные вторичные часы работают следующим образом.

Первичные часы 25 формируют шкалу текущего времени и периодически в виде пакетов информации посылают ее в канал

40 связи.

1 170417 кода текущего времени и межсерийных сигналов.

Последовательность импульсов кода те. кущего времени преобразуется декадой регистра 2 в параллельный вид и далее, через коммутатор 3 (управляемую схему

ИЛИ) поразрядно записывается в ячейки запоминающего устройства 4, определяемые формирователем адреса 5.

Кроме этого, формирователь адреса 5 осуществляет синхронизацию работы узлов вторичных часов. Генератор 21 вырабатывает импульсы (фиг. 4.1), из которых распределитель тактов 22 формирует сигналы «Выбор микросхемы» (фиг. 4.4) и «Запись— считывание» (фиг. 4.5), предназначенные для управления работой запоминающего устройства 4. Сигнал, показанный на фиг. 4.2 используется в качестве строба параллельной записи для счетной декады 7, а сигнал, показанный на фиг. 4.3, — в качестве счетного импульса, подаваемого на вход формирователя сигнала «Счет» 6. Счетчик

23 формирует адресные сигналы (фиг. 4.6—

4.8) для запоминающего устройства 4, из которых дешифратор 24 вырабатывает сигналы (фиг. 4.9 — 4.13) управления разрядами блока индикации 9, информация которых поразрядно, через дешифратор 8 считывается из запоминающего устройства 4.

Частота повторения сигналов формирователя адреса 5 выбрана с учетом удовлетворения требованиям динамической индикации.

Под действием сформированных формирователем адреса 5 управляющих сигналов при каждом обращении к ячейке (адресу) запоминающего устройства 4 осуществляется перезались ее информации в счетную декаду 7 (сигнал фиг. 4.2), а при совпадении нулевого значения сигнала «Выбор микросхемы» (фиг. 4.4) и единичного значения сигнала «Запись-считывание» (фиг. 4.5) осуществляется обратная запись информации из счетной декады 7 через открытый коммутатор 3 в ту же ячейку запоминающего устройства 4, чем обеспечивается постоянная регенерация информации.

Синхронизация сигналов взаимно независимых генератора 21 формирователя адреса 5, обеспечивающего последовательное обращение к ячейкам ЗУ, и генератора первичных часов 25, формирующих поступающие на вторичные часы пакеты информации, осуществляется счетчиком п ринятых разрядов 12 и схемой сравнения 13, путем открывания коммутатора 3 в момент совпадения состояний счетчика 23 формирователя адреса 5 и счетчика принятых разрядов 12. Этим обеспечивается запись очередного поступившего на вход вторичных часов разряда информации в соответствующую ему ячейку запоминающего устройства 4.

Задним фронтом выходного сигнала схемы сравнения 13 продвигается в следующее состояние счетчик принятых разрядов 12, чем

20 обеспечивается подготовка к приему следующего разряда информации. По окончании пакета входящей информации счетчик принятых разрядов 12 сбрасывается в исходное состояние сигналом с выхода селектора 1 и удерживается до прихода маркерных импульсов пакета информации.

Генератор 10 формирует высокостабильные импульсные сигналы, частота которых делителем частоты 11 делится до частоты следования пакетов выходящей от первичных часов 25 информации (фиг. 2.3).

При поступлении на вход вторичных часов информации (участки 1 и 3 фиг. 2), выделяемые селектором 1 сигналы межсерийных интервалов, обнуляют делитель частоты 11, не позволяя ему включить формирователь сигнала «Счет» 6 (делитель частоты 11 не успевает сформировать комбинацию, на которую настроен дешифратор 14 формирователя сигнала «Счет» 6) .

Последний не воздействует на счетную декаду 7, через которую регенерируется занесенная в ячейки запоминающего устройства 4 информация.

При пропадании информации на входе

25 вторичных часов (участок 2 фиг. 2) селектор 1 не формирует сигналов межсерийных интервалов, сбрасывающих делитель частоты 11, в результате чего последний доходит до состояния, на которое настроен дешифратор 4 (фиг. 2.4) и взводит триггер 15, запуска ющий генератор одиночного импульса 18, осуществляющий привязку сигналов формирователя адреса 5 (генератор

21) к сигналам делителя частоты 11. Сигнал триггера 15 (фиг. 2.5 и фиг. 6.1) также включает индикатор 17, извещающий оператора о пропадании линии. Сигнал с первого выхода генератора одиночного импульса 18 (фиг. 6.5) взводит второй триггер 16 (фиг. 6.7), подготавливающий к работе схему совпадения 19, сигнал на выходе которой совпа40 дает по времени с сигналом распределителя 22 формирователя адреса 5 (фиг. 4.3 и фиг. 6.4) и сигналом второго входа генератора одиночного импульса 18 (фиг. 6.6).

Сформированный таким образом сигнал

«Счет» (фиг. 6.8) поступает на тактовый

45 вход счетной декады 7 и своим отрицательным фронтом добавляет единицу к ранее занесенной в нее информации (по сигналу фиг. 4.2) из ячейки младшего разряда запоминающего устройства 4 (адрес см. фиг. 6.2 и 6.3). Положительным фронтом сигнала схемы совпадения 19 проверяется состояние дешифратора переноса 20 (фиг. 6.9).

Если при обработке информации младшего разряда возникает сигнал переполнения (фиг. 6.9), триггер 16 не переходит в нулевое состояние, блокирующее прохождение сигнала «Счет» (фиг. 4.3 и фиг. 6.4) через схему совпадения 19 при обработке последующих разрядов. Второй выход дешифратора

1170417 переноса 20 используется для минутной, часовой и суточной коррекции.

Таким образом, как видно из диаграмм фиг. 2, вторичные часы как бы ежесекундно следят за поступлением сигналов от первичных часов 25 и, при отсутствии этих сигналов (участок 1! фиг. 2) с задержкой, не превышающей длительности пакета информации, начинают автономный счет от последнего принятого значения времени.

Таким образом обеспечивается хранение шкалы времени во вторичных часах.

Максимальное время хранения шкалы времени, т. е. времени восстановления системы, определяется значением времени, при котором погрешность показаний вторичных часов за счет нестабильности собственного генератора превысит допустимое значение.

При восстановлении линии связи между первичными и вторичными часами (участок

III на фиг. 2) селектор 1 вновь начинает формировать сигналы межсерийных интервалов, сбрасывающих делитель частоты 11, в результате чего прекращается формирование сигналов «Счет» формирователем 6 и, соответственно, счет счетной декады 7. При этом информация воспринимается через декаду регистра 2, причем внесенное заранее, запаздывание компенсируется.

1170417 0öã. 2 к(Рорниробааерю сигнала „счет биения к 039

1 170417 рие. 5

1170417

4 ° °

° ° °

° ° °

° ° °

° ° °° ° °

Составитель В. Савинков

Редактор М. Товтин Техред И. Верес Корректор О. Тигор

Заказ 4703/44 Тираж 406 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4