Цифровой дискриминатор

Иллюстрации

Показать всеРеферат

1. ЦИФРОВОЙ ДИСКРИМИНАТОР, содержащий счетчик первого параметра, счетчик второго параметра, первый блок сравнения, регистр результатови блок управления, блок управления содержит два элемента И, триггер, элемент ИЛИ и элемент задержки, причем вход запуска дискриминатора соединен со счетным входом триггера и первым входом первого элемента ИЛИ, вход первого параметра дискриминатора соединен со счетным входом счетчика первого параметра, выходы которого соединены с первой группой информа-г ционных входов регистра результата, вход второго параметра дискриминатора соединен со счетным входом счетчика второго параметра, выходы которого соединены с второй группой информационных входов регистра результата , выходы которого соедине.ны с выходами дискриминатора, первая группа входов задания уровней дискриминации дискриминат.ора соединана с первой группой информационных входов первого блока сравнения, отличающий с я тем, что, с целью расширения функциональных возможностей за счет дискриминации по разности и сумме параметров в него введены сумматор, вычитатель и второй блок сравнения, а в Олокуправления введены третий элемент И и второй и третий элементы ИЛИ, причем в блоке управления инверсный выход триггера соединен с первыми входами первого и второго элементов ИЛИ, выходы которых соединены соответственно с первым и вторым входами третьего элемента ИЛИ и i первыми входами соответственно второго и третьего элементов И, выход (Л третьего элемента ИЛИ соединен с вторым входом первого элемента И, выход которого через элемент задержки соединен с вторыми входами первого и третьего элементов И, вторая группа входов задания уровня дискриминации дискриминатора соединена с первой группой информации входов второго блока управления, выходы счетчика первого параметра соединены с первыми группами входов сумматора и вычиj;; . тателя, выходы счетчика второго пара4 метра соединены с вторыми группами входов сумматора и вычитателя, выходы сумматора соединены с второй группой информационных входов первого блока сравнения и третьей группой информационных входов регистра результата, выходы вычитателя соединены с второй группой информационный входов второго блока сравнения и четвертой группой информационных входов регистра результата, выходы второго и третьего элементов блока управления соединены

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТ ИЧЕСНИХ

РЕСПУБЛИН (191 (1I)

SU, (51)4 С 06 F

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3713415/24-24 (22) 26. 12.83 (46) 30.07.85. Бюл. К - 28 (72) М.ÅI.Штейнберг, Г.С.Вайсман, А.Т.Ситников и А.С.-N.Íàôèåâ (71) Специальное конструкторское бюро

Биологического приборостроения с опытным производством Института физики АН АЗССР (53) 681.32(088.8) (56) Авторское свидетельство СССР

ЕЕ- 591854, кл. С 06 F 7/02, 1972.

Авторское свидетельство СССР

ЕЕ 1023320 кл. 6 06 F 7/02, 1983. (54) (57) 1. ЦИФРОВОЙ ДИСКРИМИНАТОР, содержащий счетчик первого параметра, счетчик второго параметра, первый блок сравнения, регистр результатов . и блок управления, блок управления содержит два элемента И, триггер, элемент ИЛИ и элемент задержки, причем вход запуска дискриминатора соединен со счетным входом триггера и первым входом первого элемента ИЛИ, вход первого параметра дискриминатора соединен со счетным входом счетчика первого параметра, выходы которого соединены с первой группой информа-. ционных входов регистра результата, вход второго параметра дискриминатора соединен со счетным входом счетчика второго параметра, выходы которого соединены с второй группой информационных входов регистра результата, выходы которого соединены с выходами дискриминатора, первая группа входов задания уровней дискриминации дискриминатора соединана с первой группой информационных входов первого блока сравнения, о т л и ч а ю— шийся тем, что, с целью расширения функциональных возможностей за счет дискриминации по разности и сумме параметров в него введены сумматор, вычитатель и второй блок сравнения, а в блок управления введены третий элемент И и второй и третий элементы ИЛИ, причем в блоке управления инверсный выход триггера соединен с первыми входами первого и второго элементов ИЛИ, выходы которых соединены соответственно с первым и вторым входами третьего элемента ИЛИ и первыми входами соответственно второго и третьего элементов И, выход третьего элемента ИЛИ соединен с вторым входом первого элемента И, выход которого через элемент задержки соединен с вторыми входами первого и третьего элементов И, вторая группа входов задания уровня дискриминации дискриминатора соединена с первой группой информации входов второго блока управления, выходы счетчика первого параметра соединены с первыми группами входов сумматора и вычитателя, выходы счетчика второго параметра соединены с вторыми группами входов сумматора и вычитателя, выходы сумматора соединены с второй группой информационных входов первого блока сравнения и третьей группой информационных входов регистра результата, выходы вычитателя соединены с второй группой информационньы входов второго блока сравнения и четвертой группой информационных входов регистра результата, выходы второго и третьего элементов блока управления соединены группами входов сумматора, вычитат ля, первого и второго узлов сравнения, вторая группа информационных входов блока соединена с вторыми группами входов сумматора и вычитателя, выходы сумматора соединены с информационными входами .первого регистра, выходы которого подключены к второй группе входов первого узла сравнения, выход которого соединен с первым выходом блока, выходы вычитателя соединены с информационными входами второго регистра, выходы которого соединены с второй группой входов второго узла сравнения, выход которого соединен с вторым выходом блока, управляющий вход блока соединен с входами синхронизации первого и второго регистров.

1170447 с управляющими входами соответственно первого и второго блоков сравнения, выход первого элемента и блока управления соединен с входом синхронизации регистра результата, первый и второй выходы первого блока сравнения соединены соответственно со вторым и третьим входами первого элемента ИЛИ блока управления, первый и второй выходы второго блока сравнения соединены соответственно с вторым и третьим входами второго элемента ИЛИ блока управления.

2. Дискриминатор по и. 1> о т л ич а ю щ и и с -я тем, что блок сравнения содержит сумматор, вычитатель, два регистра и два узла сравнения, причем первая группа информационных входов блока соединена с первыми

Изобретение относится к вычислительной и информационно-измерительной технике и может найти применение в системах регистрации и обработки случайных сигналов.

Целью изобретения является расши° рение функциональных возможностей за счет дискриминации по разности и сумме параметров.

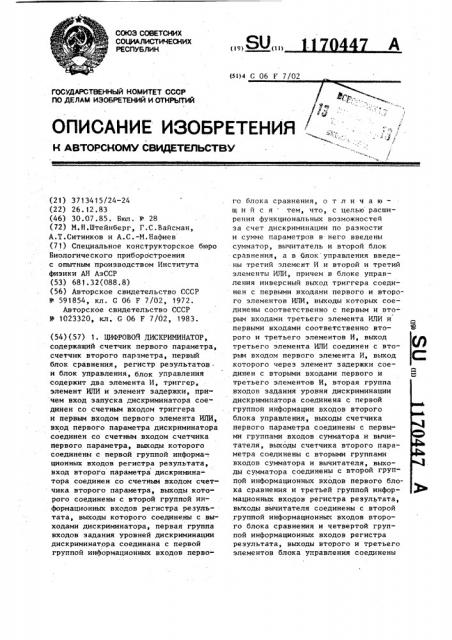

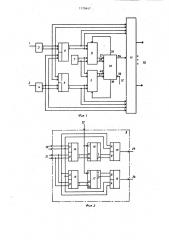

На фиг. 1 представлена структура цифрового дискриминатора; на фиг. 2 структура первого и второго блоков сравнения; на фиг. 3 — структура блока управления.

Цифровой дискриминатор (фиг. 1) содержит вход 1 первого параметра, вход 2 второго параметра, счетчик 3 первого параметра,, счетчик 4 второго параметра, сумматор 5, вычитатель 6, переключатель 7 уровней, первый и второй блоки 8 и 9 сравнения,. блок 10 управления, регистр 11 результата, вход 12 запуска дискриминатора, выходы 13 дискриминатора.

В состав блоков сравнения (фиг. 2) входят сумматор 14, вычитатель 15 первый и второй регистры 16 и 17, первый и второй узлы 18 и 19 сравнения, первая и вторая группы информационных входов 20 и 21 блока, управляюt 2

I щий вход 22, первый и второй выходы 23 и 24.

В состав блока 10 управления (фиг. 3) входят первый, второй и тре5 тий элементы ИЛИ 25, 26 и 27, первый, второй и третий элементы И 28, 29 и 30, триггер 31, формирователь 32 импульса, элемент задержки 33, выходы 34 — 36 и входы 37 — 41.

Цифровой дискриминатор работает следующим образом.

В исходной состоянии счетчики 3 и 4 цифрового дискриминатора и регистры 16 и 17, входящие в состав

1з,блоков 8 и 9, обнулены.

Перед началом цикла обработки анализируемой величины на управляющий вход 12 цифрового дискриминатора по" дается сигнал высокого уровня, а за20 тем на входы 1 и 2 начинают посту" пать унитарные коды соответствующих исходных параметров, характеризирующих объект или процесс.

Указанные коды подаются на счет2 ные входы счетчиков 3 и 4 соответственно. В сумматоре 5 производится сложение кодов счетчиков 3 и 4. В вычитателе 6 производится вычитание значения кода счетчика 4 из кода

30 счетчика 3.

1170447

Получаемые (накапливаемые) таким образом значения суммы и разности анализируемых параметров с выходов сумматора 5 и вычитателя 6 подаются на вторые группы информационных вхо-. 5 дов блоков 8 и 9 формирования сигналов разрешения соответственно, на первые группы информационных входов которых подается код величины шага уровня дискриминации, задаваемой

t0 переключателем 7 уровней.

Блоки 8 и 9 идентичны. Поэтому рассмотрим работу только блока 8 срав; нения.

Значение кода со второй группы 15 информационных входов блока 8 подаеткя на вторые группы входов сумматора 14 и вычитателя 15 и одновременно на первые группы входов узлов 18 и 19 сравнения. 20

В сумматоре 14 при этом производится сложение исследуемого кода, поступившего на вторую группу информационных входов блока 8, с кодом величины шага уровня дискриминации. 25

В вычитателе 15 определяется разность исследуемого кода и .кода величины шага уровня дискриминации.

После прекращения передачи кодов анализируемых параметров на управляю-Зб щий вход 12 цифрового дискриминатора подается сигнал низкого уровня, в соответствии с которым на входах 34, 35 и 36 блока 10 управления формируются сигналы соответственно синхронизации регистра 11 и записи содержимого сумматора 14 и вычитателя 15 в регистры 16 и 17 блоков 8 и 9.

При этом в регистр 16 блока 8 формирования сигналов разрешения записывается значение суммы исследуемого кода и кода величины шага уровня дискриминации, а в регистр 17 значение разности исследуемого кода и кода величины шага уровня дискриминации. Эти значения задают верхний и нижний уровни ближайших сумморазностных значений дискриминации анализируемой величины.

Последующие циклы обработки производятся аналогично первому, однако теперь после подачи сигнала на управляющий вход 12 устройства на выходах 34, 35 и 36 блока 10 управления будут формироваться сигналы только в случае достижения верхнего или нижнего сумморазностного значения уровня дискриминации.

При этом код исследуемого параметра поступает на первые группы входов узлов 18 и 19 сравнения и сравнивается с кодами верхнего и нижнего уровней дискриминации, поступающими на вторые группы входов соответственно из регистров 16 и 17.

При достижении указанного условия на выходе соответствующего узла сравнения в соответствующем блоке 8 (9) формируется сигнал разрешения, поступающий на вход блока 10 управления.

Таким образом, на выходах 34, 35 и 36 блока 10 управления вырабатываются сигналы соответственно синхронизации регистра 11 и записи верхнего и нижнего сумморазностных значений уровня дискриминации.

1 170447

71,1170447

Фий 3

Составитель А, Чеканов

Редактор М.Келемеш Техред О.Ващишина Корректор В.Гирняк

Заказ 4705/46 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r.Ужгород, ул.Проектная, 4