Вычислительное устройство

Иллюстрации

Показать всеРеферат

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее регистр-аккумулятор, группу из k регистров-операндов, микропрограммный блок управления, арифметико-логический блок и коммутатор, причем выход коммутатора подключен к первому информационному входу арифметико-логического блока, выход результата которого соединен с информационными входами регистра операндов группы, выходы которых подключены к соответствующим информационным входам коммутатора, (k+1)-й информационньш вход которого соединен с вторым информационным входом арифметикологического блока и с выходом pierHCTра-аккумулятора , входом подключенного к выходу результата арифметикологического блока, выходы сдвига влево, сдвига вправо и переноса которого соединены соответственно с входами с первого по третий логических условий микропрограммного блока управления, выходы операционных полей которого с первого по ()-и соединены соответственно с управлякицими входами регистров-операндов группы, i регистра-аккумулятора, коммутатора и арифметико-логического блока, отличающееся тем, что, с целью увеличения быстродействия вычислительного устройства при выполнении операции извлечения квадратного корня, оно содержит коммутатор цифры результата, причем выходы двух старпих разрядов регистра аккумулятора соединены с информационным входом коммутатора цифры результата, выход которого соединен с четветрым входом 4: 4; логических условий микропрограммного блока управления, (k+4)-й Ьыход операционных полей которого соединен 00 с управляющим входом коммутатора цифры результата.

СОЮЗ СОВЕТСНИХ

ИУЮ

РЕСПУБЛИК (5Ц4 С 06 F 7/38

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2 1) 359 1026/24-24 (22) 20;05.83 (46) 30.07.85. Бюл. Р 28 (72) Г.В.Гончаренко, В.И.Жабин, В.И.Корнейчук, А.Е.Лысенко, В.В.Макаров, В.А.Репко и В.П.Тарасенко (53) 681.33(088.8) (56) 1. Самофалов К.Г. и др. Электронные цифровые вычислительные машины. Киев, "Вища школа", 1976, с.357.

2. Коган Б.М., Каневский М.М. Цифровые вычислительные машины и системы. М., "Энергия", 1973, с. 32 1.

3. Березенко А.И.и др. Микропроцессорные комплекты повышенного быстродействия. М., "Радио и связь", 1981, с. 99-120, рис. 498 (прототип). (54)(57) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее регистр-аккумулятор, группу из k регистров-операндов, микропрограммный блок управления, арифме-. тико-логический блок и коммутатор, причем выход коммутатора подключен к первому информационному входу арифметико-логического блока, выход результата которого соединен с информационными входами регистра операндов группы, выходы которых подключены к соответствующим информационным входам коммутатора, (1+1)-й информацион„„SU„„11 44 ный вход которого соединен с вторым информационным входом арифметикологического блока и с выходом регистра-аккумулятора, входом подключенного к выходу результата арифметикологического блока, выходы сдвига влево, сдвига вправо и переноса которого соединены соответственно с входами с первого по третий логических условий микропрограммного блока управления, выходы операционных полей которого с первого по (1+3)-й соединены соответственно с управляющими входами регистров-операндов группы, регистра-аккумулятора, коммутатора Е 2 и арифметико-логического блока, о тл и ч а ю щ е е с я тем, что, с целью увеличения быстродействия вычислительного устройства при выполнении операции извлечения квадратного Я корня, оно содермит коммутатор цифры результата, причем выходы двух старших разрядов регистра аккумулятора соединены с информационным входом коммутатора цифры результата, выход которого соединен с четветрым входом логических условий микропрограммного блока управления, (k+4)-й выход опе рационных полей которого соединен с управляющим входом коммутатора цифры результата.

1170448

Изобретение относится к вычислительной технике и может быть использовано в электронных цифровых вычислительных машинах и микропроцессорах. 5

Известно арифметическое устройство, содержащее операционные блоки, каждый из которых предназначен для выполнения определенной операции (например, умножения, сложения, 10 вычитания, деления, извлечения корня). Устройство позволяет достичь высокой производительности при реализации вычислительных процессов (1$.

Однако данное устройство содер- 15 жит большой обьем аппаратуры.

Известно арифметическое устройство, содержащее блок управления, сумматор, регистры (21 .

Однако известное устройство 20 имеет ограниченные функциональные возможности, так как введение новой операции требует изменения его структуры.

Наиболее близким по технической сущности к изобретению является вычислительное устройство, содержащее арифметико-логический блок, регистра-аккумулятор регистры-опеФ

30 ранды, коммутатор и блок микропрограммного управления, причем к первой группе входов арифметико-логического блока подключены выходы регистра-акуумулятора, а к второй — выходы коммутатора, к информационным входам которого подключены выходы регистров-операндов и регистра -аккумулятора, информационные выходы арифметико-логического блока подключены к информационным входам ре- 40 гистра-аккумулятора и регистровоперандов, выходы сдвига влево и вправо, а также выход переноса арифметико-логического блока подключены к входам логических условий микропрограммного блока управления, выходы операционных полей микропрограмного блока управления подключены к управляющим входам регистров-операндов, регистра аккумулятора, арифметико-логического блока и коммутатора (3) .

Арифметические операции в этом устройстве реализуются путем после- 55 довательного выполнения микроопераций сдвига и суммирования (вычитания) в сответствии с микропрограммами, записанными в микропрограммном блоке управления.

Недостатком указанного устройства является низкое быстродействие при вычислении квадратного корня.

Цель изобретения — увеличение ,быстродействия вычислительного устройства при выполнении операции извлечения квадратного корня.

Поставленная цель достигается тем, что вычислительное устройство, содержащее регистр-аккумулятор, группу 1 регистров-операндов, микропрограммный блок управления, арифметикологический блок и коммутатор, причем выход коммутатора подключен к первому информационному входу ариметико-логического блока, выход результата которого соединен с информационными входами регистров-операндов группы, выходы которых подключены к соответствующим информационным входам коммутатора, (k+1)-й информационный вход которого соединен с вторым информационным входом арифметико-логического блока и с выходом регистра-аккумулятора, входом иод..люченного к выходу результата арифметико-логического блока, выходы сдвига влево, сдвига вправо и переноса которого соединены соответственно с входами с первого по третий логических условий микропрограмного блока управления, выходы операционных полей которого с первого по (k+3)-й соединены соответственно с управляющими входами регистровоперандов группы, регистра-аккумулятора, коммутатора и арифметика-логического блока, содержит коммутатор цифры результата, причем выходы двух старших разрядов регистра-аккумулятора соединены с информационным входом коммутатора цифры результата, выход которого соединен с четвертым входом логических условий микропрограммного блока управления, (k+4)-й выход операционных полей которого соединен с управляющим входом коммутатора цифры.

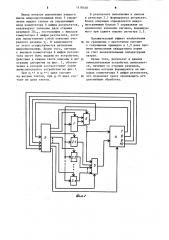

На фиг. 1 представлена схема вычислительного устройства; на фиг.2— диаграмма алгоритма вычисления квадратного корня.

Вычислительное устройство содержит регистр-аккумулятор 1, группу 2 регистров-операндов, коммутатоР 3, арифметико-логический блок 4, микроСдвиг влево или вправо в регистре-аккумуляторе 1 или в регистрахоперандах 2.1-2.k может быть осуществлен за один такт. При этом операнд выдается из нужного регистра через коммутатор 3 на арифметико- 40 логический блок 4, где сдвигается влево или вправо, а с выхода результата арифметико-логического блока записывается в тот же регистр, Сложение (вычитание) содержимого двух <5 0+2R; < 2 регистров также осуществляется за один такт. При этом в качестве регистра одного операнда всегда используется регистр-аккумулятор 1. Второй операнд может находиться в любом 50 регистре-операнде 2.1-2.k. Результат суммирования (вычитания) может быть записан только в те регистры, в которых находились операнды. Пересылка из регистра в регистр производится 55 за один такт. При этом информация из регистра 2.1-2.3 передается в арифметико-логический блок 4, с выходов

Двухразряд ное двоичное представление цифры результата гд

Выполняемое соотношение начение цифы реультаа

О 0

0 1

1 0

1 1

2 2R с1

1 1

-1 2R ° -2

1-!

2- а 2R. a Q

1 1

3 1 программный блок 5 управления, коммутатор 6 цифры результата, выходы 7 — 10 результата, сдвига влево, вправо и три переноса блока 4.

Коммутатор 6 цифры результата состоит из элементов И, первые входы которых подключены к выходам регистра-аккумулятора 1, а вторые входы— к выходу микропрограммного блока 5 управления.

Вычислительное устройство работает следующим образом.

Арифметические операции в вычислительном устройстве осуществляются

1 путем последовательного выполненйя микроопераций сдвига и суммирования (вычитания) в соответствии с микропрограммами, записанными в микропрограммном блоке 5 управления. Ветвление программ осуществляется в зависимости от значений сигналов, посту-. пающих в определенный момент времени с выходов переноса, сдвига влево или вправо арифметико-логического блока 4. Кроме того, ветвление программ может производиться по сигналам, поступающим на входы микропрограммного блока управления 5 с выхода коммутатора 6 цифры результата.

Выполнение операций сдвига, сложения, вычитания, умножения, деления и пересылки не отличается от выполнения данных операций в устройствепрототипе.

170448. 4которого записывается в нужный регистр..

При выполнении операции извлечения квадратного корня у=1(х (1/4ах 1) вычислительное устройство работает в соответствии со следующим алгоритмом:

Y =1, 2R =(х-1) р

Для i=1,п выполнить п.п. 3-5;

10 -1 при 2R;Ä (-2 у = 0 при -2 " s 2R;., (2

1 при 2R 2, R„=2R;-У„- „у -у 2 2 - ° где Y1 — слово, содержащее только i; старших разрядов результата; у; — очередная цифра результата;

R< — очередной остаток.

Микропрограмма выполнения операции извлечения квадратного корня реализуется по диаграмме алгоритма фиг.2.

Для вычисления необходимы, например, регистры 2.1, 2.2 и 2.3 для хранения — Y R,2 . В исходном состоянии величина 2К =(х-1) хранится в регистре-аккумуляторе 1, в регистре 2. t записана " 1", регистр 2.2 обнулен, а в регистре 2.3 записана

1 величина 2

Зо

Соответствие значений старших разрядов 2R;, (знакового r, и старшего разряда дробной части z, ) и очередного разряда результата у" приведено в таблице.

Операция извлечения квадратного корня выполняется за п циклов. Цикл состоит из нескольких тактов, в каждом из которых выполняется только одна микрооперация.

1170448

Перед началом выполнения каждого цикла микропрограммный блок 5 управления выдает сигнал на управляющий вход коммутатора 6 цифры результатов, анализирует значение двух старших разрядов 2R „, поступающих с выходов коммутатора 6 цифры результата, которые представляют собой значение очередного разряда у; . В зависимости от этого осуществляется ветвление микропрограммы. Кроме того, сигналы с выходов коммутатора 6 цифры результата могут быть выданы из устройства.

Действия в каждом такте описаны в диаграмме алгоритма на фиг. 2, обозначения в которой соответствуют схеме вычислительного устройства на фиг.1.

При y; — 1 и y; — 1 Цикл сОстОит из восьми тактов, при у„ =0 цикл состоит из двух тактов.

В результате выполнения и пиклов в регистре 2.1 формируется результат.

Конец операции определяется микро5 программным блоком 5 управления по единичному значению сигнала, формируемого при сдвиге вправо регистра 2.3.

Положительный эффект изобретения

10 по сравнению с прототипом состоит в сокращении примерно в 1,5 раза времени вычисления квадратного корня за счет незначительных аппаратурных затрат.

15 Кроме того, результат в данном вычислительном устройстве вычисляется, начиная со старших разрядов, значения которых формируются на выходах коммутатора 6 цифры результата, 20 что позволяет сразу производить его дальнейшую обработку.

1170448 .

Составитель А.Клюев

Редактор М.Келемеш Техред А.Бабинец Корректор B.БYтяга

Заказ 4705/46 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г.Ужгород, ул.Проектная, 4