Устройство программного управления

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ПРОГРАМШОГО УПРАВЛЕНИЯ, содержащее генератор импульсов, счетчик, блок постоянной памяти, элемент И и группу элементов И, выход генератора импульсов соединен ро счетным входом счетчика , выход которого соединен с адресным входом блока постоянной памяти , первая группа выходов которого подключена к первым входам элементов И группы, вторые входы которых соединены с выходом элемента И, выходы элементов И группы являются информационными выходами устройства , отличающееся тем, что, с целью повышения быстроГ . :-.-: Т:ЧД

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (! 9) (!!) (!)4 G 06 Р 9/06

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСЯОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3500706/24-24 (22) 14. 10. 82 (46) 30.07.85. Бюл. М 28 (72) В.К. Никифоров, Т.М. Симонова н Г.Н. Сорокин (53) 681.325(088.8) (56) Авторское свидетельство СССР

В 189830, кл. G 06 F 9/06, 1967.

Авторское свидетельство СССР

9 591858, кл. G 06 F 9/06, 1978. (54)(57) 1. УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ, содержащее генератор импульсов, счетчик, блок постоянной памяти, элемент И и группу элементов И, выход генератора импульсов соединен со счетным входом счетчика, выход которого соединен с адресным входом блока постоянной памяти, первая группа выходов которого подключена к первым входам элементов И группы, вторые входы которых соединены с выходом элемента

И, выходы элементов И группы явля.ются информационными выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно дополнительно содержит группу блоков коммутации, причем первые информационные входы блоков коммутации являются входами логических условий устройства, управляющие входы блоков коммутации подключены к второй группе выходов блока постоянной памяти, выходы блоков коммутации соединены с входами элемента И.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что каждый блок коммутации содержит элемент

ИЛИ и два элемента И, причем инверс" ный вход элемента ИЛИ, прямой вход первого элемента И, соединенный с инверсным входом второго элемента

И, являются управляющими входами блока, инверсный вход первого элемента И, соединенный с прямьв(входом второго элемента И, является информационньи входом блока, выходы первого и второго элементов И соединены соответственно с первьв(и вторым прямыми входами элемента

ИЛИ, выход которого является выходом блока.

1170456

Изобретение относится к вычислительной технике, в частности к решающим устройствам, и может быть использовано для решения задач по временным булевым функциям: в устройствах управления, автоматики.

Целью изобретения является повышение быстродействия устройства программного управления.

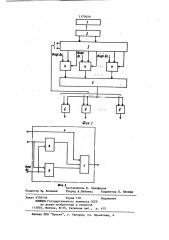

На фиг. 1 приведена структурная 1О. схема предлагаемого устройства, на фиг. 2 — функциональная схема блока коммутации.

Устройство программного управления (фиг. 1) содержит генератор 1 15 импульсов, счетчик 2, блок 3 постоянной памяти, группу блоков 4 коммутации, элемент И. 5, группу элементов

И 6. На информационные входы блоков 4 коммутации поступают сигналы 20 логических условий устройства.

Блок 4 коммутации (фиг..2) содержит один элемент ИЛИ 7 и два элемента И 8 и 9.

Устройство программного управле- 25 ния работает следующим образом.

На информационные входы группы блоков 4 коммутации поступают сигналы логических условий устройства, принимающие значения, соответствую- 3п щие логическому "0" или логической

"1". Другие входы блока 4 коммутации являются управляющими,на которые подаются сигналы с блока 3 постоянной памяти.

В блок 3 постоянной памяти записана информация в соответствии с программой управления работой блоков

4 коммутации и группы элементов И 6, составленной на основании исходных данных о конъюнкциях, подлежащих вычислению.

Генератор 1 импульсов с периодом колебаний Т и счетчик 2 осуществляют формирование сигналов, поступающих на адресные входы блока 3 постоянной памяти, и на его выходах появляются сигналы, представляющие со, бой логический "0" или логическую

11 11

1 в соответствии с записанной по, заданному адресу информацией.

В соответствии с управляющими сигналами, поступающими от блока

3 постоянной памяти, на выходе блока 4 коммутации (фиг. 2) формирует" ся: значение сигнала логического условия, подключенного к информационному входу блока 4 коммутации, если,этот сигнал логического условия является сомножителем вычисляемого логического произведения; инверсия сигнала логического условия, подключенного к информационному входу блока 4 коммутации, если сомножителем вычисляемого произведения-является инверсия этого сигнала логического условия; значение логической "1", если сигнал логического условия, подключенный к информационному входу блока 4 коммутации, не является сомножителем вычисляемого логического произведения.

Таким образом, соответствующим заданием управляющих сигналов, поступающих с блока 3 (фиг. 1) постоянной памяти на блоки 4 коммутации, к входам элемента И 5 подключаются те сигналы логического условия или инверсия сигналов логического. условия, которые являются сомножителями вычисляемого логического произведения, на остальные входы элемента

И 5 при этом подключается логическ ая 11 1 11 .

На выходе элемента И 5 появляется сигнал резуль тата логического умножения сигналов логических услов ий или их инверсий в соответствии с программой работы блоков 4 к оммутации в

По управляющему сигналу, поступающему от блока 3 постоянной памяти, открывается один элемент из группы элементов И 6, и сигнал ре" зультата логического умножения задан1ных сигналов логических условий или их инверсий появляется на одном из. информационных выходов устройства.

1170456

Pve.Ð

Составитель В. Никифоров Редактор + Келемеш Техред А.Бабинец Корректор Л. Бескид

Заказ 4705/46 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открыт И

1!3035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4