Формирователь сигнала

Иллюстрации

Показать всеРеферат

ФОРМИРОВАТЕЛЬ СИГНАЛА, содержащий a входных транзисторов, коллекторы которых соединены с выводом входного резистора и с базой первого транзистора, базы /г входных транзисторов соединены с вторым выходом входного резистора, источник напряжения, отличающийся тем, что, с целью увеличения быстродействия и уменьшения потребляемой мощности, в него введены второй и третий транзисторы и первьй и второй резисторы, причем базы ti входных транзисторов соединены с эмиттером третьего транзистора, который через первый резистор соединен с коллектором первого транзистора и с базой второго транзистора, база третьего транзистора соединена с коллектором второго транзистора и через второй резистор - с шиной источника наг1ряжения , с которой также соединен коллекi тор третьего транзистора, эмиттер (Л первого транзистора и змиттер второго транзистора соединены с выходной шиной.

СООЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (! 9! (! !) (!)4 H 03 К 5/01

48 k„ ... Ъ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ/

Н АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3345783/24-21 (22) 06.10.83 (46) 30.07.85. Бюл. ¹ 28 (72) В.В.Пастон, И,Л.Дробышева и Л.П.Холоднова (53) 682t374(088.8) (56) Патент Англии № 1489861, кл. H 03 К 13/25, 1977.

Ultra High speed Ж-Blt RAM

with 7,5 ns Acuss Time SIIC(:-77, Feb, 16, 1977, р. 77-79. (54)(57) ФОРМИРОВАТЕЛЬ СИГНАЛА, содержащий и. входных транзисторов, коллекторы которых соединены с выводом входного резистора и с базой первого транзистора, базы, входных транзисторов соединены с вторым выходом входного резистора, источник

l напряжения, отличающийся тем, что, с целью увеличения быстродействия и уменьшения потребляемой мощности, в него введены второй и третий транзисторы и первый и второй резисторы, причем базы и входных транзисторов соединены с эмиттером третьего транзистора, который через первый резистор соединен с коллектором первого транзистора и с базой второго транзистора, база третьего транзистора соединена с коллектором второго транзистора и через второй резистор — с шиной источника на!1ряжения, с которой также соединен коллектор третьего транзистора, эмиттер первого транзистора и эмиттер второго транзистора соединены с выходной шиной.

1170593

Изобретение относится к вычислительной технике и может быть использовано в качестве. элемента управления адресной шиной оперативного запоминающего устройства. 5

Цель изобретения — увеличение быстродействия и уменьшение потребляемой мощности за счет уменьшения перепаДов напряжений на элементах формирователя.

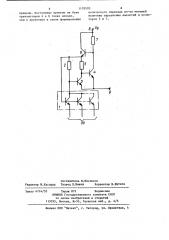

На чертеже приведена прин»»»»пиальная схема формирователя сигнала.

Формирователь сигнала содержит »1 входных транзисторов 1, коллекторы которых соединены с выводом входного 15 резистора 2 и с базой первого транзистора 3, базы и входных транзис горов соединены с вторым выводом входного резистора 2, второй транзистор

4, первый резистор 5, а также тре- 20 тий транзистор 6 и второй резистор

7, причем базы и входных транзистo ров 1 соединены с эмиттерами транзистора 6, который через первый резистор 5 соединен, с коллектором пер- 25 вого транзистора 3 и с базой второго транзистора 4, база третьего транзистора 6 соединена с коллектором второго транзистора 4 и через второй резистор 7 — с »ш»ной 8 источни30 ка напряжения, с которой также соединен коллектор третьего транзистора 6, эмиттер первого транзистора 3 и эмиттер второго транзистора 4 сое— динены с выходной шиной 9, выходами

10 формирователя. сигнала являются эмиттеры и входных транзисторов 1.

Формирователь сигнала работает следующим образом.

Пусть на входы формирователя сиг- 40 нала подается такая комбинация логических сигналов, что все »1 входных транзисторов 1 закрь»ты, ток в их коллекторной цепи отсутствует и через резистор 2 течет только базовый ток транзистора 3, вызванный прохождением тока источника тока, подключенного к выходной шине 9, через эмиттер транзистора 3.

Ъ

За счет протекания коллекторного тока транзистора 3 потенциал на базе транзистора 4 достаточно низкий z» транзистор 4 закрыт. Через резистор

7 течет базовый ток транзистора 6. На эмиттере транзистора 6 сформиро- 55 ван высокий потенциал, который ниже .потенциала шины 8 на суммарную ве,личину падения напряжения на открытом переходе база-эмиттер транзистора 6 и величину падения напряжения на резисторе 7, создаваемого за счет протекания базового тока тра»»зистора 6.

На шине 9 формирователя сигнала образован также высокий потенциал, котсрый ниже потенциала общей шины на величину падения напряжения на открытых переходах база-эмиттер транзисторов 6 и 3 и величину падения напряжения на резисторах 7 и 2 за счет протекания базовых токов транзисторов 3 и 6. Если на входы формирователя сигнала подается такая комбинация логических сигналов, что ток протекает хотя бы в одном из входных транзисторов 1, то за счет протекания коллекторного тока »» входных транзисторов 1 в резисторе 2 потенциал на базе транзистора 3 понижается и ток в эмиттерной и коллекторной цепях транзистора 3 уменьшается. Потенциал на базе транзистора

4 за счет уменьшения тока в резисторе 5 повышается, и транзистор 4 начинает проводить большой ток. Через его эмиттер проходит большая часть тока источника тока, подключенного к выходной шине 9. На выходе формирователя сигнала образуется низкий потенциал, который ниже потенциала на шине 8 на величину суммарного падения напряжения на резисторе 7 за счет протекания коллекторного тока транзистор. 4, падения напряжения на резисторе 5 ввиду протекания коллекторного тока транзисторов 3 и базового тока транзистора 4 и падений напряжений на переходе база-.эмиттер транзисторов 4 и 6.

В итоге логический перепад между состояниями выборки-и невыборки на выходной шине формирователя образует-. ся в основном на резисторе 7. В режиме переключения переход от низкого потенциала к высокому на базе транзистора 3 проходит быстрее из-за наличия указанной дополнительной цепи, так как большая часть логического перепада формируется на резисторе 7 за счет протекания тока источника тока, и только небольшая часть логического перепада формируется на резисторе 2, что дает возможность выбрать резистор 2 в 5-15 раз меньше, чем у прототипа, а это приводит к такому же уменьшению постоянной

Составитель В.Мясников

Редактор И.Касарда Техред Л.Микеш Корректор В.Бутяга

Заказ 4714/53

Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва,.Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 з l170593 . 4 времени. Постоянные времени на базе логического перепада иэ-за меньшей транзисторов 4 и 6 также меньше, величины паразитных емкостей и резисчем у прототипа в узлах Формирования торов 5 и 7.