Устройство для формирования логарифмического ряда частот

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЛОГАРИФМИЧЕСКОГО РЯДА ЧАСТОТ, содержащее первый двоичный счетчик, последовательно соединенные второй двоичный счетчик, детектор нуля и блок ключей, выходы которого соединены с входами установки второго двоичного счетчика, синхронизирующий вход которого соединен с шиной тактовых импульсов, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет уменьшения основания логарифма формируемого ряда частот, в него введены шифратор и последовательно соединенные шина импульсов смены частоты, счетчик частот, счетчик октав и коммутатор, первый информационный вход которого соединен с выходом детектора нуля и с входом первого двоичного счетчика, выходы разрядов которого соединены с остальными информационными входами коммутатора соответственно, врходы разрядов счетчика частот соединены со входами шифратора , вы (Л ходы которого соединены с соответствующими входами блока клюс чей.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСИИХ

РЕСПУБЛИН (l9) (I )) J (5))4 Н 03 К 5/156

ОЛИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCH05Af СВИДЕТЕПЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНР) ПИй (21) 3469202/24-10 .(22) 06.05.82 (46) 30.07.85. Бюл. Ы 28 (72) Н.Г. Иванов (53) 621.374.2 (088.8) (56) Авторское свидетельство СССР

У 855936, кл, Н 03 В 23/00, 1978.

Патент США 1) 3588843, кл. Н 03 К 5/156, опублик. 1971. (54)(57) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЛОГАРИФМИЧЕСКОГО РЯДА ЧАСТОТ, содержащее первый двоичный счетчик, последовательно соединенные второй двоичный счетчик, детектор нуля и блок ключей, выходы которого соединены с входами установки второго двоичного счетчика, синхронизирующий вход которого соединен с шиной тактовых импульсов, о т л и— ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет уменьшения основания логарифма формируемого ряда частот, в него введены шифратор и последовательно соединенные шина импульсов смены частоты, счетчик частот, счетчик октав и коммутатор, первый информационный вход которого соединен с выходом детектора нуля и с входом первого двоичного счетчика, выходы разрядов которого соединены с остальными информационными входами коммутатора соответственно, вуходы разрядов счетчика частот соеди- Е

Я иены со входами шифратора, выходы ко торого соединены с соответствующими входами блока ключей.

1170603

Изобретение относится к импульс- . ной технике.

Цель изобретения — расширение функциональных возможностей устройства за счет уменьшения основания 5 логарифма формируемого ряда частот.

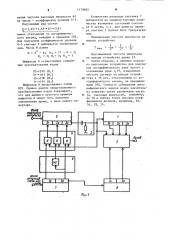

На фиг. 1 представлена структурная схема устройства для формирования логарифмического ряда частот; на фиг. 2 — временные диаграммы его работы (г„ ж — в укрупненном масштабе).

Устройство для формирования логарифмического ряда частот содержит первый двоичный счетчик 1, второй двоичный счетчик 2, детектор 3 нуля, блок 4 ключей, коммутатор 5, шифратор 6, счетчик 7 частот, счетчик 8 октав, шины тактовых импульсов и импульсов смены частоты, при- 20 чем шина тактовых импульсов, второй двоичный счетчик 2, детектор 3 нуля и блок 4 ключей соединены последовательно. Шина импульсов смены частоты, счетчик 7 частот, счетчик 25

8 октав и коммутатор 5 также соединены последовательно. Выходы счетчика 7 частот соединены с входами шифратора 6, выходы которого соединены с входами блока 4 ключей, выходы которого соединены с входами установки второго двоичного счетчика 2. Выход детектора 3 нуля соединен с одним из информационных входов коммутатора 5 н входом пер35 вого двоичного счетчика 1, выходы разрядов которого соединены с остальными информационными входами коммутатора 5.

Устройство работает следующим образом.

Счетчик 2, детектор 3 и блок 4 образуют управляемый делитель частоты, осуществляющий деление частоты входных тактовых импульсов 45 (фиг. 2и) на целые числа — коэффициенты деления. Каждый раз, когда счетчик 2 в процессе своего счета переполняется и переходит в нулевое состояние, срабатывает детектор 3 50 нуля (фиг. 21). При этом импульс с выхода детектора 3 нуля через блок

4 ключей производит принудительный перевод счетчика 2 в некоторое состояние, характеризуемое числом N. 55

Изменяя число М, можно изменять число разрешенных состояний счетчика 2, тем самым управлять коэффициентом деления, изменять частоту импульсов на выходе делителя 3 нуля.

Коэффициент деления К делителя частоты рассчитывается по формуле

K= 2-М, я где и — количество разрядов счетчика 2.

Поскольку установка разрядов счетчика 2 производится в момент полного его обнуления, достаточно задействовать лишь входы установки разрядов счетчика 2 в "1".

Переключение коэффициента деления (выбор чисел И) производится по командам счетчика 7 частот, который просчитывает импульсы смены частоты. Период импульсов смены частоты (фиг. 2o) выбирается, как правило, много большим периода импульсов на выхоце детектора 3 нуля.

Количество различных коэффициентов деления и соответственно количество различных частот импульсов на выходе детектора 3 нуля равно количеству возможных состояний счетчика 7 частот.

Преобразование двоичного кода, снимаемого с выходов разрядов счетчика 7 частот, в код, по которому открываются соответствующие заданному коэффициенту деления ключи блока

4, производит шифратор 6.

Коэффициенты деления выбираются такими, чтобы в процессе заполнения счетчика 7 частот импульсами смены частоты (фиг. 2 ) частота импульсов на выходе детектора 3 нуля (фиг. 2q) ступенчато возрастала по логариф- мическому закону в пределах от значения f до 2f с возвратом к исходному значению К при переполнении и обнулении счетчика 7 частот (фиг.20).

Таким образом, на выходе детектора 3 нуля формируется периодически повторяющийся ряд частот с малым диапазоном изменения частоты — в два раза. Основание этого логарифмического ряда может быть достаточно малым и обеспечивается выбором количества частот в ряду.

Двоичный счетчик 1 просчитывает импульсы, поступающие с выхода детектора 3 нуля, производит деление ряда частот. На выходе первого разряда счетчика 1 возникает дискретный ряд частот со значениями от f/2 до 2f/2, на выходе второго разряда — от f/4 до 2f/4 и т.д..

1170б03

Минимальное значение частоты импульсов, возникающих на выходе последнего разряда счетчика 1, можно рассчитать по формуле

5 мчн - 2т ) где m — количество разрядов счетчика 1.

Двоичные коды, возникающие на выходах разрядов счетчика 8 октав в !

О процессе счета счетчиками 7 и 8 импульсов смены частоты, подаются на управляющие входы коммутатора 5, чем обеспечивается последователь,ное подключение к выходу устройства сигналов (фиг. 2 к), возникающих на выходах отдельных разрядов счетчика 1. Коммутация производится так, чтобы в процессе заполнения счетчика 8 октав к выходу устройства подключались все более высококачественные выходы счетчика 1. Последним на выход устройства подключается входной сигнал счетчика 1, после чего счетчик 8 октав переполняется, и на выходе устройства происходит скачкообразный возврат к сигналу с минимальной частотой (фиг. 2х).

Таким образом, все счетчики устройства работают .циклично.

В начале цикла работы, при нулевом состоянии счетчиков 7 и 8, на выходе детектора 3 нуля формируются импульсы с частотой f а на выход устройства поступает сигнал со старшего разряда (m) -счетчика т.е. сигнал с частотой

2f

F !

О макс 2 "

В момент переполнения и обнуления счетчика 7 частот, счетчик 8 октав переходит в состояние ."1", при котором коммутатор 5 подключает на выход устройства сигнал,. поступающий с выхода m-1 разряда счетчика 1. На выходе устройства появля ется сигнал с частотой

f 2f

I мни 2в- 2" Q макс t

f о мни

При заполнении счетчика 7 частот, частота импульсов на выходе детектора 3 нуля возрастает по логариф мическому закону до значения 2f, а на выходе устройства — до значения

45 т.е. в момент переполнения счетчика 7 частот скачка частоты на выходе устройства не происходит.

Во время следующего заполнения счетчика 7 частот на выходе устройства продолжается формирование логарифмического ряда частот с возрастанием частоты импульсов до значения

2f

|Макс после чего счетчик 7 частот переполняется, счетчик 8 октав переходит в состояние "2" и т.д.

Максимальная частота сигнала на выходе устройства формируется при полном заполнении счетчиков 7 и 8.

Она равна Zf. На этом заканчивается цикл формирования логарифмического ряда частот на выходе устройства. С приходом следующего импульса смены частоты счетчики 7 и 8 обнуляются, происходит возврат к началу цикла.

Вариант конкретного выполнения устройства.

Пусть счетчики 7 и 8 выбраны двухразрядными, т.е. могут принимать по четыре состояния. В этом случае в логарифмическом ряце частот со значениями от f до 2f должно содержаться четыре частоты. Коэффициент (основание логарифма) такого логарифмического ряда можно рассчитать по формуле

% а =+2

) где q — количество возможных состояний счетчика 7 частот.

В данном примере основание логарифма формируемого ряда частот

1 а = - 2 = 1,19.

Ряд частот получается следующим

f — >1, 19f «1,41f -1,68f — (2f)

От достигнутой при реализации устройства точности формирования частот этого ряда зависит точность формирования всего логарифмического ряда частот. Указанные соотношения частот могут быть получены, например, делением тактовой частоты 401 на числа — коэффициенты деления 40, 34, 29, 24. В этом случае отклонение от логарифмического закона не превьппает 27., Для простоты приведен случай, когда ряд частот формируется путем де1170603 ления частоты тактовых импульсов 6f на числа - коэффициенты деления 6-3.

Полученный ряд частот

f 1,2f- 1,5f 2f (2f) — — 3 .имеет отклонения от логарифмического закона1 лежащие в пределах 20Х.

:,Для получения коэффициентов деления

6-3 счетчик 2 выбирается трехразрядным. Числа N равны

М = 2 — К. М< 2з 6 2 я

М2 = 3 М = 4 N = 5 з

Шифратор 6 осуществляет следующие преобразования кодов

00 010 (М,)

01- 011 (N )

10 100 (М )

11 101 (М )

Шифратор 6 представляет собой

ПЗУ. Однако анализ представленного преобразования кодов показывает, что для данного простого примера шифратор 6 может быть выполнен значительно проще, в виде одного инвертора.

Количество разрядов счетчика 1 выбирается на единицу большим количества возможных состояний счетчика 8 октав, т.е. для данного примера счетчик 1 должен быть трехразрядным.

Минимальная частота импульсов на выходе устройства

1О

f f

Мин 2

Максимальная частота импульсов на выходе устройства равна 2f.

15 Таким образом, в примере показано выполнение устройства для получения логарифмического ряда частот с основанием ряда 1)19, изменением частоты сигнала на выходе устрой20 ства в 16 раз, отклонениями от логарифмического закона, не превышающими 207.. Точность соблюдения логарифмического закона можно значительно повысить путем увеличения часто25 ты тактовых импульсов, например, до 40 и выбора более высоких коэффициентов деления, например, 40, 34, 29, 24.

1170603

Составитель Ю. Бурмистров

Редактор И. Касарда Техред JI.Микещ Корректор Е. Сирохман

Заказ 4714/53 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4