Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ по авт. св. № 805487, отличающийся тем, что, с целью повьшения быстродействия и точности, дополнительно введены 6 преобразующих каскадов, блок выделения адресного кода, блок регистров памяти, тп основньк входов которого соединены через арифметическое устройство с )Tj выходами счетчика, а Е адресных входов соединены с выходами блока вьщеления адресных кодов, входы которого соединены с логическими выходами 6 преобразующих каскадов, причем вход предьщущего преобразующего каскада соединен с выходом последующего преобразующего каскада, а вход первого преобразующего каскада соединен с выходом сумматора, аналоговый выход последнего преобразующего каскада соединен с входом первой ячейки памяти, два дополнительных выхода устройства управления соеS динены с дополнительным входом (Л блока регистров памяти и входом блока вьщеления адресного кода, дополнительный выход которого соединен с вторым входом устройства, управления.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (l 9) (1)) (51) 4 г @

/ ) Ф

ОПИСАНИЕ ИЗОБРЕТЕНИЯ/

H ABTOPCHGMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (61) 805487 (21) 2784560/18-21 (22) 25.06.79 (46) 30;07.85. Бюл. Р 28 (72) В.Н. Махов, А.В. Жуков, Н.Н. Мельник и Б.С. Новисов (71) Уральский ордена Трудового

Красногс Знамени политехнический ,институт им. С.M. Кирова (53) 681.325 (088.8) (56) 1. Авторское свидетельство СССР

У;- 805487, кл. Н 03 К 13/17, 1979. (54)(57) АНАЛОГΠ†ЦИФРОВ ПРЕОБРАЗОВАТЕЛЬ по авт. св. 805487, о т— л и ч а ю шийся тем, что, с целью повышения быстродействия и точности, дополнительно введены (преобразующих каскадов, блок выделения адресного кода, блок регистров памяти, )и основных входов которого соединены через арифметическое устройство с ))) выходами счетчика, а (, адресных входов соединены с выходами блока выделения адресных кодов, входы которого соединены с логическими выходами 0 преобразующих каскадов, причем вход предыдущего преобразующего каскада соединен с выходом последующего преобразующего каскада, а вход первого преобразующего каскада соединен с выхбдом сумматора, аналоговый выход последнего преобразующего каскада соединен с входом первой ячейки памяти, два дополнительных выхода устройства управления соединены с дополнительным входом блока регистров памяти и входом блока выделения адресного кода, дополнительный выход которого соединен с вторым входом устройства.. управления.

Изобретение относится к радио-. технике и может быть использовано

1170606 выход последнего преобразующего каскада соединен с входом первой!

20 \

30

40

50

55 в спектрометрии ионизирующих излучений.

Известен аналого-цифровой преобразователь, содержащий входное устройство, дискриминатор, линейный коммутатор, сумматор, основной дискриминатор уровня, схему синхронизации, задающий генератор, блок эталонной длительности, генератор эталонного тока, интегратор, блок распределения импульсов, счетчик, первую и вторую ячейки памяти, блок управления, арифметический блок, блок вывода кода, разрядное устройство, причем выход входного формирователя соединен через коммутатор с первым входом сумматора, второй вход которого подключен через генератор нарастающего напряжения к первому выходу генератора кода; второй вход коммутатора соединен через вторую ячейку памяти с выходом первой ячейки памяти, входы арифметического устройства подключены к выходам счетчика импульсов, счетный вход которого соединен с вторым выходом генератора кода, а выход подключен к входу блока вывода кода, выходы устройств управления соединены с входами управления всех блоков, а первый вход подключен к выходу входного формирователя Я .

Недостатками данного аналого-. цифрового преобразователя являются низкие быстродействие и точность, Цель изобретения — повышение быстродействия и точности.

Поставленная цель достигается тем, что в аналого-цифровой преобразователь дополнительно введены преобразующих каскадов, блок выделения адресного кода, блок регистров памяти, m основных входов которого соединены через арифметическое устройство с тп выходами счетчика, а f адресных входов соединены с вь)ходами блока выделения адресных кодов, входы которого соединены с логическими выходами 0 преобразующих каскадов, причем вход предыдущего преобразующего каскада соединен с выходом последующего преобразующего каскада, а вход первого преобразующего каскада соединен с выходом сумматора, аналоговый ячейки памяти, два дополнительных выхода устройства управления соединены с дбполнительным входом блока регистров памяти и входом блока выделения адресного кода, дополнительный выход которого соединен с вторым входом устройства управления.

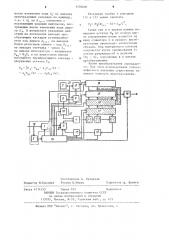

На чертеже изображен аналого-цифровой преобразователь.

Аналого-цифровой преобразователь содержит входное устройство I дискриминатор 2, коммутатор 3, сумма" тор 4, преобразующие каскады 5-1

5-0, схему 6 синхронизации, задающий генератор 7, пропускатель 8, генератор 9 эталонного тока, интегратор 10, счетчик 11, первую и вторую ячейки 12 13 14 управления, арифметическое устройство 15, блок 16 вывода кода, блок

17 выделения адресного кода, блок 18 регистров памяти, причем блоки 1 и 2 объединены в блок 19 входного формирователя," блоки 9 и 10

4 объединены в блок 20 линейно нарастающего напряжения; блоки 6 — 8 объединены в генератор 21 единичного кода.

Аналого-цифровой преобразователь работает следующим образом.

В режиме коррекции на первый вход сумматора 4 подается с помощью коммутатора 3 нулевой потенциал, а на второй его вход — линейно изменяющееся напряжение U с выхода блока 20. Одновременно с включением линейно изменяющегося напряжения на вход счетчика 11 подается единичный код с выхода генератора 21.

Параллельный код, получаемый на ш выходах счетчика 11, по командам с блока 17 выделения адресного кода записывается в блок 18 регистров памяти. Записываемый в блок регистров код с высокой степенью точности соответствует значению линейно нарастающего напряжения, поступающего на вход первого преобразующего каскада. Параллельный код с выходов счетчика 11 записывается в блок регистров памяти в моменты, когда код на выходах преобразующих каскадов изменяется (начиная с нулевого) на единицу, например, 000....00; 000...01;

000...10 и т.д. Данный код, в связи с ограниченной точностью преобразуюU>.= М (0,.2 + о ; 2 + ° ..+ „, 2 J (l)

Так как в момент изменения на единицу кода на выходах преобразующих каскадов напряжение остатка 0 на аналоговом выходе последнего каскада равно нулю, то (О -a U ) 2 — a U ) 2-...-a U = 0 (2)

llew 1 о 2 о с о

Можно переписать, раскрывая в (2) скобки

=aU„(2+@U, ) 2 +...+

+ a U, /2 (3) 45 где U — эталонное напряжение в

01

i-oM преобразующем каскаде.

Поскольку величины U из-за их

Ос нестабильности точно не определены, то получаемый код А = а а ...а 50 е не может быть использован непосредственно (для отождествления с измеряемой величиной U ), а будет использоваться в качестве адреса для извлечения из блока регистров па- 55 мяти кода N„ с высокой точностью, соответствующего величине Бо, =

М > 0

f на 0 выходах преобразующих каскадов.

Таким образом, в режиме коррекции устанавливается четкое однозначное соответствие между напряжением на входе первого преобразующего каскада Uz, кодом адреса А на логических выходах преобразующих каскадов и значением параллельного кода N„ на выходе счетчика 11. 25

Учитывая данное соответствие вели.чинПп, =M,A; =N,N„, гдеМ1иN2— нормирующие коэффициенты, можно записать

В режиме измерения измеряемый сигнал подается через. входное устI ройство 1, коммутатор 3 и сумматор

4 на вход первого преобразующего каскада. Иа логических выходах преобразующих каскадов вырабатывается код адреса, а на аналоговом выходе последнего преобразующего каскада вырабатывается сигнал величина которого равна значению напряжения остатка.

Uc (Ux a

2; ..— à U)x (4) ем

Раскрывая скобку, можно переписать о (U„- U /2 = -а(Бо, /2 + a U„ /2+

+...аешь =О, (5) Учитывая (1) и (3) мощно записать (6) Б,= М Я1+ Бс/2

Величина N; находится путем извлечения ее из блока регистров памяти в соответствии с адресом А, полученным на.выходах преобразующих каскадов. Напряжение остатка

U0; начиная со второго цикла кодирования, вновь подается на вход первого преобразующего каскада с помощью ячеек 12 и 13 памяти и коммутатора 3. Второй и последующие циклы преобразования происходят аналогич-, ным образом. Через и циклов преобра- . зования на выходах арифметического устройства вырабатывается 7 и рази рядный код, получаемый с учетом старшинства разрядов путем суммирования двоичных чисел Nl,N,...,N„ э э э получаемых на выходах блока регистров памяти, в соответствии с адресами А<, А,..., A„.

Второй режим измерения отличается от первого тем, что после установления напряжения остатка U е на выходе последнего преобразу1ощего каскада, на второй вход сумматора 4 подается линейно нарастающее напряжение По с выхода генератора 20. Одновременно с -подачей напряжения По на вход счетчика 11 подаются импульсы единичного кода с вихода генератора 21. Подача импульсов и изменение линейно нарастающего напряжения прекращаются

1 f 70606

5 0„= М (N,, — S) + Uà/2" °

U>= (U„- U„— я V„/õ2 — а, Пор /х2 ... аеИо.е,/х2

Составитель А. Кузнецов

Редактор И.Касарда Техред Л.Микеш

Корректор В. Бутяга

Заказ 4714/53 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 после изменения кода А на выходах

4 преобразующих каскадов на единицу, т ° е. с А на А, синхронно с

i 41 последующим кодовым импульсом, поступающим после изменения кода адреса А,,, В результате указанных действий на логических выходах преобразующих каскадов устанавливается код адреса А;,, на выходах блока регистров памяти — код Ы

11 на выходах счетчика — число S, на выходе интегратора — напряжение

Н„ = М Б, а на аналоговом выходе .последнего преобразующего каскада напряжение остатка U

Раскрывая скобки и учитывая (1) и (3) можно записать

Также как и в первом режиме измерения остаток Бе во втором цикле кодирования вновь подается на вход сумматора 4 и процесс преобразования происходит аналогичным образом. Код измеряемого сигнала получается путем суммирования (с учетом разрядности) и величин (N„ — S), получаемых в и циклах преобразования.

Время преобразования уменьшаетсН. При этом использование точного цифрового значения существенно повышает точность преобразования.