Умножитель

Иллюстрации

Показать всеРеферат

УМНОЖИТЕЛЬ, содержащий генератор тактовых импульсов, элемент И, два управляемых делителя частоты, реверсивный счетчик и схему сравнения, первый вход которой соединен с выходом реверсивного счетчика, отличающийся тем, что, с целью йовьшения быстродействия, в него введены делитель частоты, два двухвходовых и четырехвходовый многоразрядные сумматоры, два управляемых делителя частоты, восемь коммутаторов, семь реверсивных счетчиков, три схемы сравнения и четыре многоразрядных вьиитателя, причем выход генератора тактовых импульсов соединен с первыми управляющими входами делителя частоты и всех управляемых делителей частоты, выход делителя частоты соединен с информационными входами первого , второго, третьего и четвертого коммутаторов, первый и второй выходы которых соединены соответственно с суммирующими и вьмитающими входами первого, второго, третьего и четвертого реверсивных счетчиков, выходы которых соединены соответственно с первыми BxoAaMii первого, второго, третьего и четвертого многоразрядных вычитателей, выходы которых соединены соответственно с информационными входами первого, второго, третьего и четвертого управляемых делителей частоты, выходы соединены соответственно с информационными входа1-1и пятого, шестого, седьмого и восьмого коммутаторов, первый и второй выходы пятого и шестого коммутаторов соединены соответственно с суммирующими и вычитающиьш входами пятого и шестого реверсивных счетчиков, а первый и второй выходы седьмого и (Л восьмого коммутаторов соединены соотс ветственно с вычитающими и cyм Dфyющими входами седьмого и восьмого реверсивных счетчиков, выходы пятого, шестого, седьмого и восьмого реверсивных счетчиков соединены с информационными входами четырехвходового многоразрядного сумматора, выход которого соединен с выходом устройства, входы знаков сомножителей которого соединены с первым и вторым входами | первого двухвходового многоразрядного 00 4 сумматора, выход которого соединен с вторым входом первой схемы сравнения, выходы Больше всех схем сравнения соединены с первыми управляющими входами соответствующих пар коммутаторов, вторые управляющие входы которых соединены с вторыми входами всех многоразрядных вычитателей и с выходами Меньще всех схем сравнения, выходы Сравнение которых соединены с вторыми Управляющими входами соответствующих управляемых делителей частоты

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (111 (51)4 С 06 F 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOIVlY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3703861:/24-24 (22) 22.02.84 (46) 07.08.85. Бюл. h 29 (72) В.Ф.Евдокимов, Н.Ю.Пивень, Ю.А.Плющ, В.В.Реутов и З.А.Джирквелишв или. (71) Институт проблем моделирования в энергетике АН Украинской. ССР (53) 681 ° 325(088.8) (56) Авторское свидетельство СССР

Ф 392495, кл. С 06 F 7/52, 1973.

Авторское свидетельство СССР

У 590735, кл. С 06 F 7/52, 1978. (54)(57) УМНОЖИТЕЛЬ, содержащий генератор тактовых импульсов, элемент И, два управляемых делителя частоты, реверсивный счетчик и схему сравнения, первый вход которой соединен с выходом реверсивного счетчика, о т л и— ч а ю шийся тем, что, с целью

Повышения быстродействия, в него введены делитель частоты, два двухвходовых и четырехвходовый многоразрядные сумматоры, два управляемых дели-

1 теля частоты, восемь коммутаторов, семь реверсивных счетчиков, три схемы сравнения и четыре многоразрядных вычитателя, причем выход генератора тактовых импульсов соединен с первыми управляющими входами делителя частоты и всех управляемых делителей частоты, выход делителя частоты соединен с информационными входами первого, второго, третьего и четвертого коммутаторов, первый и второй выходы которых соединены соответственно с суммирующими и вычитающими входами первого, второго, третьего и четвертого реверсивных счетчиков, выходы которых соединены соответственно с первыми входами первого, второго, третьего и четвертого многоразрядных вычитателей, выходы которых соединены соответственно с информационными входами первого, второго, третьего и четвертого управляемых делителей частоты, выходы ко орых соединены соответственно с информационными входами пятого, шестого, седьмого и восьмого коммутаторов, первый и второй выходы пятого и шестого коммутаторов соединены соответственно с суммирующими и вычитающими входами пятого и шестого реверсивных счетчиков, Ж а первый и второй выходы седьмого и восьмого коммутаторов соединены соот- %Ф У ветственно с вычитающими и суммирую- С щими входами седьмого и восьмого реверсивных счетчиков, выходы пятого, ыестого, седьмого и восьмого реверсивных счетчиков соединены с информационными входами четырехвходового многоразрядного сумматора, выход которого соединен с выходом устройства, входы знаков сомножителей которого соединены с первым и вторым входами первого двухвходового многоразрядного сумматора, выход которого соединен с вторым входом первой схемы сравнения, выходы "Больше" всех схем сравнения соединены с первыми управляющиМи входами соответствующих пар коммутаторов, вторые управляющие входы которых соединены с вторыми входами всех многоразрядных вычитателей и с выходами

"Меньше" всех схем сравнения, выходы

"Сравнение" которых соединены с вторыми управляющими входами соответствующих управляемых делителей частоты

1171784

30 и с входами элемента И, выход которого соединен с вторым управляющим входом делитепя частоты, выходы второго, третьего и четвертого реверсивных счетчиков соединены соответственно с первыми входами второй, третьей и четвертой схем сравнения, второй вход второй схемы сравнения соединен с выходом второго двухвходового многоИзобретение относится к цифровым (дискретным) вычислительным машинам, в которых по меньшей мере часть вычислений осуществляется с помощью электрических устройств, к устройствам 5 для обработки данных с воздействием на порядок их расположения или на содержание обрабатываемых данных, в частности, для умножения, и может быть использовано в различных устройствах цифровых (дискретных) вычислительных машин.

Целью изобретения является повышение быстродействия устройства.

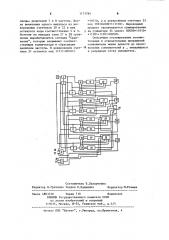

На чертеже представлена структур- 15 ная схема умножителя.

Устройство содержит генератор 1 импульсов, делитель 2 частоты, элемент И 3, первый 4 и второй 5 двухвходовые многоразрядные сумматоры, 10 управляемые делители 6-9 частоты, коммутаторы 10-17, реверсивные.счетчики 18-25, схемы 26-29 сравнения, многоразрядные вычитатели 30-33, четырехвходовый многоразрядный сумматор 25

34, выход 35 устройства, входы знаков первого 35 и второго 36 сомножителей, входы абсолютной величины первого 37 и второго 38 сомножителя.

Предлагаемое устройство работает следующим образом.

Числа в дополнительном коде, умножение которых производится в устройстве, можно представить как х = Ъ /

A х и у1=y,y, где х и у — знаки 35 чисел, а х и у — абсолютные величины

Юl г г при х=О и y=O или дополнения абсолют" ных величин при х=1, у=1.

Рассмотрим работу умножителя на примере двух чисел: х =2 и у =3 при щ

9 разрядного сумматора, первый и второй входы которого соединены с входами абсолютной величины сомножителей устройства и с вторыми входами третьей и четвертой схем сравнения соответственно, третьи входы которых соединены соответственно с первым и вто рым входами первого двухвходового многоразрядного сумматора.

2. этом х=0, х=.2, у=О, у 3. В исходном состоянии на входы 36-39 поданы нулевые коды, все реверсивные счетчики

18-25 сброшены в нуль, схемы 26-29 сравнения по этой причине вырабатывают сигналы "Сравнение", которыми сбрасываются управляемые делители

6-9 частоты и через элемент И 3 сбрасывают делитель частоты 2, в результате чего импульсы из генератора 1 не поступают. После этого на вход 36 .ъ» поступает знак х=О числа х, который далее поступает на схему 28 сравнения и на вход сумматора 4. На вход

37 поступает знак y=0 числа у, кото3 рый поступает на схему 29 сравнения и второй вход сумматора 4, с выхода которого результат 00 поступает насхему 26 сравнения. На вход 38 поступает абсолютная величина х=2, которая подается на схему 29 сравнения, а также на вход сумматора 5. На вход

39 поступает абсолютная величина у=3, которая подается на схему 28 сравнения, а также на вход сумматора

5, с выхода которого результат 2+3=5 подается на схему 27 сравнения.

После этого схемы 26-29 сравнения вырабатывают сигналы "Больше", которые откроют коьыутаторы 10-14 и 16 для поступления импульсов на суммирующие входы реверсивных счетчиков

18-22 и 24 и на. коммутаторы 15 и 17 для поступления импульсов на вычитающие входы реверсивных счетчиков 23 и 25, где насчитываются дополнения.

Одновременно снимается сброс со всех делителей частоты и импульсы из генератора 1 импульсов начинают поступать во все делители и счетчики. В нлчя! 171784 реверсивный счетчик 21 заносится один импульс, т.е. двоичный код 00001, а в реверсивных счетчиках 23 и 25 после вычитания одного импульса будут дво— ичные коды 11111. Управляющие коэффи- 2 циенты на управляющих входах делителей 6-9 установятся равными 2. После занесения третьих импульсов в реверсивные счетчики 20, 22 и 24 в реверсивный счетчик 21 заносятся еще два Зр импульса и хранится код 00011, а из реверсивных счетчиков 23 и 25 вычитаются еще по два импульса и хранятся коды 11101. Кроме того, схема 29 сравнения вырабатывает сигнал "Сравнение" З5

1 который сбрасывает .управляемый делитель 9 частоты и закрывает коммутаторы 16 и 17. На информационных входах делителей 7 и 9 частоты устанавливаются управляющие коэффициенты 3.

После занесения четвертых импульсов в реверсивные счетчики 20 и 22 в реверсивный счетчик 21 заносятся еще три импульса и хранится код 00110, а иэ реверсивного счетчика 23 вычитаются- еще три импульса и хранится код 11010. Кроме того, схема 28 сравнения вырабатывает сигнал "Сравнение", который сбрасывает управляемь«« дели45 тель 8 частоты и закрывает коимутато- 5О ры 14 и 15. На информационном входе делителя 7 частоты устанавливается управляющий коэффициент 4. После занесения двух очередных импульсов в реверсивный счетчик 20 в реверсивный счетчик 7t заносятся еще четыре и пять импульсов и хранится код 11111, после этого схема 27 сравнения вырале работы, так как на выходах Меньаге" схем 26-29 — нулевые сигналы, нулевые коды с выходов реверсивных счетчиков 18, 20, 22 и 24 через вычитатели 30-33 поступают на информа- 5 ционные входы управляемых делителей

6-9 частоты, т.е. в начале работы устанавливаются нулевые управляющие коэффициенты. После занесения в реверсивные счетчики 18 и 20, 22 и 24 первых импульсов в реверсивных счетчиках 19, 21, 23 и 25 сохраняются нулевые коды, но управляющие коэффициенты уже равны 1. Кроме того, на выходе схемы 26 сравнения появляется r5 сигнал "Сравнение", которым сбрасывается управляемый делитель 6 частоты и закрываются коммутаторы 10 и 11.

После занесения в реверсивные счетчики 20, 22 и 24 вторых импульсов в 20 оатывас.т cHI нал Сравнение, кото!«ый сбрасывает управляемый делитель 7 частоты и закрывает коммутаторы 12 и

13, и с выхода элемента И 3 сбрасывается делитель 2. Переходный процесс в схеме завершается сул«мированиеи чисел 00000 + 11111 + 11010 + 11101 соответственно с реверсивных счетчиков 19, 21, 23 и 25 на сумматоре 34, после чего rra выходе 35 появляется результат 00110, т.е. 2к3 = 6. Если теперь какой-либо из сомножителей или оба сомножителя получат положительное приращение, то соответствующая схема сравнения выработает на первом выходе сигнал Больше", откроет соответствующие коммутаторы и устранит сброс с соответствующего управляемого делителя и делителя 2 частоты, после чего полученное приращение сработается аналогично описанному. Если один из сол«ножителей (или оба сомножителя) получит отрицательное приращение, то работа устройства несколько изменится. Допустим, отрицательное приращение — 1 получил сомножитель у = 3, т.е. у =3-1=2. Тогда примем за исходное положение момент окончания переходного процесса в примере

2x3=6, т.е. в исходном состоянии с выхода реверсивного счетчика 22 через вычитатель 32 на информационный вход управляемого делителя 8 частоты подается коэффициент 4, а с выхода реверсивного счетчика 20 через вычитатель 31 на информационный вход делителя 7 частоты подается коэффициент

6. После прихода приращения — 1 на вход 39 оно поступает на вход схел«ь«

28 сравнения. С выхода сумматора 5 результат 2+2=4 поступает на вход схемы 27 сравнения. На выходах схем

27 и 28 сравнения вырабатываются сигналы "Меньше", которые поступают в младший разряд вычитателей 31 и 32.

Управляющий коэффициент 6-1=5 .с выхода вычитателя 31 устанавливается на информационном выходе делителя 7 частоты, а управляющий коэффициент 4-1

=3 — на информационном входе делителя 8 частоты. Сигналы "Меньше" открывают коммутаторы 12-14 так, что импульсы поступают на вычитающие входы реверсивных счетчиков 20-22, а импульсы с выхода коммутатора 15— на сул«мирующий вход реверсивного счетчика 23, кроме того, снимается сброс с делителя 2 частоты и управ.

1171784

Составитель Е.Захарченко

Редактор Л.Гратилло Техред О.Ващишина Корректор М.Розман

Заказ 4863/40 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г.Ужгород, ул.Проектная, 4 ляемьы делителей 7 и 8 частоты. После вычитания одного импульса из реверсивных счетчиков 20 и 22. в них останутся коды соответственно 5 и 3.

Поэтому на выходах схем 2? и 28 сравнения вырабатываются сигналы "Срав11 нение, которые закрывают соответствукщие коммутаторы и сбрасывают делители, частоты. В реверсивном счетчике 21 остается код 11111-00101=

=11010, а в реверсивном счетчике 23 код 11010+00011=11101. Переходный процесс заканчивается суммированием на сумматоре 34 числе: 00000+11010+

+ 1 1 101+ 1,1 101 =00100.

Описанным отслеживанием положительных и отрицательных приращений сомножители можно довести до произ10 вольных сомножителей 11, умещающихся в разрядную сетку умножителя.