Устройство для запуска логического анализатора

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ЗАПУСКА ЛОГИЧЕСКОГО АНАЛИЗАТОРА, содержащее блок распознавания параллельного ко-, да, узел фиксации распознавания, триггер подготовки, блок синхронизации , блок цифровой задержки, узел сброса триггера подготовки, входы данных, вход внешнего синхросигнала, вход сигнала подготовки, выход сигнала запуска по коду, выход сигнала задержанного запуска, входы сигналов установки цифровой задержки, входы внутренних синхросигналов и выходы кодовых разрядов цифровой задержки, причем входы данных устройства подключены к информатдионному входу блока распознавания параллельного кода, выход которого соединен с информационным входом узла фиксации ра.спознавания , синхронизирующий и управляюпцй входы которого соединены соответственно с первым выходом блока синхронизации и с выходом триггера подготовки, выход узла фиксации распознавания соединен с выходом сигнала запуска по коду и с входом запуска блока цифровой задержки, установочный вход которого соединен : входами сигналов установки цифровой задержки, синхровход блока цифровой задержки соединен с вторым выходом блока синхронизации и первым входом узла сброса триггера подготовки, а первый и второй информационные выходы блока цифровой задержки соединены соответ-, ственно с выходами кодовых разрядов цифровой задержки устройства и выходом сигнала /задержанного запуска устройства , третий выход блока синхронизации соединен с синхровходоь блока распознавания параллельного кода, вход сигнала подготовки устройства соединен с единичным входом триггера подготовки, вход внешнего синхросигi нала подключен к входу блока синхронизации , а второй и третий входы уз (Л С ла сброса триггера подготовки соединены с входами внутренних синхросигналов устройства и с выходом сигнала задержанного запуска устройства соответственно , от|1Ичающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности запуска по заданному числу взаимосвязанных пар по следовательных событий, в него ;р введены элемент 2 И-ИЛИ и переключа4 тель, при этом выход элемента 2 И-ИПИ подключен к первому входу триггера подготовки, первый вход первого элемента И элемента 2 И-ИЛИ подключен к выходу узла сброса триггера подготовки, а первый и второй входы второго Элемента И элемента 2 И-Шта соединены соответственно с выходом узла фиксации распознавания и с первьм контактом переключателя, второй и третий контакты которого подключены к входам Логическая единица и Логический нуль соответственно .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (5!)4 Г 06 F 11/00

ОПИСАНИЕ ИЗОБРЕТ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3645580/24-24 (22) 27.09.83 (46) 07.08.85. Вюл. Р 29 .(72) П.П. Алексеев, К.А. Тынсон, В.Е. Добровинский и М.А. Пильв (53) 681. 3 (088. 8) (56) Анализатор логических состояний шестнадцатиканальный 806. Проспект

2,3. 1., ЦООНТИ "Экос", 1978, Патент СИА Ф 4040025, кл. G 06 F 3/14, опублик. 1977, (54)(57) УСТРОЙСТВО JPIH ЗАПУСКА ЛОГИЧЕСКОГО АНАЛИЗАТОРА, содержащее блок распознавания параллельного кода, узел фиксации распознавания, триггер подготовки, блок синхронизации, блок цифровой задержки, узел сброса триггера подготовки, входы данных, вход внешнего синхросигнала, вход сигнала подготовки, выход сигнала запуска по коду, выход сигнала задержанного запуска, входы сигналов установки цифровой задержки, входы внутренних синхросигналов и выходы кодовых разрядов цифровой задержки, причем входы данных устройства подключены к информационному входу блока распознавания параллельного кода, выход которого соединен с информационным входом узла фиксации распознавания, синхронизирующнй и управляющий входы которого соединены cooiветственно с первым выходом блока синхронизации и с выходом триггера подготовки, выход узла фиксации распознавания соединен с выходом сигнала запуска по коду и с входом запуска блока цифровой задержки, установочный вход которого соединен с входами сигналов установки цифровой задержки, синхровход блока цифровой задержки

„„SU„„1 1794 A соединен с вторым выходом блока синхронизации и первым входом узла сброса триггера подготовки, а первый и второй информационные выходы блока цифровой задержки соединены соответ-, ственно с выходами кодовых разрядов цифровой задержки устройства и выходом сигнала, задержанного запуска устройства, третий выход блока синхронизации соединен с синхровходом блока распознавания параллельного кода, вход сигнала подготовки устройства соединен с единичным входом триггера подготовки, вход внешнего синхросигнала подключен к входу блока синхронизации, а второй и третий входы узла сброса триггера подготовки соединены с входамн внутренних синхросигналов устройства и с выходом сигнала задержанного запуска устройства соответственно, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности запуска по заданному числу взаимосвязанных пар последовательных событий, в него введены элемент 2 И-ИПИ и переключатель, при этом выход элемента

2 И-ИЛИ подключен к первому входу триггера подготовки, первый вход первого элемента И элемента 2 И-ИЛИ подключен к выходу узла сброса триггера подготовки, а первый и второй входы второго элемента И элемента

2 И-ИЛИ соединены соответственно с выходом узла фиксации распознавания и с первым контактом переключателя, второй и третий контакты которого подключены к входам "Логическая единица" и "Логический нуль" соответственно.

1171

Изобретение относится к области радиоизмерительной техники и может быть использовано Дпя запуска логических анализаторов различного класса и назначения. 5

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения возможности запуска по заданному числу взаимосвязанных пар последо- 10 вательных событий °

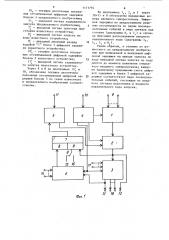

На фиг. 1 изображено предлагаемое устройство для запуска логического анализатора; на фиг. 2 — временные диаграммы. 15

Устройство состоит из блока 1 распознавания параллельного кода, узла 2 фиксации распознавания, блока 3 цифровой задержки, блока 4 синхронизации, .триггера 5 подготов- 20 ки, узла 6 сброса триггера подготовки, элемента 7 типа 2 И-ИЛИ, переключателя 8 режимов запуска, входов 9 данных, входа 10 внешнего синхросигнала, входа 11 сигнала подго- 25 товки, выхода 12 сигнала запуска по коду, выхода 13 сигнала задержанного запуска, входов 14 внутренних синхросигналов логического анализатора, входов 15 и 16 соответственно З0 потенциалов Логический нуль" и

"Логическая единица", входов 17 сигналов установки цифровой задержки, выходов 18 кодовых разрядов цифровой задержки.

Устройство работает следующим образом.

При отключенной или включенной, но установленной в "0 цифровой задержке независимо от положения переключателя 8 работа предлагаемого устройства для запуска аналогична работе известного.

При включенной и ненулевой цифровой задержке и при подключениии переключателя 8 режимов запуска к входу 15 "Логический нуль" работа предлагаемого устройства также аналогична работе известного.

При включенной и ненулевой цифро- 50 вой задержке и при подключении переключателя 8 к входу 16 "Логическая единица" выходной сигнал запуска по коду с выхода узла 2 фиксации распознавания через второй вход второго 55 элемента И элемента 7 устанавливает в 0 выходной сигнал триггера 5 подготовки. По очередному внешнему

794 сихросигналу последовательно во времени происходит увеличение отсчета цифровой задержки на единицу в блоке

3 и переключение в "0" выходного сигнала узла 2 фиксации распознавания (так как выходной сигнал триггера 5 подготовки находится в состоянии логического "0", запрещая фиксацию распознавания в узле 2). ,Выходной сигнал узла 2, находящийся в состоянии логического "0", запрещает по всем последующим внешним синхросигналам отсчет цифровой задержки блоком 3.

Отсчет цифровой задержки продолжается при появлении на входах 11 и 9 (при наличии внешнего синхросигнала на входе 1 0) очередной пары последовательных событий: сигнала подготовки и параллельного кода (запуска) соответственно.

После окончания отсчета цифровой задержки независимо от положения переключателя 8 режимов запуска по выходному сигналу блока 6 через вход первого элемента И элемента 7 триггер 5 !

1 fl подготовки. устанавливается в 0

Описанный принцип работы предлагаемого устройства иллюстрируется детальными временными диаграммами (для сравнения на фиг. 2 приведены детальные временные диаграммы функционирования известного устройства), где 1 — внешний синхросигнал;

2 — сигнал синхронизации блока

3 цифровой задержки, получаемый с одного из выходов блока 4 синхронизации;

3 — сигнал синхронизации узла 2

1 фиксации распознавания, получаемый с одного из выходов блока 4 синхронизации;

4 — сигнал синхронизации блока 1 t распознавания, получаемый с блока 4 синхронизации;

5 — выходной сигнал распознава1 ния по коду блока 1 распознавания;

6 — входной сигнал подготовки;

7 — .выходной сигнал триггера

1 подготовки предлагаемого изобретения

8 — выходной сигнал узла 2 фикса1 ции распознавания предлагаемого изобретения (выходной сигнал запуска по коду схемы запуска);

9 — выходной двоичный разряд

1 кодовой "1" блока 3 цифровой задержки предлагаемого изобретения; з 11717

10 — текущие десятичные показания отсчитываемой цифровой задержки блоком 3 предлагаемо.го изобретения;

11 — выходной сигнал задержанного запуска предлагаемого изобретения; 5

7f

7 — выходной сигнал триггера подготовки известного устройства;

8(8 — выходнои сигнал запуска по коду известного устройства

%

9 — выходной двоичный разряд

1 и м !

О кодовой ".1" блока 3 цифровой задержки известного устройства (У

10> — текущее десятичное показание отсчитываемой цифровой задержки блоком 3 известного устройства 15 !

Э

11 — выходной сигнал задержанного зайуска известного устройства.

Через К и N на диаграммах 10 и

10„ обозначено текущее десятичное показание отсчитываемой цифровой за- 20 держки блоком 3 по схеме известного и предлагаемого изобретений соответственно.

94

На диаграммах 1, 2,и 3 через

Э (К+1) и N обозначены порядковые номера внешнего синхросигнала. Цифровая задержка по предлагаемому решению отсчитывается по парам последовательных событий в виде сигнала под. готовки (диаграммы 6 и 7 ) и сигна1 1 ла фиксации распознавания входного параллельного кода (диаграммы 3.1, 4„, 5„и 8„) °

Таким образом, в отличие от известного по предлагаемому изобретению при включенной и ненулевой цифровой задержке на выходе запуска по коду выходной сигнал запуска по коду длится до момента появления очередного входного синхросигнала; каждому единичному приращению счета цифровой задержки в блоке 3 цифровой задержки соответствует. пара последовательных событий, состоящая иэ входного сигнала подготовки и входного параллельного кода запуска.

1171794 бремя

Фиг. Р

Составитель С. Старчихин

Редактор Л. Гратилло Техред C,йовжий Корректор В. Бутяга

Заказ 4864/41 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4