Сигнатурный анализатор

Иллюстрации

Показать всеРеферат

СИГНАТУРНЫЙ АНАЖЗАТОР, содержащий первьй и второй формирователи сигнатур, блок индикации,блок эталонных сигнатур, первый и второй блоки сравнения, первый счетчик, первый триггер, первый формирова .тель одиночных импульсов и первый ,элемент И, причем входы сброса всех разрядов первого формирователя сигнатур объединены с входами сброса всех разрядов, кроме первого, второго формирователя сигнатур и через первый формирователь одиночных импульсов подключены к входу запуска анализатора, информационный вход первого формирователя сигнатур является информационным входом анализатора , синхровход анализатора соединен с первьм входом первого элемента И, второй вход которого соединен с выходом первого триггера , а выход - с синхровходом формирователя сигнатур, группа информационных выходов блока эталонных сигнатур соединена с первой группой информационных входов первого блока сравнения, отличающийся тем, что, с целью расширения функциональных возможностей анализатора за счет обеспечения возможности выделения из сигнатуры диагностической информации о месте неисправности, в него введены регистр ошибки, дешифратор отсутствия ошибки, второй счетчик , два триггера, два элемента И, элемент ИЛИ и два формирователя одиночных импульсов, причем группа, выходов первого формирователя сигнатур связана с второй группой информационных входов первого блока сравнения и с первой группой информационных входов блока индикации, вторая группа информационных входов которого соединена с информационными выходами .второго счетчика, третий информационный вход блока индикации соединен .с S выходом дешифратора отсутствия ошибки (Л и со счетным входом второго триггера , инверсньм выход которого подключен к третьему входу первого элемента И, группа выходов второго формирО вателя сигнатур соединена с первой группой информационных входов второго блока сравнения, вторая группа, информационных входов которого связана с группой информационных входов дешифратора отсутствия ошибки и с группой СР выходов регистра ошибки, группа инг формационных входов которого соеди sl нена с выходами первого блока сравнения , управляющий вход второго блока сравнениясоединен с первым входом второго элемента И, синхровходом второго формирователя сигнатур и с первым входом элемента ИЛИ, второй вход которого соединен с синхровходом первого формирователя сигнатур и с выходом третьего элемента И, а выход подключен к счетному входу первого счетчика, первый выход которого подключен к первому входу третьего элемента И и к входу запуска второго

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (l9) (I I). (>>)4 С 06 F 11 16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

00 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3711962/24-24 (22) 16.03.84 (46) 07.08.85. Бюл. Р 29 (72) Е,И. Николаев, Е.З. Храпко и А.В. Горохов (53) 681.3(088 ° 8) (56) Электроника, 1977, Р 5, с. 23"33.

Авторское свидетельство СССР

Р 890396, кл. G 06 F 11/00, 1980. (54)(57) СИГНАТУРНЫЙ АНАЛИЗАТОР, содержащий первый и второй формирователи сигнатур, блок индикации, блок эталонных сигнатур, первый и второй блоки сравнения, первый счетчик, первый триггер, первый формирователь одиночных импульсов и первый ,элемент И, причем входы сброса всех разрядов первого формирователя сигнатур объединены с входами сбро- са всех разрядов, кроме первого, второго формирователя сигнатур и через первый формирователь одиночных импульсов подключены к входу запуска анализатора, информационный вход первого формирователя сигнатур является информационным входом анализатора, синхровход анализатора соединен с первым входом первого элемента И, второй вход которого соединен с выходом первого триггера, а выход — с синхровходом формирователя сигнатур, группа информационных выходов блока эталонных сигнатур соединена с первой группой информационных входов первого блока сравнения, отличающийся тем, что, с целью расширения функциональных возможностей анализатора за счет обеспечения возможности выделения из сигнатуры диагностической информации о месте неисправности, в него введены регистр ошибки, дешифратор отсутствия ошибки, второй счетчик, два триггера, два элемента И, элемент ИЛИ и два формирователя одиночных импульсов, причем группа выходов первого формирователя сигнатур связана с второй группой информационных входов первого блока сравнения и с первой группой информационных входов блока индикации, вторая группа информационных входов которого соединена с информационными выходами второго счетчика, третий информационный вход блока индикации соединен с выходом дешифратора отсутствия ошибки и со счетным входом второго триггера, инверсный выход которого подключен к третьему входу первого элемента И, группа выходов второго формиро вателя сигнатур соединена с первой группой информационных входов второго блока сравнения, вторая группа информационных входов которого связана с группой информационных входов дешифратора отсутствия ошибки и с группой выходов регистра ошибки, группа ин-. формационных входов которого соединена с выходами первого блока сравнения, управляющий вход второго блока сравнения- соединен с первым входом второго элемента И, синхровходом второго формирователя сигнатур и с первым входом элемента ИЛИ, второй вход которого соединен с синхровходом первого формирователя сигнатур и с выходом третьего элемента И, а выход подключен к счетному входу первого счетчика, первый выход которого подключен к первому входу третьего элемента И и к входу запуска второго

1171797 формирователя одиночных импульсов, второй выход первогд счетчика соединен с вторым входом третьего элемента И и четвертым входом элемента

ИЛИ, выход второго и вход запуска третьего формирователей одиночных импульсов объединены и подключены к управляющему входу регистра ошибки, выход третьего формирователя одиночных импульсов соединен со счетным нходом первого триггера и управляющим входом дешифратора отсутствия ошибки, синхровходы всех трех формирователей одиночных импульсов соединены с третьим входом третьего элемента И и с синхровходом анализатора, входы установки в ноль первого

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и диагностики логических блоков, блоков постоянной и перепрограммируемой памяти, в которых неисправность в одной ячейке памяти проявляется только на одном выходе блока и в одном слове, т.е. в одном блоке выходной последовательности, В

Целью изобретения является расширение функциональных возможностей анализатора за счет обеспечения возможности выделения из сигнатуры диагностической информации о месте неисправности.

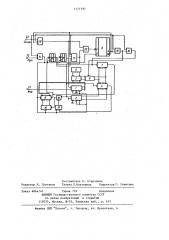

На чертеже приведена структурная схема сигнатурного анализатора.

Устройство содержит первый 1 и второй 2 формирователй сигнатур, 20 первый 3 и второй 4 блоки сравнения, блок 5 эталонных сигнатур, регистр 6 ошибки, дешифратор 7 отсутствия ошибки, блок 8 индикации, первый 9 и второй 10 счетчики, первый, второй д и третий триггеры 11 - 13, три формиронателя одиночных импульсов 1416, три элемента И 17 - l9, элемент

ИЛИ 20, информационный. вход 21,управ ляющий вход 22 "Пуск" и синхро30 вход 23.

При выявлении диагностической информации используется тот факт что и второго счетчиков, первого1 второго,и третьего триггеров, блока индикации и вход установки в единицу первого разряда второго формирователя сигнатур объединены и подключены к выходу первого формирователя одиночных импульсов, выход второго блока сравнения подключен к единичному входу третьего триггера, выход которого соединен с вторым входом второго элемента И, выход которого подключен к входу вычитания второго счетчика, информационный вход и вход сброса первого разряда второго формирователя сигнатур и нход установки в единицу первого разряда формирователя сигнатур соединеныс шинойлогического нуля. при одиночных ошибках в последовательности длины N (2 - 1 (где К вЂ” число

К разрядов регистра), поступающей на свертку в регистр с обратными связями через схему суммирования по модулю два, о бр азующий предельный мн о гочле н, сигнатура (свертка) несет в себе диагностическую информацию о месте ошибки в последовательности, Учитывая, что одиночные ошибки в блоках памяти наиболее вероятны, из сигнатуры можно выделить эту информацию, используя принцип суперпозиции (независимости рассмотрения воздействия полезной информации и ошибки на линейную систему — регистр с обратными связями, через схему суммирования по модулю два).

Работа анализатора основана на свертке анализируемой двои ной последовательности с помощью формиронателя 1 сигнатур, на сравнении ее с эталонной сигнатурой на блоке 3, на получении синдрома ошибки на регистре 6, на анализе синдрома ошиб- ки на отсутствие ошибки в блоке 7, на однозначной идентификации в случае одиночной ошибки места ошибки в анализируемой последонательности на блоках,2, 4, 13, 18 и 10 и на индикации места ошибки на индикаторе

8 в виде порядкового номера ошибки з

Анализатор работает следующим образом.

По внешнему управляющему сигналу

lt 11

Пуск первый формирователь 14 одиночного импульса выдает сигнал, по которому блоки 1,2,8,9,10,11,12 и

13 устанавливаются в исходные состо ния, причем все разряды формирова" теля 1 сигнатур и разряды формирователя 2 сигнатур (кроме первого) устанавливаются в нуль, а первый разряд формирователя 2 сигнатур— в единицу. Счетчик 10 устанавливается в состояние N, где N — число бит в последовательности, поступающей на информационный вход 21 сигнатурного анализатора.

Анализируемая последовательность поступает на информационный вход формирователя 1 сигнатур и по синхро импульсам с входа 23 сворачивается в сигнатуру. Результат свертки яндицируется на индикаторе 8 и поступает на первый блок 3 сравнения, куда также поступает эталонная сигнатура из блока 5.

Информация с выхода блока 3, пред ставляющая собой вектор ошибки, по сигналу с формирователя 15 одиночного импульса фиксируется на регистре 6. Вектор ошибки анализируется при поступлении на блок 7 управляющего сигнала с выхода третьего формирователя 16 одиночного импульса.

Блок 7 при этом настроен на нулевую комбинацию. В случае отсутствия ошибки (эталонная и полученная сигнатуры совпадают и вектор ошйбки равен нулю) с выхода дешифратора 7 на счетный вход триггера 12 поступает импульс, останавливающий работу управляющей части анализатора.

Этот же импульс поступает на индикатор 8, фиксируя верную анализируемую последовательность..

Если вектор ошибки не ранен нулю, что имеет место в случае несовпаде" ния эталонной и полученной сигнатур, то на выход блока 7 сигнал не проходит и работу управляющей части анализатора продолжается. Подачей управляющего сигнала с выхода второго формирователя 15 одиночного им" пульса на регистр 6 ошибки заканчи1171797 4 вается первая половина работы сигнатурного анализатора — режим контроля и начинается второй режим — диагнос тика неисправностей. Режим диагностики начинается с выдачи первым элементом И 17 пачки из N импульсов, я- поступающей на второй элемент И 18, блок 4 сравнения и синхровход второго формирователя 2 сигнатур. Эти

1р, импульсы через элемент И 18, открытый триггером 13, поступают на вычитающий вход счетчика 10, предварительно устанавленного в состояние N, Формирователи 1 и 2 сигнатур полностью совпадают по числу разрядов регистра и структуре обратных связей. Обратные связи выбраны так, чтобы в режиме .генерации регистр с последними перебирал предельное,число комбинаций М=2"-1, где К вЂ” число разрядов регистра. Разрядность регистра К выбрана из условия 2 N.

С момента поступления укаэанных импульсов формирователь 2 сигнатур д работает в режиме генерации, т.е. перебирает все возможные комбинации кроме нулевой, так как информационный вход его соединен с корпусом, а перед началом работы он установлен в состояние 100. О. Когда в формирователе 2 сигнатур появляется комбинация, совпадающая с вектором ошибки, зафиксированно на регистре

6 ошибки, блок 4 сравнения выдает сигнал, который через триггер 13 и

35 элемент И 18 прерывает пакет импульсов на входе счетчика 10. Если ошибка была íà i-ом такте последова" тельности, то импульс сравнения с

40 блока 4 появится на такте с номером (N-i) и через элемент И I8 на вычитающий вход счетчика 10 пройдет (N-i) импульсов. Состояние счетчика равно tN-(N-1)3 "-i и индицируется на индикаторе 8.

Таким образом, использование предложенного сигнатурного анализатора позволяет осуществлять не только режим контроля входных последовательностей, но и в случае наличия одиночной ошибки режим диагностки с автоматическим указанием местоположения ошибки в виде порядкового номера искаженного символа.

1171797

Составитель С. Старчихин

Редактор Л. Гратилло Техред Л.Мартяшова Корректор Г. Решетник

Заказ 4864/41 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", r. Ужгород, ул. Проектная, 4