Устройство управления обращением к памяти

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО УПРАВЛЕНИЯ ОБРАЩЕНИЕМ К ПА11ЯТИ, содержащее восемь элементов И, шесть элементов НЕ, триггер и элемент ИЛИ, причем первый вход запроса обращения устройства подключен к первому входу первого элемента И, второй вход которого подключен к выходу первого элемента НЕ, а выход через второй элемент НЕ подключен к первому входу второго элемента И, входы с второго по четвертый которого подключены соответственно к выходу третьего элемента НЕ, к установочному входу устройства и к выходу четвертого элемента НЕ, выход второго элемента И подключен к входу первого элемента НЕ и соединен с первым входом элемента ИЛИ, второй вход которого подключен к входу четвертого элемента НЕ и соединен с выходом третьего элемента И, входы с первого по четвертый которого подключены соответственно к выходу пер- . вого элемента НЕ, установочному входу устройства, вьрсоду пятого элемента НЕ и выходу шестого элемента НЕ, вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с вьгходом четвертого элемента НЕ, первый выход управления коммутацией источников запроса устройства подключен к первому входу элемента ИЛИ и соединен с первым входом пятого элемента И, второй вход которого соединен с первым входом шестого элемента И, второй вход которого соединен с вторым входом элемента ИЛИ и подключен к второму выходу управления коммутацией источников запроса устройства , выходы пятого и шестого элементов И подключены соответственно к первому и второму выходам подi тверждения приема запроса устройства , входы установки в 1 и установ Л ки в О триггера соединены соответственно с выходами пятого и шестого элементов И, прямой и инверсный выходы триггера подключены соответственно к первым входам седьмого и восьмого элементов И, вторые входы которых соединены с входом конца цикла ч1 обращения устройства, вход подтвержЗо дения приема запроса, которого соединен с первым входом шестого элемента И, выход седьмого элемента И подключен к входу третьего элемента НЕ и соединен с первым выходом конца цикла обращения устройства , второй выход конца цикла обращения которого соединен с выходом восьмого элемента И и подключен к входу пятого элемента НЕ, выход элемента ИЛИ подключен к выходу запроса обращения устройства, отличающееся тем, чтЪ, с целью повышения надежности путем обеспечения работоспособности при одновременном поступлении запросов

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (31! (5!)4 G 06 F 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ HOMHTET СССР

l10 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3701728/24-24 (22) 20.02.84 (46) 07.08.85. Бюл. № 29 (72) С.Ф.Жулинский и А.Н.Сергеев (53) 68 1.32(088.8) (56) Авторское свидетельство СССР № 374601, кл. G 06 F ..9/00, 1973.

Авторское свидетельство СССР № 877541, кл. G 06 F 9/30, 1981 (54 ) (5 7 ) УСТРОЙСТВО УПРАВЛЕНИЯ ОБРАН1ЕНИЕМ К ПАМЯТИ, содержащее восемь элементов И, шесть элементов НЕ, триггер и элемент ИЛИ, причем первый вход запроса обращения устройства подключен к первому входу первого элемента И, второй вход, которого подключен к выходу первого элемента

HE а выход через второй элемент

НЕ подключен к первому входу второго элемента И, входы с второго по четвертый которого подключены соответственно к выходу третьего элемента HE к установочному входу устройства и к выходу четвертого элемента НЕ, выход второго элемента И подключен к входу первого элемента

НЕ и соединен с первым входом элемента ИЛИ, второй вход которого подключен к входу четвертого элемента НЕ. и соединен с выходом третьего элемента И1 входы с первого по четвертый которого подключены соответственно к выходу первого элемента HE установочному входу устройства, выходу пятого элемента НЕ и выходу шестого элемента

HF, вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с выходом четвертого элемента HF., первый выход управления коммутацией источников запроса устройства подключен к первому входу элемента ИЛИ и соединен с первым входом пятого элемента И, второй вход которого соединен с первым входом шестого элемента И, второй вход которого соединен с вторым входом элемента ИЛИ и подключен к второму выходу управления коммутацией источников запроса устройства, выходы пятого и шестого элементов И подключены соответственно к первому и второму выходам подтверждения приема запроса устройства, входы установки в "1" и установки в "0" триггера соединены соответственно с выходами пятого и шестого элементов И, прямой и инверсный выходы триггера подключены соответственно к первым входам седьмого и восьмого элементов И, вторые входы которых соединены с входом конца цикла обращения устройства, вход подтверждения приема запроса. которого соединен с первым входом шестого элемента И, выход седьмого элемента И подключен к входу третьего элемента НЕ и соединен с первым выходом конца цикла обращения устройства, второй выход конца цикла обращения которого соединен с выходом восьмого элемента И и подключен к входу пятого элемента НЕ, выход элемента ИЛИ подключен к выходу запроса обращения устройства, о т л и ч а ю щ е е с я теи, что, с целью повышения надежности путем обеспечения работоспособности при одновременном поступлении запросов

117 ня обращение, оно содерж((т элемент

И-HF ф фо1.мировятель одиночного импульса и седьмой элемент НЕ, причем первый- вход запроса обращения устроиства через формировагель одиночного импульса подключен к первому

1801 ((х(э((у э.«(ем(нтя H-НЕ, в((х(эд которого подключен к второму входу четвертОГО эломс 1(тя <«f Второи Вход запрося обращения устройства через седьмой элемент НГ подключен к второму входу элемента И-НЕ.

В исходном состоянии на входы 18 и 19 устройства поступает низкий потенциал, а на входы 23-25 — высо— кий потенциал. Под действием этих потенциалов и импульса отрицательной полярности, поступающего на установочный вход 25 устройства и являющегося сигналом установки устройства в исходное состояние, в последнем в исходном состоянии высокий потенциал устанавливается на выходе элементов И 7 и 8, формирователя 22 одиночного импульса, элемента И-НЕ 21, элементов НЕ 9, 40

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для организации работы двух вычислительных машин на общее поле памяти.

Цель изобретения — повышение надежности путем обеспечения работоспособности при одновременном поступлении запросов на обращение к памяти, 1О

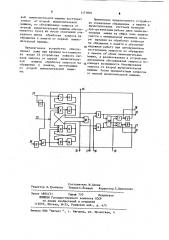

На чертеже изображена блок-схема устройства.

Устройство содержит восемь элементов И 1-8, семь элементов HF 9-15, элемент ИЛИ 16, выход 17 запрося 15 обращения, вход 18 подтверждения приема запроса, .вход 19 конца цикла обращения, триггер 20, элемент И-HF.

21, формирователь 22 одиночного импульса, первый и второй входы 23 20 и 24 запроса обращения, установочный вход 25, первый и второй выходы 26 и 27 подтверждения приема запроса, первый и второй выходы 28 и 29 кон- . ца цикла обращения, первый и второй 25 выходы 30 и 31 управления коммутацией источников запроса.

Устройство управления обращением к памяти работает следующим образом. 30

10, 12 и 13 и на одном (безразлично каком) выходе триггера 20, а низкий потенциал — на выходе элементов

И 1-6, элементов НЕ 11, 14 и 15, элемента ИЛИ 16, на одном из выходов триггера 20 и на выходах 17,26, 27, 28, 29, 30 и 3 1 устройства.

При появлении запроса на обращение к памяти от первой вычислительной машины низкий потенциал устанавливается на входе 23 устройства, я при появлении запроса на обращение к памяти от второй вычислительной машины — на входе 24 устройства. Пусть первым поступает запрос от первой вычислительной машины. Под действием низкого потенциала, установленного на входе 23, на выходе элементов И 7 и НЕ 12 устанавливается низкий потенциал, а на выходе элементов И 5, НЕ 11 и (1ЛИ 16 — высокий потенциал, тем самым на выходе 17 устройства формируется высокий потенциал, который является сигналом обращения к памяти, а на втором входе элемента И 6 устанавливается низкий потенциал, запрещающий обработку запроса на обращение к памяти от второй вычислительной машины. На выходе 30 устройства также устанавливается высокий потенциал, который используется для управления коммутатором, обеспечивающим подключение к памяти адресных и числовых шин от первой вычислительной машцны.

В таком состоянии устройство находится до момента появления на входе

18 сигнала сопровождения из памяти в виде импупьса положительной поляр- . ности, который свидетельствует о том, что сигнал обращения к памяти принят и вычислительная машина может снять запрос на обращение к памяти. При появлении сигнала сопровождения на вхо1171801 машины.

Если во время обработки устройством запроса на обращение к памяти от первой вычислительной машины поступает запрос на обращение к памяти от второй вычислительной машины, то под действием низкого потенциала на входе 24 устройства устанавливается высокий потенциал на четвертом входе элемента И 6.

Однако на выходе элемента И 6 сохраняется низкий потенциал до тех пор, пока на его втором входе действует низкий запрещающий потенциал, 45 де 18 устройства на выходе элемента

И 3 формируется импульс положительной полярности, который поступает на выход 26 устройства г> виде сигнала сопровождения, разрешающего первой вычислительной машине снять запрос на обращение к памяти, и. на.единичный вход триггера 20, при этом устанав ливается или подтверждается высокий потенциал на первом входе эле- 10 мента И 1. Такое состояние устройства сохраняется до момента прихода на вход 19 сигнала "Конец цикла в виде импульса положительной полярности. При этом на выходе эле- 15 мента И 1 формируется импульс положительной полярности, который посту" пает на выхбд 28 устройства в виде сигнала "Конец цикла", а через элемент НЕ 9 в виде импульса отрицатель-20 ной полярности поступает на первый вход элемента И 5 и устанавливает на выходе элементов И 5 и 7, HE 11 и 12 и ИЛИ 15 потенциалы, соответствующие исходному состоянию устрой- 25 ства. Тем самым снимается с второго входа элемента И 6 запрет на обработку запросов на обращение к памяти от второй вычислительной машины.

Величина задержки сигнала "Ko- З0 нец цикла" относительно сигнала сопровождения такова, что к моменту окончания действия на входе 19 устройства сигнала "Конец цикла" первая вычислительная машина снимает запрос на обращение к памяти.

С приходом на вход 19 устройства сигнала "Конец цикла в устройстве заканчивается цикл обработки запро са на обращение к памяти от первой 40 вычислительной машины и оно готово без задержки приступить к обработке последующих запросов, поступающих от первой или второй вычислительной который снимается только после окончания обработки запроса на обращение к памяти от первой вычислительной машины. После этого без какой-либо задержки устройство приступает к обработке запроса на обращение к памяти от второй вычислительной машины, устанавливая высокий потенциал на выходе элементов И 6 и ИЛИ 16 и низкий запрещающий потенциал на втором входе элемента И 5, тем самым запрещая обработку запроса на обращение к памяти от первой вычислитель ной машины, При одновременном поступлении от обеих вычислительных машин запросов на обращение к памяти очередность обработки строго определена: первым обрабатывается запрос. на обращение к памяти, поступающий от первой вычислительной машины на вход 23 устройства ° Такой режим обслуживания запросов обеспечен благодаря тому, что в момент поступления низкого потенциала на вход 23 устройства на выходе формирователя 22 одиночного импульса вырабатывается импульс отрицательной полярности с длительностью,превышающей время переходных процессов в элементах И 5 и 7, НЕ 11 и 12. Этот импульс поступает на первый вход элемента И-НЕ 21 и блокирует прохождение на вход элемента

И 8 сигнала запроса на обращение к памяти от второй вычислительной машины, поступающего в виде низкого потенциала на вход 24 устройства. Запрос от первой вычислительной машины может" поступать и во время обработки устройством запроса на обращение к памяти от второй вычислительной машины, в этом случае вырабатываемый формирователем 22 импульс отрицательной полярности не оказывает никакого влияния на работу устройства.

В предложенном устройстве управления обращением к памяти реализованы следующие дисциплины обслуживания: первый выставил вопрос — первым обслужен; если запросы поступают одновременно, то первым обслуживается запрос от первой вычислительной машины, а затем от второй; при постоянно существующих запросах от обеих вычислительных машин обеспечивается поочередное обслуживание их; если при постоянно существующем запросе от пер1171801 вой вычислительной машины поступает Применение предлагаемого устройстзапрос от второй вычислительной ва управления обращением к памяти в .машины, то обслуживание запроса от вычислительных системах позволит второй вычислительной машины обеспе- -при организации работы двух вычисли5 чивается сразу же после окончания оче- тельных машин на общее п л о щее поле памяти редного цикла обработки запроса на свести к минимальной величине потеобращение к памяти от первой вычис- Ри времени на обработку запроСов лительной машины. на обращение к памяти и обеспечит

1О надежную работу при одновременном

Предлагаемое устройство обеспе- поступлении запросов на обращение чивает даже при наличии постоянного к памяти от обеих вычислительных на входе 23 устройства ложного снг- машин, а реализованная в устройстве нала запроса от первой вычислитель- дисциплина обспуживания запросов исной машины обработку запросов на 1 ключает возможность блокирования обращение к памяти, поступающих от второй вычислительной маши- машины более приоритетным о тетным запросом от первой вычислительной машины.

Составитель М.Силин

Редактор Л.Гратилло Техред С.йовжий Корректор Л.Пилипенко

Заказ 4864/41 ТиРаж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент ", r. ужгород, ул. Проектная, 4