Устройство для записи информации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ЗАПИСИ ИНФОРМАЦИИ по авт. св. № 809352, отличающееся тем, что, с целью повышения надежности устройства, оно содержит элемент И-ИЛИ-НЕ и дополнительный элемент И, один вход которого соединен с выходом элемента И-ИЛИ-НЕ а другой является входом установки в «О, выход дополнительного элемента И подключен к установочной шине, одни входы элемента И-ИЛИНЕ соединены с соответствуюш,ими выходами блока ввода информации, а другие - с выходами триггеров. (Л CZ 00 4; |

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (ЗЦ4 G 11 С (/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 809352 (21) 3746134/24-24 (22) 28.05.84 (46) 07.08.85. Бюл. № 29 (72) Ю. С. Герасимов (53) 681.327.6 (088.8) (56) Авторское свидетельство СССР № 809352, кл. G 11 С 7/00, 1979. (54) (57) УСТРОЙСТВО ДЛЯ ЗАПИСИ

ИНФОРМАЦИИ по авт. св. № 809352, от„„gIJ„„1171847 личаюи!ееея тем, что, с целью повышения надежности устройства, оно содержит элемент И вЂ” ИЛИ вЂ” HE и дополнительный элемент И, один вход которого соединен с выходом элемента И вЂ” ИЛИ вЂ” НЕ а другой является входом установки в «О», выход дополнительного элемента И подключен к установочной шине, одни входы элемента И вЂ” ИЛИНЕ соединены с соответствующими выходами блока ввода информации, а другие — с выходами триггеров.

1171847

Изобретение относится к аппаратуре регистрации данных, может быть использовано в системе подготовки данных для записи информации в клавишных устройствах, и является дополнительным к авт. св.

Хе 809352.

Цель изобретения — повышение надежности устройства.

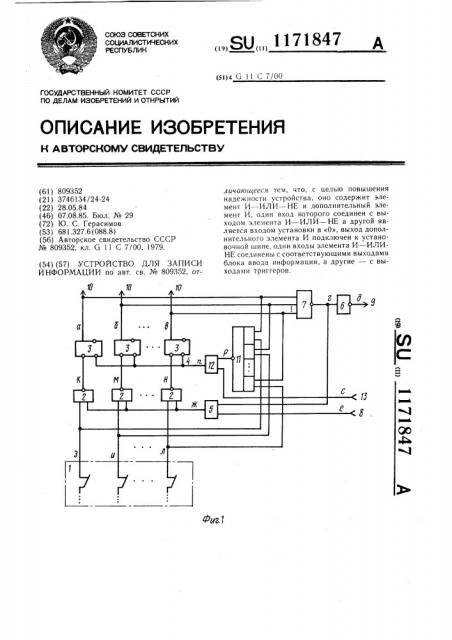

На фиг. 1 приведена принципиальная электрическая схема предложенного устройства; на фиг. 2 — эпюры напряжения в характерных точках схемы.

Устройство содержит блок 1 ввода информации, элементы И вЂ” НЕ 2, триггеры 3, установочную шину 4, элемент И 5, элемент НЕ 6, элемент ИЛИ вЂ” НЕ 7, шину 8 разрешения записи, выход 9, выходы 10 устройства, элемент И вЂ” ИЛИ вЂ” HE 11, дополнительный элемент И 12 и вход 13 установки в «О».

Устройство работает следующим. образом.

В исходном состоянии на выходах 10 присутствует сигнал логического «О». При этом, если на шине 8 разрешения записи присутствует сигнал логической «1», то с выхода элемента 5 сигнал логической «1» подается на входы элементов 2.

При размыкании одной из клавиш блока 1 сигнал логической «1» подается на вход элемента 2. Триггер 3 опрокидывается и на выходе элемента 7 появляется сигнал логического «О», который поступает на входы элементов 2. Тем самым перекрывается ввод информации из блока 1 в триггеры 8. После опрокидывания одного из триггеров 3 с выхода 9 выдается сигнал логической «1» на последующее аналогичное устройство или в схему индикации состояния триггеров 3.

С момента размыкания клавиш блока

1 до момента блокировки элементов 2 проходит до 100 нс, определяемое суммарным временем прохождения сигнала через элемент 2, триггер 3, элементы 7 и 5. В то же время при ручном размыкании клавиши блока 1 сигнал на информационном входе элемента 2 сохраняется в течение до 0,1 с.

Чтобы в промежутке времени от момента блокировки элементов 2 до момента замыкания клавиши блока 1 триггеры 3 не были обнулены, в схему устройства введены элементы 11 и 12. На выходе элемента 11 именно в течение этого промежутка времени сохраняется сигнал логического «0», блокируя тем самым для прохождения сигнала обнуления элемент 12 на установочную шину 4 триггеров 3. Как только замыкается клавиша блока 1, т. е. на информационном входе элемента 2 появляется сигнал логи15 ческого «О», хотя состояние соответствующего триггера 3 и остается равным логической «1», на выходе элемента 11 формируется сигнал логической «1», который снимает блокировку элемента 12 на прохождение сигнала обнуления на упомянутый триггер 3.

Сигнал обнуления, соответствующий сигналу логической «1», проходит элемент 12 и шину 4 и опрокидывает тот триггер 3, который находится в единичном состоянии, в нулевое состояние. На этом цикл записи ложного символа информации устройством завершается.

Все последующие циклы записи информации, при которых последовательно используются и другие клавиши блока 1, проходят аналогично описанному.

На фиг. 2 представлены эпюры напряжения в основных точках схемы фиг. 1.

При этом предполагается, что логической «1» соответствует высокий уровень напряжения, а логическому «О» — низкий. Анализ соответствующих эпюр показывает, что прохождение сигнала на обнуление триггеров 3 невозможно до тех пор, пока не будут разомкнуты клавиши 1.

1171847

Редактор С. Патрушева

Заказ 487 I /44 а б

6 г

t ,Ф

f

1

1 t

Составитель В. Гордонова

Техред И. Верес Корректор Е. Рошко

Тираж 584 Подп ис ное

ВНИИПИ Государственного комитета СССР по делам изобретений и о1крытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4