Запоминающее устройство

Иллюстрации

Показать всеРеферат

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО , содержащее элементы памяти, один вывод каждого из которых соединен со словарной шиной, а другой - с опорной, генератор тока хранения и блок разряда, первые выводы которых соединены с онорной шиной, а вторые - с шиной нулевого потенциала, формирователь строки, содержащий п-р-п-транзистор, коллектор которого соединен с шиной питания, эмиттер - со словарной шиной, а база является адресным входом устройства, и резистор, один вывод которого соединен с базой, а другой - с коллектором п-р-п-транзистора, отличающееся тем, что, с целью повышения быстродействия устройства, в него введен блок шпунтирования, состоящий из двух п-р-п-транзисторов, причем коллектор первого п-р-п-транзистора подключен к шине питания , а эмиттер - к опорной шине и эмиттерам второго п-р-п-транзистора, база первого и коллектор и база второго п-р-п-транзисторов блока шунтирования подключены к дополнительному эмиттеру п-р-п-транзистора формирователя строки.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (Si}4 U 11 С 8 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3673761/24-24 (22) 19.12.83 (46) 07.08.85. Бюл. № 29 (72) М. О. Ботвиник, Ю. Н. Еремин и М. П. Сахаров (53) 681.327.66 (088.8) (56) Алексеенко А. Г., Шагурин И. И. Микросхемотехника.М.: Радиосвязь, 1982, с. 261.

Интегральная микросхема 185РУ4. Технические условия, 6КО.348.327. (54) (57) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее элементы памяти, один вывод каждого из которых соединен со словарной шиной, а другой — с опорной, генератор тока хранения и блок разряда, первые выводы которых соединены с опорной шиной, а вторые — с шиной нулево„„su„„» 71849 го потенциала, формирователь строки, содержащий п-р-п-транзистор, коллектор которого соединен с шиной питания, эмиттер со словарной шиной, а база является адресным входом устройства, и резистор, один вывод которого соединен с базой, а другой — с коллектором п-р-п-транзистора, отличаюи1ееся тем, что, с целью повышения быстродействия устройства, в него введен блок шунтирования, состоящий из двух п-р-п-транзисторов, причем коллектор первого и-р-п-транзистора подключен к шине питания, а эмиттер — к опорной шине и эмиттерам второго п-р-п-транзистора, база первого и коллектор и база второго и-р-и-транзисторов блока шунтирования подключены к дополнительному эмиттеру и-р-п-транзистора формирователя строки.

117!849

Изобретение относится к вычислительной технике и может найти применение при построении микросхем памяти большой информационной емкости.

Целью изобретения является повышение быстродействия устройства.

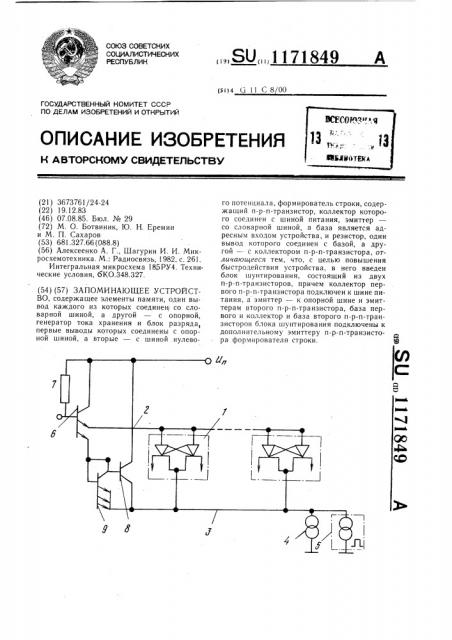

На чертеже представлена принципиальная схема предложенного запоминающего уст р ой ств а.

Запоминающее устройство содержит элементы 1 памяти, один вывод каждого из которых соединен со словарной 2 шиной, а другой — с опорной 3, генератор 4 тока хранения и блок 5 разряда, первые выводы которых соединены с опорной шиной 3, а вторые — с шиной нулевого потенциала. Формирователь строки содержит п-р-и-транзистор 6, коллектор которого соединен с шиной питания, эмиттер — со словарной шиной 2, а база является адресным входом устройства, и резистор 7, один вывод которого соединен с базой, а другой — с коллектором п-р-и-транзистора 6.

Устройство содержит блок шунтирования, который состоит из двух и-р-и-транзисторов

8 и 9, причем коллектор первого и-р-и-транзистора 8 подключен к шине питания, а эмиттер — к опорной шине 3 и эмиттерам второго и-р-п-транзистора 9, база транзистора 8 и коллектор и база транзистора 9 блока шунтирования подключены к дополнительному эмиттеру п-р-и-транзистора 6 формирователя строки.

Запоминающее устройство работает следующим образом.

Уровень напряжения на адресном входе схемы определяется наличием или отсутствием тока в резисторе 7. Если на адресный вход схемы в режиме невыбранной строки подан низкий уровень напряжения, то блок 5 разряда выключен. При этом генератор 4 тока хранения рассчитан таким образом, что через него протекает суммарный ток хранения всех элементов памяти и нормированный ток по цепи: шина питания, коллектор-эмиттер второго п-р-итранзистора 8, опорная шина 3, генератор

4 тока хранения, шина нулевого потенциала. Нормирование этой составляющей тока осуществляется первым дополнительным транзистором 9 и в зависимости от числа эмиттеров транзистора 9 статический коэффициент передачи этой цепи равен 1 (один эмиттер), J2- (два эмиттера), ..., h (и-эмиттеров) .

Таким образом, проигрыш в мощности потребления может быть программируемым.

В режиме выбранной строки на адрес. ный вход схемы подан высокий уровень напряжения. Генератор 4 тока хранения и блок 5 разряда включены. Если дополнительный коэффициент передачи тока схемы, образованной первым и-р-и-транзистором 8 и вторым .транзистором 9, значительно выше статического (при одинаковой конструкции этих транзисторов он равен + ), то начальный ток опорной шины 3 значйтелен, что позволяет разгрузить элементы 1 памяти

30 от протекания большого тока до начала операции записи и тем самым повысить быстродействие устройства.

Редактор С. Патрушева

Заказ 4871/44

Составитель А. Дерюгин

Техред И. Верес Корректор М. Са мборская

Тираж 584 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4