Элемент памяти

Иллюстрации

Показать всеРеферат

ЭЛЕМЕНТ ПАМЯТИ, содержащий тиристор, анод которого является первым управляющим входом элемента памяти, катод тиристора является вторым управляющим входом элемента памяти, транзистор и диод, анод которого соединен с эмиттером транзистора и является третьим управляющим входом элемента памяти, катод диода соединен с коллектором транзистора и с одной из баз тиристора, отличающийся тем, что, с целью повыщения помехоустойчивости элемента памяти, база транзистора соединена с другой базой тиристора. (Л 00 сд

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я0„„1171850

{5!)4 G 11 С 11/40,)3

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2I) 3742056/24-24 (22) 23.05.84 (46) 07.08.85. Бюл. № 29 (72) С. А. Королев (53) 681.327.6 (088.8) (56) Патент Японии № 56-22080, кл. G 11 С 11/40, 1981.

Авторское свидетельство СССР № 888207, кл. G Il С 11/40, 1977. (54) (57) ЭЛЕМЕНТ ПАМЯТИ, содержащий тиристор, анод которого является первым управляющим входом элемента памяти, катод тиристора является вторым управляющим входом элемента памяти, транзистор и диод, анод которого соединен с эмиттером транзистора и является третьим управляющим входом элемента памяти, катод диода соединен с коллектором транзистора и с одной из баз тиристора, отличающийся тем, что, с целью повышения помехоустойчивости элемента памяти, база транзистора соединена с другой базой тиристора.

1171850

Составитель Г. Бородин

Редактор С. Патрушева Техред И. Верес Корректор С. Черни

3а к аз 4871/44 Тираж 584 Подписное

ВНИИ ПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4

Изобретение относится к вычислительной технике, а именно к ячейкам памяти, и может быть использовано при создании интегральных оперативных запоминающих устройств большой емкости.

Цель изобретения — повышение помехоустойчивости ячейки памяти.

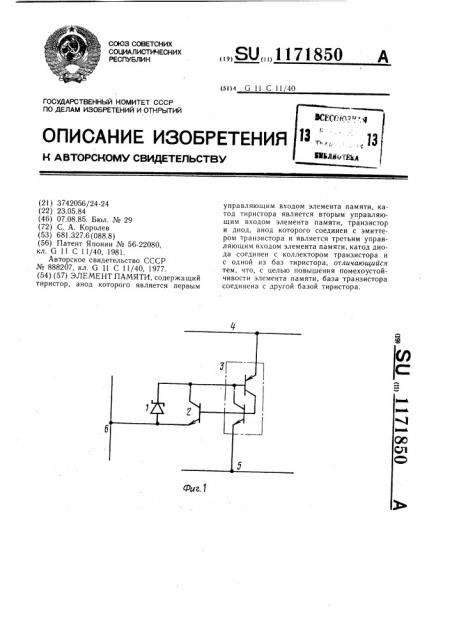

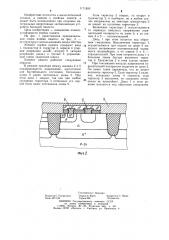

На фиг. 1 представлена принципиальная схема ячейки памяти; на фиг. 2 ее структура с использованием диода Шоттки.

Элемент ячейки памяти содержит диод

1, транзистор 2, тиристор 3, первую 4 (первая разрядная шина),: вторую 5 (вторая разрядная шина) и третью 6 управляющие шины (адресная шина).

Элемент памяти работает следующим образом.

В режиме хранения между шинами 4 и 5 поддерживается напряжение, достаточное для бистабильного состояния. Потенциал шины 6 равен потенциалу шины 5. При этом диод 1 закрыт, так как при любом состоянии тиристора 3 потенциал его первой базы выше потенциала шины 5.

Если тиристор 3 открыт, то открыт и транзистор 2, и наоборот, но в любом случае напряжение на эмиттере транзистора 2 не влияет на состояние тиристора 3.

Включение тиристора 3 осуществляется от перепада импульса напряжения отрицательной полярности по шине 6, а по шинам 4 и 5 — положительной.

Диод 1 при этом остается под обратным смещением. Выключение тиристора 3

1р осуществляется при подаче по шине 2 импульса напряжения положительной полярности полувыборки, а по шинам 5 и 6— отрицательной. При этом откроется диод 1 и большим током быстро выключит тиристор 3. Транзистор 2 в этом случае заперт.

15 При считывании импульс напряжения отрицательной полярности подается по шине 5.

Он имеет такие параметры, что не может включить тиристор 3. Если тиристор 3 включен, потенциал шины 4 снизится, если тиристор 3 выключен, то снижения потен2О циала не произойдет. Диод 1 в этом режиме находится под обратным смещением.