Сумматор-умножитель

Иллюстрации

Показать всеРеферат

СУММАТОР-УМНОЖИТЕЛЬ, содержащий два коммутатора, сумматор рабочего диапазона, умножитель рабочего диапазона, причем первые информационньй и управляющий входы первого коммутатора соединены соответственно с входом второго операнда и входом сложения сумматора-умножителя , выход первого коммутатора соединен с первым входом сумматора рабочего диапазона, выходы умножителя рабочего диапазона и сумматора рабочего диапазона соединены соответственно с первым и вторым информационными входами второго коммутатора , первый управляющий вход и выход которого являются соответственно входом умножения и выходом младшего разряда результата сумматора-умножителя , о тличающийся тем, что, с целью расширения области применения за счет формирования сигнала переполнения при сложении и старшего разряда результата при умножении, он содержит четыре дешифратора , три шифратора дополнительного диапазона, умножитель дополнительного диапазона, вычитатель дополнительного диапазона, два шифратора рабочего диапазона, четыре элемента ИЛИ и два элемента ИСКЛКЬ ЧАЮЩЕЕ ИЛИ, причем вход первого операнда сумматора-умножителя соединен с вторым входом сумматора рабочего диапазона, первым входом умножителя рабочего диапазона и входом первого дешифратора, выходы которого соединены с соответствующими входами первого шифратора дополнительного диапазона, выход которого соединен с первым входом умножителя дополнительного диапазона, второй вход которого соединен с выхоi дом второго шифратора дополнительного диапазона, вход второго операн (Л да сумматора-умножителя соединен с вторым входом умножителя рабочего диапазона и входом второго дешифратора , выходы которого соединены с соответствующими входами второго шифратора дополнительного диапазона и первого шифратора рабочего диапа зона, выход которого соединен с со вторым информационным входом перво4 го коммутатора, второй управляющий О вход которого соединен с первым вхосо дом первого элемента ИЛИ и с входом вычитания сумматора-умножителя, вход сложения которого соединен с вторым входом первого элемента Ш1И, выход последнего соединен с вторым управляющим входом второго коммутатора , вькодом соединенного с входом третьего дешифратора, выходы которого соединены с соответствующими входами третьего шифратора дополнительного диапазона, выход которого и выход умножителя дополнительного диапазона соединены соответственно

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5l)4 G 06 F 7/49

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3613434/24-24 (22) 29.06 ° 83 (46) 15.08.85. Бюл. 9 30 (72) В.Г. Евстигнеев, А.Н. Кошарновский, А.С. Новожилов и А.В. Маркин (53) 681.3 (088.8) (56) Авторское свидетельство СССР

9 352275, кл. G 06 F 7/72, 1972.

Авторское свидетельство СССР

9 256368, кл. G 06 F 7/49, 1976. (54) (57) СУММАТОР-УИНОЖИТЕЛЬ, содержащий два коммутатора, сумматор рабочего диапазона, умножитель рабочего диапазона, причем первые информационный и управляющий входы первого коммутатора соединены соответственно с входом второго операнда и входом сложения сумматора-умножителя, выход первого коммутатора соединен с первым входом сумматора рабочего диапазона, выходы умножителя рабочего диапазона и сумматора рабочего диапазона соединены соответственно с первым и вторым информационными входами второго коммутатора, первый управляющий вход и выход которого являются соответственно входом умножения и выходом младшего разряда результата сумматора-умножителя, отличающийся тем, что, с целью расширения области применения за счет формирования сигнала переполнения при сложении и старшего разряда результата при умножении, он содержит четыре дешифратора, три шифратора дополнительного диапазона, умножитель дополнительного диапазона, вычитатель дополнительного диапазона, два шифра„„SU„„1173409 тора рабочего диапазона, четыре элемента ИЛИ и два элемента ИСКЛ10"

ЧАЮЩЕЕ ИЛИ, причем вход первого операнда сумматора-умножителя соединен с вторым входом сумматора рабочего диапазона, первым входом умножителя рабочего диапазона и входом первого дешифратора, выходы которого соединены с соответствующими входами первого шифратора дополнительного диапазона, выход которого соединен с первым входом умножителя дополнительного диапазона, второй вход которого соединен с выходом второго шифратора дополнительного диапазона, вход второго операнда сумматора-умножителя соединен с вторым входом умножителя рабочего диапазона и входом второго дешифратора, выходы которого соединены с соответствующими входами второго шифратора дополнительного диапазона и первого шифратора рабочего диапазона, выход которого соединен с вторым информационным входом первого коммутатора, второй управляющий вход которого соединен с первым входом первого элемента ИЛИ и с входом вычитания сумматора-умножителя, вход сложения которого соединен с вторым входом первого элемента ИЛИ, выход последнего соединен с вторым управляющим входом второго коммутатора, выходом соединенного с входом третьего дешифратора, выходы которого соединены с соответствующими входами третьего шифратора дополнительного диапазона, выход которого и выход умножителя дополнительного диапазона соединены соответственно

1173409

АЬ=о с1, +4 q, 4+6= Vq + о,q,, с входами вычитаемого и уменьшаемого вычитателя дополнительного диапазона выход которого. соединен через четвертый дешифратор с входом второго шифратора рабочего диапазона, выход которого является выходом старшего разряда результата сумматора-умножителя, нечетные выходы первого и второго дешифраторов соединены соответственно с входами второго и третьего элементов ИЛИ, выходы которых сое1

Изобретение относится к вычислительной технике и может быть использовано в качестве одного из q-ичных разрядов многоразрядного арифметического устройства быстродействую- э щих вычислительных машин.

Цель изобретения — расширение области применения за счет формирования сигнала переполнения при сложении и старшего разряда результата при умножении.

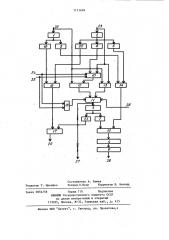

На чертеже представлена схема предлагаемого сумматора-умножителя.

Сумматор-умножитель содержит дешифраторы 1,2,3 и 4, шифраторы IS

5,6 и 7 дополнительного диапазона, шифраторы 8 и 9 рабочего диапазона, коммутаторы 10 и 11, сумматор 12 рабочего диапазона, умножитель 13 рабочего диапазона, умножитель 14 20 дополнительного диапазона, вычитатель 15 дополнительного диапазона, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 16 и 17, элементы ИЛИ 18, 19, 20 и 21, входы 22 и 23,первого и второго операн- 25 дов, входы 24, 25 и 26 слежения, вычитания и умножения, выходы 27, 28 и 29 младшего разряда, старшего разряда результата и переполнения соответственно. 30 В основу работы сумматора-умножителя положено следующее.

Пусть исходные числа А и В представлены по основаниям рабочего и диапазона СОК q = P Р;,Kpoмe того, 1 1„ пусть среди оснований рабочего диапазона нет четных оснований.

Произведение максимальных чисел из данного диапазона требует квадрадинены соответственно с первым и вторым входами первого элемента ИСКЛЮЧйОЩЕЕ ИЛИ, выход которого и выход четвертого элемента ИЛИ соединены соответственно с первым и вторым входами второго элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, выход которого является выходом переполнения сумматора-умножителя, нечетные выходы третьего дешифратора соединены соответственно с входами четвертого элемента HJIH.

2 тичного диапазона для представления.

Введем основания дополнительного диапазона СОК такие, что

@-П p ) g1.

1= ni

Расширенный диапазон q-Q достаточен для представления произведения.

Запишем произведение чисел А и В в виде где о „ и о 0 — старший и младший разряды произведения соответственно.

Остатки произведения по основаниям рабочего диапазона представляют младшую q-ую цифру а(0.

Старшая q-ая цифра произведения получается следующим образом:

Ы„=((АВ }, -((ЯВ) ) „)

Сумма чисел иэ данного диапазона требует для своего представления двойного диапазона, ее можно записать в виде

Ф где с — значение суммы по модулю qj

V = (1 ;1 — сигнал переноса в старший q-ый разряд, Ч=((А+В) -((А+ Ь) )2 )а

Дешифраторы 1,2,3 и 4 преобразуют числа из кода СОК в унитарный код.

Шифраторы 5, 6 и 7 преобразуют унитарный код в код СОК по основаниям дополнительного диапазона.

3 1

Шифратор 8 преобразует унитарный код в код дополнения числа до 2 по основаниям рабочего диапазона.

Шифратор 9 преобразует унитарный код в код СОК по основаниям рабочего диапазона.

Сумматор 12 и вычитатель 15 представляют соответственно совокупность независимых сумматоров и вычитателей по основаниям СОК.

Умножители 13 и 14 представляют совокупность независимых умножителей по основаниям СОК.

Сумматор-умножитель работает следующим образом.

Сложение ° Числа А и В по выходам 22 и 23 поступают на входы первого 1 и второго 2 дешифраторов.

Одновременно по входу 24 поступает управляющий сигнал сложения, который открывает по первому управляющему входу коммутатор 10 и через элемент ИЛИ 18 по второму управляющему входу — коммутатор 11. Кроме того, числа А и В поступают на второй вход-сумматора 12 и на первый информационный вход коммутатора соответственно. Коды первого и второго слагаемых, преобразованные на элементах ИЛИ 19 и 20, по модулю два поступают на элемент ИСКЛЮЧА10ЩЕЕ ИЛИ 16. С выхода коммутатора 10 второе слагаемое поступает на сумматор 12, где происходит сложение.

С выхода сумматора 12 результат о р через открытый по второму входу коммутатор 11 поступает на выход

27 сумматора-умножителя. Код результата, преобразованный на элементе ИЛИ

173409 4

21, по модулю два поступает на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

17, на первый вход которого поступает значение с выхода элемента

ИСКЛЮЧАЮЩЕЕ ИПИ 16. С выхода эле-мента ИСКЛЮЧАЮЩЕЕ ИЛИ 17 сигнал V поступает на выход 29 сумматора-умножителя.

Вычитание. Данная операция вы10 полняется аналогично операции сложения. Отличие состоит в том, что через коммутатор 10 поступает с шифратора 8 дополнение кода второго числа.

15 Умножение. Числа А и Б с входов

22 и 23 поступают на дешифраторы

1 и 2. По входу 26 подается сигнал умножения. Первый и второй операнды поступают также на входы умножите-

ZO ля 13. Преобразованные по основаниям дополнительного диапазона на шифраторах 5 и 6 первый и второй операнд поступают на входы умножителя 14. С выхода умножителя 13

25 через коммутатор 11 младший разряд произведения с поступает на выход 27 сумматора-умножителя. Одновременно с с помощью дешифратора

3 и шифратора 7 преобразуется в код по основаниям дополнительного диапазона и вычитается на вычитателе

15 из результата умножителя 14. На выходе вычитателя 15 образуется старшая цифра а произведения по основаниям дополнительного диапазона. Далее она преобразуется посредством дешифратора 4 и шифратора 9 в код по основаниям рабочим диапазона и поступает на выход 28 сумматора-умножителя.

1173409

Составитель А. Клюев.

Техред О.Неце Корректор Л. Бескид

Редактор Т. Иитейко

Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5054/48

Филиал ППП "Патент, г. Ужгород, ул. Проектная,4