Программное устройство управления

Иллюстрации

Показать всеРеферат

ПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее генератор импульсов , счетчик, первый и второй дешифраторы, блок памяти, первую и вторую группы коммутаторов, триг-. гер, элемент И, элемент задержки, регистр адреса и выходной регистр, причем вход управления режимом устройства подключен к управляющим входам коммутаторов первой и второй групп и входу записи-чтения блока памяти, адресные входы которого соединены с выходами первого дешифратора , входы которого соединены с выходами регистра адреса, первая и вторая группы информационных входов которого соединены соответственно с выходами коммутаторов первой и второй групп, вход записи регистра адреса соединен с первым выходом второго дешифратора, второй и третий выходы которого соединены соответственно с входом установки в единицу триггера и входом записи выходного регистра, установочный вход которого соединен с первым входом установки в ноль триггера, с установочным .входом счетчика и подключен к входу начальной установки устройства, четвертый выход второго дешифратора соединен с вторым входом установки в ноль триггера, входом элемента задержки и является выходом признака конца работы устройства, выход элемента задержки соединен с входом сброса счетчика, счетньш вход которого соединен с выходом элемента И, первый вход которого является входом признака начала работы устройства, второй вход элемента И соединен с выходом генератора импульсов, информационные выходы счетчика соединены с входами второго дешифратора, выход триггера соединен с входом разрешения обращения блока i памяти, информационные входы которого являются информационными входами уст (Л ройства, выходы блока памяти соединены с информационными входами выходного регистра, первая группа выходов которого является первой группой информационных выходов устройства, первые информационные входы коммутаторов второй группы подключены к второй группе вьпсодов выходного регистра, 00 4 первые информационные входы коммутаторов первой группы подключены к перйой группе входов условий устройства , вторые информационные входы коммутаторов второй группы подключены к второй группе входов условий устройства, отличающееся тем, что, с целью сокращения оборудования за счет уменьшения объема , оно содйржит группу мультиплексоров и группу дешифраторов, причем выходы мультиплексоров группы соединены с вторыми информационными входами ответствующих коммутаторов первой группы , управляющие входы мультиплексоров группы подключены к второй группе

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ .Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3629909/24-24 (22) 03.08.83 (46) 15.08.85. Бюл. № 30 (72) Д.И.Павлов (53) 681.325(088.8) (56) Авторское свидетельство СССР № 1003085, кл. С 06 F 9/22, 1981.

Авторское свидетельство СССР № 940163, кл. G 06 F 11/26, 1981. (54)(57) ПРОГРАММНОЕ УСТРОЙСТВО

УПРАВЛЕНИЯ, содержащее генератор импульсов, счетчик, первый и второй дешифраторы, блок памяти, первую и вторую группы коммутаторов, триг-:гер, элемент И, элемент задержки, регистр адреса и выходной регистр, причем вход управления режимом устройства подключен к управляющим входам коммутаторов первой и второй групп и входу записи-чтения блока памяти, адресные входы которого соединены с выходами первого дешифратора, входы которого соединены с выходами регистра адреса, первая и вторая группы информационных входов которого соединены соответственно с выходами коммутаторов первой и второй групп, вход записи регистра адреса соединен с первым выходом второго дешифратора, второй и третий выходы которого соединены соответственно с входом установки в единицу .триггера и входом записи выходного регистра, установочный вход которого соединен с первым входом установки в ноль триггера, с установочным ,входом счетчика и подключен к входу начальной установки устройства, четвертый выход второго дешифратора сое„„SU„„1173414 А (5 )4 G 06 F 9/00 G 06 F 9/22 динен с вторым входом установки в ноль триггера, входом элемента задержки и является выходом признака конца работы устройства, выход элемента задержки соединен с входом сброса счетчика, счетный вход которого соединен с выходом элемента И, первый вход которого является входом признака начала работы устройства, второй вход элемента И соединен с выходом венератора импульсов, информационные выходы счетчика соединены с входами второго дешифратора, выход триггера соединен с входом разрешения обращения блока памяти, информационные входы которого являются информационными входами устройства, выходы блока памяти соединены с информационными входами выходного регистра, первая группа выходов которого является первой группой информационных. выходов устройства, первые информационные входы коммутаторов второй группы подключены к второй группе выходов выходного регистра, первые информационные входы коммутаторов первой группы подключены к первой группе входов условий устрой.ства, вторые информационные входы коммутаторов второй группы подключены к второй группе входов условий устройства, о т л и ч а ю щ е е с я тем, что, с целью сокращения оборудования sa счет уменьшения объема памяти, оно содрржит группу мультиплексоров и группу дешифраторов, причем выходы мультиплексоров группы соединены с вторымиинформационными входами соответствующих коммутаторов первой группы, управляющие входы мультиплексоров группы подключены к второй группе

1173414 выходов выходного регистра, информа- выходов выходного регистра подклюционные входы мультиплексоров груп- чена через группу дешифраторов к пы подключены к третьей группе вхо- второй группе информационных выходов дов условий устройства, третья группа устройства.

Изобретение относится к вычислительной технике и может быть использовано для построения управляющих автоматов и автоматов обработки дискретной информации. 5

Цель изобретения — сокращение оборудования за счет уменьшения объема памяти.

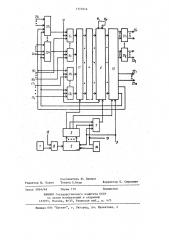

На чертеже представлена функциональная схема предлагаемого устрой- 10 ства.

Программное устройство управления содержит генератор 1 импульсов, счетчик ?, второй дешифратор 3, первый дешифратор 4, блок 5 памяти, первую гпуппу коммутаторов 61-6 триггер 7,,элемент И 8, вход 9 сброса, гфуппу информационных вхо-. дов 10„ -10м, регистр 11 адреса, выходной регистр 12, вторую группу 20 коммутаторов 13„ -13, элемент 14 задержки, вход 15 признака начала работы, первую группу входов 161 -16 условий, вторую группу входов 17„—

17 условий, вход 18 управления режимом, выход 19 признака конца работы, группу мультиплексоров

20„ — 70<, группу дешифраторов 21

21, первую группу информационных выходов 22„-22„ вторую группу инфор-30 мационных выходов 231-23О и третью группу входов 24„ -24,„ условий.

Устройство .работает следующим образом.

Коммутаторы 6 и 13 в зависимости от значения сигнала на входе 18 устройства коммутируют тот или иной вход, а блок памяти в зависимости от значения этого сигнала работает в режиме записи информации или считы- 40 вания.

Перед началом работы устройства в блок 5 памяти необходимо записать информацию об алгоритме работы уст|ройства управления. Для этого сигнал 45

"0" с входа 15 устройства запрещает

2 прохождение импульсов от генератора 1 через элемент. И 8 на счетчик 2, а сигнал с входа 9 приводит триггер 7, счетчик 2 и регистр 12 в исходное состояние, Затем на. входах 9 и 15 устройства устанавливаются сигналы

"1". При этом импульсы с генератора 1 через элемент И 8 поступают на вход счетчика 2, откуда в параллельном коде на дешифратор; 3 подается число отсчитанных импульсов, в результате на вход регистра 11 поступает импульс, по которому в него записывается адрес, заданный на входах 16„ -161 и 17 -17 устройства. Адре с дешифрируется дешифратором 4 и в блоке 5 памяти выбирается ячейка, в которую необходимо записать информацию с входных шин

10 -10 устройства. Счетчик 2 продол1 Я жает считать и дешифратор 3 устанавливает триггер 7 в единичное значение и разрешается запись в блок 5 памяти.

Затем дешифратор 3 устанавливает триггер 7 в исходное состояние, чем снимается сигнал обращения с блока 5 памяти, и сигнализирует по выходу 19 о необходимости выставить новую информацию для записи в новый адрес, через элемент 14 происходит сброс счетчика 2 в исходное состояние. Далее процесс многократно повторяется.

После записи информации подается сигнал "1" на вход 18 устройства, разрешающий считывание информации, а коммутаторы 6 и 13 коммутируют соответственно выходы мультиплексоров

20 и выходы регистра 12. Затем подается импульсный сигнал "0", приводящий счетчик 2, триггер 7 и регистр 12 в исходное состояние.

Процесс считывания информации из блока 5 памяти аналогичен процессу записи и управляется генератором 1, счетчиком .2, дешифратором 3 и триггером 7. При этом адреса считывания определяются совокупностью сигналов

3 11 на третьей группе выходов регистра 12 и соответствующих входах 24 устройства, входах, которые коммутируются в данном состоянии на вход коммутатора 6. Мультиплексоры 20 коммутируют .на вход коммутаторов 6 в каждом а; состоянии не более К входных сигналов из множества входных сигналов N, чем и достигается сокращение объема блока памяти по входным сигналам.

В выходных сигналах блока памяти, поступающих на входы дешифратора 21, закодированы выходные функции устрой;ства управления. Причем подгруппы .! выходных сигналов, поступающих на входы соответствующих дешифраторов, выбраны так, что внутри их каждый из сигналов принимает значение в моменты времени, не совпадающее с другими, его членами. Это группа выходов 23

73414 4 устройства. Выходные сигналы устройства управления, для которых кодирования провести невозможно, выведены непосредственно на выход устройства (группа 22).

В ряде случаев оказывается достае точным иметь мультиплексоры с числом коммутирующих входов, равным полови1О не и менее числа состояний памяти автомата. В этом случае часть входных переменных, коммутируемых мультиплексорами, не анализируется в а; состояниях или анализируется дважды в раз15 личных состояниях (например, в состоянии а1 — код 10011, состоянии а> код 00011), что необходимо учитывать при кодировании состояний автомата и программирования переключательных функций, записываемых в блок памяти.

1173414 як

f7<

Составитель Ю. Ланцов

Редактор Ю. Ковач Техред О.Неце Корректор Е. Сирохман

Заказ 5054/48 Тираж 710 Под пис но е

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4