Устройство для формирования векторов на экране электронно- лучевой трубки

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВЕКТОРОВ НА ЭКРАНЕ ЭЛЕКТРОННОЛУЧЕВОЙ ТРУБКИ, содержащее регистр, первый блок постоянной памяти, соединенный первым и вторым выходами соответственно с первыми входами первого и второго умножителей, соединенных вторыми входами между собой, а выходами - соответственно с первыми входами первого и второго сумматоров, первый и второй цифроаналоговые преобразователи, отличающееся тем, что, с целью расширения функциональных возможностей и повышения точности устройства, в него введены второй блок постоянной памяти, третий и четвертый умножители, первый и второй интеграторы, причем первый выход регистра соединен с входом первого блока постоянной памяти, входы - с входами устройства, второй выход через первый цифроаналоговый преобразователь - с вторым входом первого умножителя , третий выход через второй цифроаналоговый преобразователь - с первыми входами третьего и четвертого умножителей, четвертый выход - с входом второго блока постоянной памяти, соединенного первым и вторым выходами соответственно с вторыми с входами третьего и четвертого умножителей, ® выходы которых соединены соответственно (Л с вторыми входами первого и второго сумматоров , соединенных выходами через соответственно первый и второй интеграторы с соответствующими выходами устройства, с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1173436 (51) 4

ОПИСАНИЕ ИЗОБРЕ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3697688/24-21 (22) 09.02.84 (46) 15.08.85. Бюл. №; о (72) И. М. Урецкий и А. А. Денисов (53) 681.327.11(088.8) (56) Авторское свидетельство СССР № 830510, кл. G 09 G 1/08, 1981.

Авторское свидетельство СССР № 807362, кл. G 09 G 1/08, 1981 (прототип).

Бахтиаров Г. Д. Аналого-цифровые преобразователи. М. Советское радио, 1980, с, 51 — 54. (54) (57) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВЕКТОРОВ НА ЭКРАНЕ ЭЛЕКТРОННОЛУЧЕВОЙ ТРУБКИ, содержащее регистр, первый блок постоянной памяти, соединенный первым и вторым выходами соответственно с первыми входами первого и второго умножителей, соединенных вторыми входами между собой, а выходами соответственно с первыми входами первого и второго сумматоров, первый и второй цифроаналоговые преобразователи, отличающееся тем, что, с целью расширения функциональных возможностей и повышения точности устройства, в него введены второй блок постоянной памяти, третий и четвертый умножители, первый и второй интеграторы, причем первый выход регистра соединен с входом первого блока постоянной памяти, входы — с входами устройства, второй выход через первый цифроаналоговый преобразователь — с вторым входом первого умножителя, третий выход через второй цифроаналоговый преобразователь — с первыми входами третьего и четвертого умножителей, четвертый выход — с входом второго блока постоянной памяти, соединенного первым и вторым выходами соответственно с вторыми входами третьего и четвертого умножителей, выходы которых соединены соответственно с вторыми входами первого и второго сумматоров, соединенных выходами через соответственно первый и второй интеграторы с соответствующими выходами устройства.

1173436

Изобретение относится к автоматике и вычислительной технике, а именно к технике отображения информации, и может быть использовано для визуального представления графической информации на экране электроннолучевой трубки (ЭЛТ) в автоматизированных системах управления, в частности, для решения навигационных задач.

Цель изобретения — расширение функциональных возможностей и повышение точности устройства.

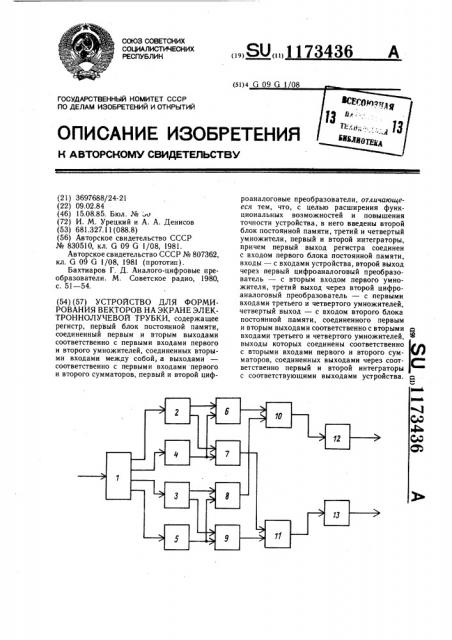

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит регистр 1, первый 2 и второй 3 блоки постоянной памяти, первый

4 и второй 5 цифроаналоговые преобразователи (ЦАП), первый 6, второй 7, третий 8 и четвертый 9 умножители, первый 10 и второй 1 сумматоры, первый 12 и второй 13 интеграторы.

Первый и второй выходы первого блока 2 постоянной памяти соединены соответственно с первыми входами первого 6 и второго 7 умножителей, соединенных вторыми входами между собой, а выходами — соответственно с первыми входами первого 10 и второго 11 сумматоров.

Первый выход регистра 1 соединен с входом первого блока 2 постоянной памяти, входы — с входами устройства, второй выход через первый ЦАП 4 — с вторым входом первого умножителя 6, третий выход через второй ЦАП 5 — с первыми входами третьего 8 и четвертого 9 умножителей, четвертый выход — с входом второго блока 3 постоянной памяти, соединенного первым и вторым выходами соответственно с вторыми входами третьего 8 и четвертого 9 умножителей, выходы которых соединены соответственно с вторыми входами первого 10 и второго 11 сумматоров, соединенных выходами через первый 12 и второй 13 интеграторы с соответствующими выходами устройства.

Регистр 1 предназначен для приема и хранения полярных координат векторов, подлежащих сложению.

Блоки 2 и 3 памяти предназначены для хранения кодов табличных функций синуса и косинуса угла и представляют собой постоянные запоминающие устройства (ПЗУ), содержимое каждой ячейки которых равняется синусу или косинусу адреса этой ячейки.

Такие блоки памяти могут быть выполнены на основе программируемых потребителем интегральных схем ПЗУ.

ЦАП 4 и 5 предназначены для преобразования кодов модуля вектора в пропорциональные напряжения.

Умножители 6 — 9 предназначены для цифроаналогового перемножения кодов синуса и косинуса аргумента вектора на напряжение, пропорциональное модулю вектора, и представляют собой четырехквадратные умножающие цифроаналоговые преобразователи. го l5

25 зо

Сумматоры 10 и 11 предназначены для алгебраического суммирования двух напряженийй.

Интеграторы 12 и 13 предназначены для интегрирования входных напряжений в течение времени формирования вектора и могут быть выполнены на базе операционного усилителя с конденсатором и аналоговым ключом в цепи обратной связи.

Устройство работает следующим образом.

В регистр 1 записывается код полярных координат двух векторов, подлежащих геометрическому сложению (вычитанию) на экране ЭЛТ.

Коды аргументов первого и второго векторов поступают соответственно на входы блоков 2 и 3 постоянной памяти, в результате чего на выходах блока 2 постоянной памяти формируются коды синуса и косинуса аргумента первого вектора, а на выходах блока 3 постоянной памяти — коды синуса и косинуса аргумента второго вектора.

Коды синуса и косинуса аргумента первого вектора поступают на цифровые входы умножителей 6 и 7, на аналоговые входы которых подается напряжение, пропорциональное модулю первого вектора, преобразованное из кода модуля с помощью преобразователя 4. В результате на выходе умножителей 6 и 7 формируются напряжения, пропорциональные проекциям первого вектора на координатные оси Х и Y.

Коды синуса и косинуса аргумента второго вектора поступают на цифровые входы умножителей 8 и 9, на аналоговые входы которых подается напряжение с выхода преобразователя 5, пропорциональное модулю второго вектора, причем если осуществляется сложение векторов, то полярность напряжения на выходе преобразователя 5 совпадает с полярностью напряжения на выходе преобразователя 4, если вычитание, то полярности противоположны. На выходах умножителей 8 и 9 формируются напряжения, пропорциональные проекциям второго вектора на оси Х и Y. Напряжения, пропорциональные проекциям векторов по оси Х, суммируются аналоговым сумматором 10, а напряжения, пропорциональные проекциям векторов по оси Y, — сумматором 11. Следовательно, на выходах сумматоров 10 и 11 действуют напряжения, пропорциональные проекциям суммарного вектора на оси Х и Y.

Эти напряжения интегрируются интеграторами 12 и 13 и подаются на отклоняющую систему ЭЛТ (не показана), обеспечивая отображение на экране ЭЛТ вектора, равного геометрической сумме (разности) двух входных векторов.

Таким образом, введение второго блока 3 постоянной памяти, умножителей 8 и 9, интеграторов 12 и 13 и их связей позволяет расширить функциональные возможности устройства и обеспечить возможность reo1173436

Составитель В. Дворкин

Редактор Ю. Ковач Техред И. Верес Корректор О. Тигор

Заказ 5069 49 Тираж 452 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, ж — 35, Раушская наб., д. 4/5

Филиал ППП сПатент>, г. Ужгород, ул. Проектная, 4 метрического сложения двух векторов, а отсутствие многократного преобразования число-импульсных кодов, позволяет повысить точность устройства.

Устройство может быть применено, в частности, в системах отображения совмещенной радиолокационной и графической информации, входящих в состав подвижных объектов, и позволяет отображать истинные и относительные векторы скоростей подвижных объектов для решения задач маневрирования и безопасного расхождения.