Оперативное запоминающее устройство на микросхемах памяти

Иллюстрации

Показать всеРеферат

1. ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МИКРОСХЕМАХ ПАМЯТИ, содержащее основной источник питания, шлход которого через разделительный элемент подключен к входам питания микросхем памяти и выходу резервно , то источника питания, формирователь сигналов неисправности питания и огJ рани 1ительный элемент, отличающееся тем, что, с целью повьшейия надежности устройства, в него в -введены триггер, группа элементов И и элемент И, выход которого подключен к входам выбора кристалла микросхем памяти, один из входов - к выходу триггера, входы которого соединены с выходами элементов И группы, прямой вход первого и первый инверсный вход второго элементов И группы t подключены к выходу формирователя сигналов неисправности питания и через ограничительный элемент соединены с выходом резервного источника пита-ния , причем инверсный вход первого и второй инверсный вход второго элементов И группы являются первым входом устройства, ВТорьм входом которого (. является второй вход элемента И, входы питания триггера и элементов И (Л . соединены с выходом резервного источника питания.I 2.Устройство по п. 1, отличающееся тем, что резервный источник питания выполнен в виде емкостного накопителя. 3,Устройство по п. 2, отличающееся тем, что первый и второй входы устройства объединены. оэ 4 4 СХ

СОЮЗ СОБЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (!9) (! ))

A (51) 4

ОПИСАНИЕ ИЗОБРЕТ

Я ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3612886/24-24 (22) 01.07.83 (46) 15.08.85. Stcam, И 30 (72) А.Е.Ашман, Е.M.Почекуева и Н.А.Сальников (53) 681.327.66(088.8) . (56) Полупроводниковые запоминающие устройства и их применение. Под ред.

А.Ю.Гордонова. М.: Радио и связь, 1981, с. 143.

У.Титце и Шенк Полупроводниковая схемотехника. М.: Мир, 1982, с. 395. (54)(57} 1 ° ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО НА МИКРОСХЕМАХ ПАМЯТИ, содержащее основной источник питания, выход которого через разделительный элемент подклочен к входам питания микросхем памяти и выходу резервно. го источника питания, формирователь сигналов неисправности питания и orpmv xeszxm% элемент, о т л и ч а ю-! щ е е с я тем, что, с целью повыше ния надежности устройства, в него в введены триггер, группа элементов И и элемент И, выход которого подключен к входам выбора кристалла микросхем памяти, один из входов — к выходу триггера, входы которого соединены с выходами элементов И группы, прямой вход первого и первый инверсный вход второго элементов И группы, подключены к выходу формирователя сигналов неисправности питания и через ограничительный элемент соединены с выходом резервного источника питания, причем инверсный вход первого и второй инверсный вход второго элементов И группы являются первым входом устройства, вторым. входом которого является второй вход элемента И, вхо« ды питания триггера и элементов И соединены с выходом резервного источника питания.

2. Устройство по п. 1, о т л и ч аю щ е е с я тем, что резервный источник питания выполнен в виде емкостного накопителя.

3. Устройство по п. 2, о т л и— ч а ю щ е е с я тем, что первый и второй входы устройства обьединены.

1173448

Изобретение относится к вычислительной технике, конкретнее к технике хранения информации н может быть использовано в вычислительных системах, где требуется обеспечение со- 3 хранности информации при кратковременных перерывах питания.

Цель изобретения — повышение надежности устройства путем обеспече.ния сохранности инфарл1аПии при кратковременных отключениях основного источника питания.

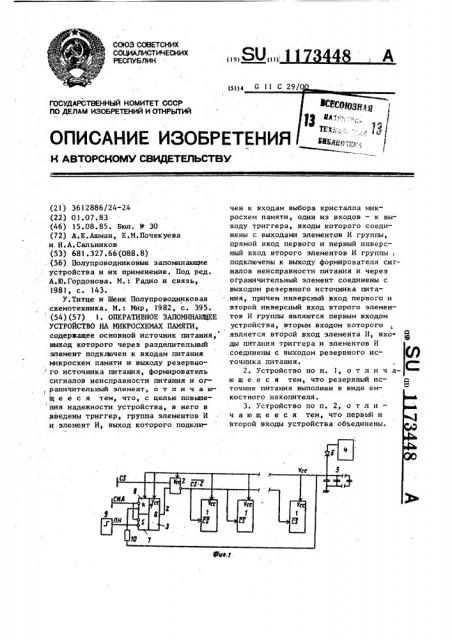

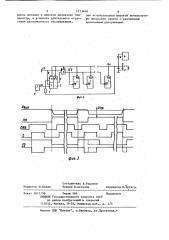

На фиг. 1 и 2 показаны примеры схемной реализации предлагаемого уст-1 ройства; на фиг. 3 — временные диаграммы его работы. устройство содержит (фиг,! и фиг.2) микросхемы 1 памяти, характеризуемые микромащным режимом хранения информации (например, КМОП ОЗУ ), элемент И 2, триггер 3, основной источник 4 питания и резервный источник 5 питания, выполненный например, в виде емкостного накопителя, разделительный элемент, например диод б, группу элементов И 7 и 8, формирователь 9 сигналов неисправности питания и ограничительный элемент, например резистор 10, Устройство работает следующим образом.

Если основной источник 4 питания исправен, то диод б открыт и все устройство питается от указанного истач->5 ника. Сигнал ПН "Питание неисправно" на выходе формирователя- 9 имеет низкий уровень ("О" ). До прихода активного синхроимпульса СИА на соот.— . ветствующем входе устройства также существует низкий уровень О" и триггер 3 установлен в состояние "1" при этом с его выхода сигнал Е (" Запрет" ) высокого уровня ("1" ) открывает элемент И 2, через который сигнал CS (" Выбор кристалла" ) проходит на соответствующие входы микросхем 1 (фиг.1 и 3 j.

При отключении источника 4 напряжение на его выходе Ueeix падает и диод б запирается, в этом случае питание микросхем 1 памяти, необходимое для обеспечения хранения занесенной в эти микросхемы информации, а также питание микромощных элемента И 2 и, Ы триггера 3, необходимых для блокировки обращения, осуществляется от накопителя 5.

Б момент достижения напряжением

Б,„ граничного значения Ut< формируется сигнал ПН в виде высокого уровня ("1" ). Значение граничного напряжения должно быть больше минимального догустимого напряжения питания, обеспечивающего хранение информации в микросхемах 1 памяти и нормальное функционирование элемента И 2 и триггера 3, Если сигнал ПН формируется в момент„ когда устройство свободно от обращения, то триггер 3 сигналами СИА = О и ПН = 1 переводится в состояние "0" и на выходе этого триггера формируется сигнал Z = 0, который закрывает элемент И 2 и не до1 пускает последующих обращений к микросхемам 1 памяти.

Аналогичным образом происходит процесс включения основного источника 4: при достижении напряжением

П6, значения U» в моменты между обращениями формируется сигнал ПН=.Q который вместе с сигналом СИА=О переводит триггер 3 в состояние "1 ; сиг= нал Z=i открывает элемент И 2 и подготавливает устройство к нормальной работе, Питание всего устройства при этом опять осуществляется от основного источника 4.

Если отключение источника 4 и формирование сигнала ПН.=1 происходит во время обращения, та прерывание цикла обращения недопустимо и необходимо задержать процесс формирования сигнала Z=0 до окончания цикла (СИА=О), так как в противном случае возможна потеря информации. Эта задержка осуществляется триггером 3, который уста. навливается в состояние "0 в момент, соответствующий концу синхроимпульса СИА, когда ПН=1 и СИА=.О. В результате на входах микросхем 1 памяти до конца обращения сохраняется нормальный режим работы микросхемы в соответствии с заданной временной диаграммой.

Аналогичным образом происходит процесс включения основного источника 4.

В устройстве (фиг.2), где отсутствуют активные синхроимпульсы, все процессы происходят аналогичным образом, только включение и выключение сигнала Е происходит не по фронтам синхроимпульса СИА, а по фронтам сигнала CS.

Предлагаемое устройство обеспечивает сохранность информации при пере-, фиг. 2 (pU8. 3

Составитель В. Рудаков

Техред И.Асталош

Корректор, В, Бутяга, Si.

Редактор Ю.Ковач

Заказ 5071/50 Тираж 584

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, -35 Раушская наб,, д. 4/5

Подписное

Филиал ППП "Патент", г.Ужгород, ул.Проектная,4 з 1173448 4 рывах питания в широком диапазоне тем- при использовании широкой номенклатуператур, в условиях длительного отсут- ры микросхем памяти с различными ствия регламентного обслуживания, временными диаграммами.