Умножитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ, содержащий формирователь импульсов, вход которого соединен с входной шиной, выход - с входом блока управления, первый выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с первым входом триггера, второй вход которого соединен с выходом первого счетчика импульсов , счетный вход которого соединен с выходом первого элемента И, первый вход которого соединен с первым выходом триггера, второй выход которого соединен с выходной шиной и с первым входом второго элемента И, выход которого соединен со счетным входом второго счетчика импульсов, второй вход первого элемента И соединен с выходом первого делителя частоты, вход которого соединен с шиной опорной частоты и с вторым входом второго элемента И, второй делитель частоты, выход которого соединен со счетным входом третьего счетчика импульсов, информационные выходы которого через первый регистр памяти соединены с информационными входами первого счетчика импульсов , отличающийся тем, что, с целью повышения точности умножения при изменении входной частоты, в него введен второй регистр памяти, информационные входы которого соединены с информационными выходами второго делителя частоты, счетный вход которого соединен с выходом первого $S делителя частоты, вход сброса - с вторым выходом блока управления и с входом сброса (Л третьего счетчика импульсов, вход записи первого регистра памяти соединен с входом записи второго регистра памяти и с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго счетчика импульсов , выход - с входами записи первого и второго счетчиков импульсов, а информационные входы второго счетчика импульсов соединены с информационными выходами второго регистра памяти. 00 гСЛ СО

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (з1)4 Н 03 К 5 156! ©со „;-,.

13 "::

rtх6.;,. 18

®ЮЯ®О ТЕ, ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМЪ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3696991/24-2! (22) 07.02.84 (46) 15.08.85. Бюл. № 30 (72) И. И. Корнилов, А. С. Овсянников и А. П. Фролов (71) Куйбышевский электротехнический институт связи (53) 621.374.4 (088.8) (56) Авторское свидетельство СССР № 1056372, кл. Н 03 К 5/156, 29.12.81.

Авторское свидетельство СССР № 760420, кл. Н 03 К 5/Ol, 24.07.78. (54) (57) УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ, содержащий формирователь импульсов, вход которого соединен с входной шиной, выход — с входом блока управления, первый выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с первым входом триггера, второй вход которого соединен с выходом первого счетчика импульсов, счетный вход которого соединен с выходом первого элемента И, первый вход которого соединен с первым выходом триггера, второй выход которого соединен с выходной шиной и с первым входом второго элемента И

У выход которого соединен со счетным входом

„„SU„„1173537 A второго счетчика импульсов, второй вход первого элемента И соединен с выходом первого делителя частоты, вход которого соединен с шиной опорной частоты и с вторым входом второго элемента И, второй делитель частоты, выход которого соединен со счетным входом третьего счетчика импульсов, информационные выходы которого через первый регистр памяти соединены с информационными входами первого счетчика импульсов, отличающийся тем, что, с целью повышения точности умножения при изменении входной частоты, в него введен второй регистр памяти, информационные входы которого соединены с информационными выходами второго делителя частоты, счетный вход которого соединен с выходом первого делителя частоты, вход сброса — с вторым выходом блока управления и с входом сброса третьего счетчика импульсов, вход записи первого регистра памяти соединен с входом записи второго регистра памяти и с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго счетчика импульсов, выход — с входами записи первого и второго счетчиков импульсов, а информационные входы второго счетчика импульсов соединены с информационными выходами второго регистра памяти.

ll

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и измерительной тгх-!!Ик!!.

1де.!ь изобретения — повышение точности умножения при изменении входной частоты за счет компенсации погрешности при изме!!енин входной частоты.

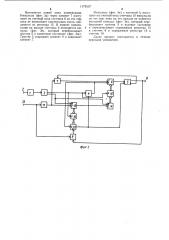

На фиг. 1 приведена электрическая структурная схема умножителя частоты следования импульсов; на фиг. 2 -- блок управления„ вар:!ант выполнения; на фиг. 3 — временные диаграммы, поясняющие работу устройства.

Умножитель частоты следования импульсов содержит формирователь 1 импульсов, вход которого соединен с входной шиной 2, выход — с входом блока 3 управления, i, еоный ":,» хо которого со,".ди!!ен с первым вхо.ил! элементы ИЛИ 4, второй вход которого Осдп;!сki с первым входом триггера 5, второ!! вход которого соединен с выходом первого счетчика 6 импульсов, счетный вход которого соединен с выходом первого элемента И 7, первый вход которого соединен п,ервым выхо,дом триггеры 5, второй выход которого соединен с выходной шиной 8 и с первым входом второго элемента И 9, выход которого соединен со счетным входом в.!Оро! О i". k Tiki!! 10 HMII) .ibCOB, kITOpOH BXOQ первого элемента И 7 соединен с выходом первого делителя 11 частоты, вход которого соеди!сн с шиной 12 опорной частоты и с вторым входом второго элемента И 9, второи дег!ятс !ь 13 частоты, выход которого соединс! со счетным входом третьего счетчик

Первый и второй счетчики импульсов выполнены вычитающими, третий — суMMHрующим.

73537

40

5 !

О 5

Устройство работает следующим образом.

Импульсы умножаемой частоты Р„через формирователь 1 импульсов поступают на блок 3 и в одновибраторах 17 и 18 формируются соответственно импульсы записи (фиг. Зб) информации в регистры 15 и 16 и через элемент 4 (фиг. Зг) — в счетчики 6 и 10 (фиг. Зв) делителя 13 и счетчика 14.

В исходном состоянии триггер 5 находится в состоянии «О» (фиг. Зж) и содержимое делителя 13 и счетчика 14 равно нулю.

В начале i-го периода умножаемой частоты выходным сигналом (фиг. Зб) блока 3 с первого выхода производится перезапись кодовой комбинации, накопленной в (i — 1) -м периоде, из счетчика 14 в регистр 15, а затем и в счетчик 6 импульсов сигналом (фиг. Зг), поступившим на второй его вход с первого выхода блока 3 через элемент 4. Этим же импульсом производится перезапись кодовой комбинации из делителя 13 в регистр 16 и в счетчик 10. В следующий момент времени импульсом (фиг. Зв) сброса с второго выхода блока 3 происходит сброс в «О» делителя 13 и счетчика 14, тем самым подготавливая их к заполнению по цепи опорной частоты.

В течение i-го периода умножаемой частоты опорная частота fo делится на М в делителе 11, импульсы с частотой fi=fo/М поступают на счетный вход делителя 13.

С его выхода импульсы уже с частотой 12=

=fi/М подаются на счетный вход счетчика 14

В счетчике 6 происходит компенсация записанного числа Ni, полученного импульсом с частотой fi/M за время Т„в (i — 1)-м периоде умножаемой частоты, импульсами (фиг. Зд) с частотой fi, поступающими на счетный вход счетчика 6 с выхода элемента 7, который открыт высоким потенциалом, поступающим с инверсного выхода триггера 5.

В конце цикла компенсации выходным сигналом (фиг. Зе) счетчика 6 перебрасывается триггер 5 (фиг. Зж), закрывающий элемент 7 и открывающий элемент 9, через который импульсы с частотой fo (фиг. Зи) поступают на счетный вход счетчика 10. В то же время через закрытый элемент 7 импульсы (фиг. Зд) с частотой fi на счетный вход счетчика 6 не поступают.

Таким образом, в счетчике 10 происходит компенсация записанного числа, после чего на его выходе появляется импульс (фиг. 3x), который перебрасывает триггер 5 в исходное состояние и формируется первый выходной импульс (фиг. Зж) с коррекцией. При этом низким потенциалом, поступающим с прямого выхода триггера 5, элемент 9 закрывается, а высоким потенциалом, поступающим с инверсного выхода триггера 5, элемент 7 открывается. Этим же выходным сигналом (фиг. Зк) счетчика 10 импульсов, прошедшим через элемент 4 (фиг. Зг), показания регистра 15 записываются в счетчик 6 и показания регистра 16 — в счетчик 10.

1173537

Начинается новый цикл компенсации.

Импульсы (фиг. Зд) через элемент 7 поступают на счетный вход счетчика 6 до тех пор, пока не произойдет компенсация числа, введенного из регистра 15. В момент компенсации на выходе счетчика 6 появляется импульс (фиг. 3e), который перебрасывает триггер 5 в единичное состояние (фиг. Зж).

Триггер 5 открывает элемент 9 и закрывает элемент 7.

Импульсы (фиг. Зи) с частотой fo поступают на счетный вход счетчика 10 импульсов до тех пор, пока на его выходе не появится выходной импульс (фиг. 3x), который перебрасывает триггер 5 в нулевое состояние и перезаписывает содержимое регистра 15 в счетчик 6 и содержимое регистра 16 в счетчик 10.

Далее процесс повторяется в течение периодов умножения.

1173537 (Pub. 3

Составитель А. Соколов

Редактор Н. Швыдкая Техред И. Верес Корректор В. Гирняк

Заказ 5077/54 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4