Устройство согласования

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО СОГЛАСОВАНИЯ, содержащее первый и второй транзисторы первого типа проводимости с инжекционным питанием, эмиттеры которых подключены к общей шине, база инжектора второго транзистора подключена к общей шине, коллектор первого транзистора подключен к выходу устройства и к коллектору третьего транзистора второго типа проводимости, эмиттер которого подключен к шине питания, отличающееся тем, что, с целью уменьшения потребляемой мощности, введены два диода Шоттки и резистор, база третьего транзистора через резистор подключена к коллектору второго транзистора и к катоду первого диода Шоттки, анод которого подключен к базе первого транзистора, база инжектора которого подключена к входу устройства и к катоду второго диода Шоттки, анод которого подключен базе второго транзистора . (Л оо сд ел ю

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5Ц4 Н 03 К 19 091

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМ,К СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3701422/24-.21 (22) 17.02.84 (46) 15.08.85. Бюл. № 30 (72) С. В. Касаткин, И. И. Лавров, В. И. Громов и П. В. Ястребов (53) 621.375 (088.8) (56) Заявка Великобритании № 2015840, кл. Н 03 К 19/08, 1979.

Авторское свидетельство СССР № 557438, кл. Н 01 1 29/70, 1976. (54) (57) УСТРОЙСТВО СОГЛАСОВАНИЯ, содержащее первый и второй транзисторы первого типа проводимости с инжекционным питанием, эмиттеры которых подключены к общей шине, база инжектора второго тран„„Я0„„1173552 а зистора подключена к общей шине, коллектор первого транзистора подключен к выходу устройства и к коллектору третьего транзистора второго типа проводимости, эмиттер которого подключен к шине питания, отличающееся тем, что, с целью уменьшения потребляемой мощности, введены два диода

Шоттки и резистор, база третьего транзистора через резистор подключена к коллектору второго транзистора и к катоду первого диода Шоттки, анод которого подключен к базе первого транзистора, база инжектора которого подключена к входу устройства и к катоду второго диода Шоттки, анод которого подключен < базе второго транзистора.

1173552

Составитель А. Янов

Техред И. Верес Корректор Л. Пилипенко

Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и о крытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Редактор Н. Швыдкая

Заказ 5078/55

Изобретение относится к импульсной технике и может быть использовано в цифровых интегральных схемах.

Цель изобретения — уменьшение потребляемой мощности.

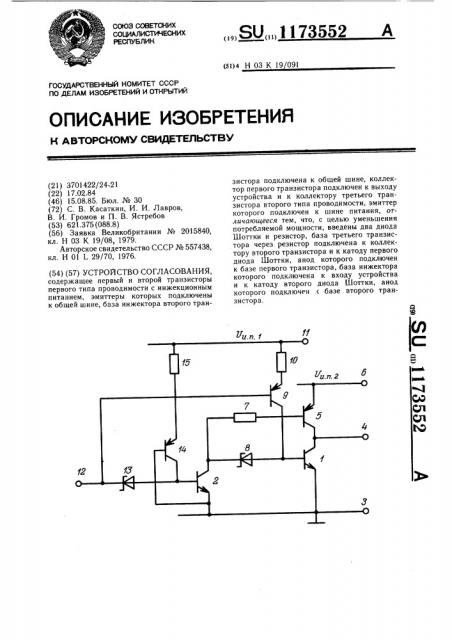

На чертеже приведена электрическая принципиальная схема устройства.

Устройство содержит первый 1 и второй 2 транзисторы первого типа проводимости, эмиттеры которых подключены к общей шине 3, коллектор транзистора 1 подключен к выходу 4 устройства и к коллектору третьего транзистора 5 второго типа проводимости, эмиттер которого подключен к шине 6 питания, а база через резистор 7 подключена к коллектору транзистора 2 и катоду первого диода Шоттки 8, анод которого подключен к базе транзистора 1 и коллектору транзистора 9 второго типа проводимости, который является инжектором транзистора 1, эмиттер которого через резистор 10 подключен к шине 11 питания, а база подключена к входу 12 устройства и катоду второго диода Шоттки 13, анод которого подключен к базе транзистора 2 и коллектору транзистора 14 второго типа проводимости, который является инжектором транзистора 2, база которого подключена к общей шине 3, 25 а эмиттер через резистор 15 подключен к шине 11 питания.

Устройство согласования работает следующим образом.

Если на входе 12 устройства присутствует сигнал логического «О» (управляющий этим входом транзистор насыщен), коллекторный ток транзистора 14, величина которого определяется в основном сопротивлением резистора 15, через прямо включенный диод Шоттки 13 ответвляется из базы транзистора 2 в коллектор управляющего входом 12 транзистор. Транзистор 2 заперт.

Поскольку база транзистора 9 закорочена на общую шину 3 через управляющий входом 12 транзистор предыдущего каскада, то транзистор 9 открыт и его коллекторный 40 ток, который определяется в основном значением сопротивления резистора 10, поступает в базу транзистора 1, вызывая его отпирание. Транзистор 1 находится в режиме насыщения, и на выходе устройства 4 присутствует сигнал логического «О» (=0,1 — 45

0,2В) .

При этом так как транзистор 2 закрыт, то ток базы транзистора 5 определяется коллекторным током утечки транзистора 2 и обратным током диода Шоттки 8, которыми имеют малую величину, что соответствует закрытому состоянию транзистора 5. В этом состоянии устройство потребляет ток, равный сумме эмиттерных токов транзисторов 14 и 9, При поступлении на вход 12 устройства сигнала логической «1» (управляющий этим входом транзистор предыдущего каскада закрыт) коллекторный ток транзистора 14 ответвляется в базу транзистора 2, который открывается и входит в режим насыщения.

Одновременно с этим происходит запирание транзистора 9 и транзистора 1. При этом запирание транзистора 1 осуществляется перехватом коллекторного тока транзистора 9 и активным рассасыванием базового заряда за счет протекания коллекторного тока транзистора 2. Так как транзистор 2 входит в режим насыщения, то база транзистора 5 через резистор 7 и транзистор 2 оказывается закороченной на общую шину 3

Транзистор 5 открывается и его коллекторный ток осуществляет форсированный перезаряд суммарной нагрузочной емкости на выходе 4 устройства до напряжения, равного

Ыа а — 1./ан 5, где Ua.аа — напряжение шины 6 питания, а 1/аа з — напряжение коллектор— эмиттер транзистора 5 в режиме насыщения.

На выходе 4 устройства устанавливается сигнал логической «1».

В этом состоянии устройство потребляет ток, равный сумме эмиттерного тока транзистора 14 и базового тока транзистора 5.

Транзистор 9 закрыт, так как его базовый ток определяется коллекторным током утечки управляющего входом 12 транзистора и обратным током диода Шоттки 13, величины которых малы.

Таким образом, снижение потребляемой мощности устройства достигается за счет отключения наибольшего в устройстве тока транзистора 9 и стабилизации базового тока транзистора 5 в состоянии логической «1» на выходе устройства 4. Кроме того, в предлагаемом устройстве одноколлекторные транзисторы 1 и 2 могут быть выполнены в нормальном включении, что также приводит к снижению потребляемой мощности устройства.