Непозиционный цифроаналоговый преобразователь

Иллюстрации

Показать всеРеферат

НЕПОЗИЦИОННЫЙ ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий блок набора эталонных напряжений, блок суммирования напряжений, отлит чающийся тем, что, с целью повышения быстродействия, в него введены г блоков ключей, где П- число оснований непозиционной системы счисления , п элементов ИЛИ, п аналоговых ключей, п блоков вычитания, мажоритарный блок, блок преобразования по модулю, при этом соответствующие п группвыходов блока набора эталонных напряжений подключены к соответствующим аналоговым входам соответствующих блоков ключей, выходы которых подключены к первым входам соответствующих блоков вычитания, выходы которых подключены к соответствующим входам блока суммирования напряжения, выход которого подключен к первому входу блока преобразования по модулю, выход которого подключен к выходной шине цифроаналогового преобразовате-. ля, шины преобразуемого кода подключены к управляющим входам соответствующих блоков ключей, соответствующие шины преобразуемого кода подключены ко входам соответствующих элес S ментов ИЛИ, выходы которых подключе ны к соответствующим входам мажоритарного блока, выходы которого подключены к управлянмцим входам соответствующих пар аналоговых ключей, выходы которых подключены ко вторым входам соответствующих блоков вычитания, а аналоговые входы объединены и подключены к (п+1)-му выходу блока набора эталонных напряжений, вход которого объединен со вторым входом блока преобразования по модулю и подключен к шине эталонного напряжения.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19((I I) (5))4 Н 03 М 1/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ и АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТЭЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3608386/24-24 (22) 07.04.83 (46) 15.08.85. Бюл. У 30 (72) Н.А.Вершков, С.Н.Хлевной, Н.И.Червяков и Н.И.Швецов (53) 681,325(088.8) (56) Абрамсон И.Т. и др. Принципы построения преобразователей информации в системе остаточных классов, Автометрия, 1969, В 2, с. 7.

Авторское свидетельство СССР к 282767, кл. Н 03 К 13/03, 1969. (54)(57) НЕПОЗИЦИОННЫЙ ЦИФРОАНАЛОГО- .

ВЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий блок набора эталонных напряжений, блок суммирования напряжений, о т л и — . ч а ю шийся тем, что, с целью повышения быстродействия, я него введены и блоков ключей, где П вЂ” число оснований непоэиционной системы счисления, и элементов ИЛИ, и аналоговых ключей, и блоков вычитания, мажоритарйый блок, блок преобразования по модулю, при этом соответствующие и групп выходов блока набора эталонных напряжений подключены к соответствующим аналоговым входам соответствующих блоков ключей, выходы которых подключены к первым входам соответствующих блоков вычитания, выходы которых подключены к соответствующим входам блока суммирования напряжения, выход которого подключен к первому входу блока преобразования по модулю, выход которого подключен к выходной шине цифроаналогового преобразовате-. ля, шины преобразуемого кода подключены к управляющим входам соответствующих блоков ключей, соответствующие шины преобразуемого кода подключены ко входам соответствующих элементов ИЛИ, выходы которых подключены к соответствующим входам мажоритарного блока, выходы которого подключены к управляющим входам соответствующих пар аналоговых ключей, выходы которых подключены ко вторым входам соответствующих блоков вычитания, а аналоговые входы объединены и подключены к (и+1)-му выходу блока набора эталонных напряжений, вход которого объединен со вторым входом блока преобразования по модулю и подключен к шине эталонного напряжения.

1 1173

Изобретение относится к вычисли тельной технике и может быть использовано для сопряжения вычислительных устройств, функционирующих в системе остаточных классов (СОК) с различными оконечными устройствами, требующими аналогового вывода, а также в технике связи в случае использования кодов СОК в цифровой телефонии, Целью изобретения является позы- 1п шение быстродействия.

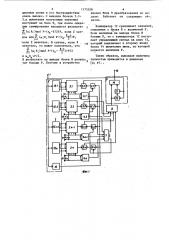

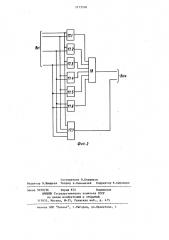

На .фиг. 1 приведена структурная схема устройства; на фиг. 2 — пример реализации мажоритарного блока для

СОК с числом оснований п=4.

Непозиционный цифроаналоговый преобразователь содержит шину 1 эталрнного напряжения, блок 2 набора эталонных напряжений, блоки 3.1-3.п ключей, элементы ИЛИ 4.1-4.п, блоки 5.1-5.п вычитания, аналоговые ключи 6,1-6.п, мажоритарный блок 7, блок 8 суммирования напряжений, блок 9 преобразования по модулю, выходную шину 10, шины 11 преобразуемого кода, при этом в состав блока 9 входят компаратор 12, ключ 13, блок 14 вычитания, а в состав блока 2резисторные делители 15,1-15.п и резисторный делитель 1 6 надва.В состав мажоритарного блока 7 для п=4 входят элементы И 17.1-17.7 и элемент ИЛИ 18.

Принцип работы устройства заключается в следующем. 35

Из теории чисел известно, что если число А представлено в СОК с основаниями Р, P,,..., Р,„, остатками, ..., с, то оно может быть найдено как 4О

А=(ф,З, +с< В2+ ° ° ° cc„l3 )mod Р

=(- ;В,)mod g, (1) где  — коэффициенты ортогонального базиса, удовлетворяющие условию

Р— диапазон однозначного представления чисел в конкретной СОК.

Выражение (1) можно переписать как и

А= м;В; -r ДР, 5Î где r - ранг числа .А.

Если две любые величины, В, и 1В превышают величину Р/2, то при суммировании М; В;+g В превысит значение P. Таким образом, целесооб- 55 разно вычислить все возможные значения к;В,, М; =0,1,..., P, -1, найти те остатки <;, при которых значения В превышают Р/2, и при их поступлении на вход преобразователя вычитаем значения P/2 попарно из каналов преобразования. Если же число m каналов, в которых к В >Р/2 нечетное, то

nl-I сумма (Qg В -kP)+a В может превы в- 1 m q сить значение P. Поэтому на выходе преобразователя необходимо поставить; устройство приведения в диапазон P..

Таким образом, вычитание величины В Р/2, где g- четное, позволяет частично скомпенсировать ранг числа А и, кроме того, более рационально использовать диапазон выходного сумматора, так как в сумматоре вместо величины

Ф О ,Х ;В, находится величина „В— (r„-0/г) Р/2

1=1

На входе резисторных делителей

15.1-15.п с шины подается эталонное напряжение величиной Р. Резисторные делители рассчитаны так, что с них снимаются напряжения, пропорциональные (g, B;)mod Р, где ю ; =О, 1,..., Р„,. На шины 11 преобразуемого кода подаются остатки ф;, представленные в единичном коде, т.е. возбужденной оказывается та из Р;., шин, номер которой равен величине остатка.

С приходом остатков открываются соответствующие ключи блоков 3.1-3.п ключей и величины (g,  )mod Р проходят на первые входы блоков 5.1-5.п вычитания. Некоторые входные шины 11, а именно те, которым соответствуют ;В; Р/2, подключены к входам элементов ИЛИ 4.1-4.п проходя через которые сигналы поступают на входы мажоритарного блока 7, который осуществляет выборки 2 из п, 4 из и 6 из и и. т.д. Пример реализации мажоритарного блока, осуществляющего выборки 2 из 4 и 4 из 4 приведен на фиг. 2. Если на входов мажоритарного блока 7 поступили сигналы, то с 2/2 выходов, если 5 четное, или с (0-1)/2 выходов, если t нечетное, подают сигналы на 1 (или 0-1) соответствующих аналоговых ключей 6.1-6.п на информационные входы которых поступает величина P/2 с резисторного делителя 16 на два. Причем процесс подачи на одни входы блоков 5.1-5,п вычитания величин (ы;В„)той Р и на другие входы — величины Р/2 происходит почти одновременно, так как мажоритарный блок 7 реализов н ко,биназ 1173558 4 ционным путем и его быстродействие введен блок 9 преобразования по мо» очень высоко. С выходов блоков 5.1- дулю. Работает он следующни об-.

5.п вычитания полученные значения разом. поступают на блок 8, где после операпии суммирования находится результат Компаратор 12 сравнивает значение, и снимаемое с блока 8 с величиной Р.

Если величина на выходе блока 8

Ное или Z («; B, ) mod P- (г,„- — -) Р, В больше Р, то с компаратора 12 поступает управляющий сигнал на ключ 13, ! если сли (нечетное. В случае, если 0 .:jp . который подключает к.второму входу . нечетное, то может полУчиться, что блока 14 вычитания шину по которой и .с (к В )mod P-(r — — -))Р/2

E-1 подается величина Р, ъ 4 2 и Фс„В )Р/2. п

Таким образом, выходная величина

В результате на выходе блока 8 резуль-, полностью приводится в диапазон тат больше Р. Поэтому в устройство (О;.Р).. t 173558 дх.

Составитель В.Першиков

Редактор Н.Швьщкая Техред А.Кикемезей Корректор E.ÑHðîõìàí

Заказ 5079/56 Тираж 872 Подпис ное

ВЯИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Филиал ПНП "Патент", г.ужгород, ул.Проектная, 4