Устройство многоуровневого прерывания

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО МНОГОУРОВНЕВОГО ПРЕРЫВАНИЯ,содержащее регистр запросов , блок выходных элементов И, триггер запрета прерывания, триггер прерывания , триггер .синхронизации, nor . стоянный запоминающий блок, причем информационные входы регистра запросов являются входами запросов устройства , а выход .регистра запросов соединен с входом постоянного запоминающего блока и информационным входом блока выходных элементов И, управляющий вход которого соединен с Rвходом триггера прерьюания и входом выдачи кода приоритетности устройства , а выход является выходом приоритетности устройства, вход Прерьшающая программа устройства соединен с синхронизирующим входом триггера запрета прерывания первым информационным входом входного коммутатора и первым входом запуска счетчика, выход котррого соединен с входом дешифратора, выход которого соединен с управляющими входами входного и выходного коммутаторов, выход выходного коммутатора соединен с первым входом схемы сравнения, второй вход которой соединен с выходом постоянного запоминающего блока, выход схемы сравнения соединен с первым входом первого элемента И, выход которого соединен с информа-, ционным входом триггера синхронизации , Быход которого соединен с 5 входом триггера прерывания, выход ;. которого является .выходом прерывания устройства и соединен с входом установки B.I триггера запрета прерывания , выход которого соединен с вторым входом первого элемента-И и .первым входом второго элемента И, вы (Л ход которого соединен с управляющим входом регистра запросов, вход так-, товых импульсов устройства соединен с вторым входом второго элемента И и . тактовым входом триггера сиихронизации , вход Конец прерывающей программы устройства соединен с вторым входом запуска с четчика, вторым информационным входом входного коммутатора и третьим входом первого элемента И, отличающееся тем, что, с целью расширения функциональных возможностей за счет динамического управления проц.ссами прерывания путем изменения уровня прерывания обслуживаемой программы, оно содержит стек счетчиков состояний и коммутатор, причем выход входного коммутатора соединён с входом записи стека счетчиков состояний, выход которого соединен с информациол} ым входом выходного коммутатора , выхо постоянного запоминающего блока соединен с информационным вхо

СОЮЗ СОВЕТСКИХ * СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) g i 1) (51)4 С 06 9

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР « »--ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3736731/24-24 (22) 11.03.84 (46) 23.08.85. Бюл. )!« 31 (72) Ю.И.Ялинич, В.IÎ.Ëàð÷åíêî, К.К.Фурманов и M. Ô,.Õoëîäíûé (71) Харьковский ордена Ленина авиационный институт им. Н.Е.)Куковского (53) 681.325(088.8) (56) Авторское свидетельство СССР

II« 811259, кл. С 06 F 9/46, !979.

Авторское свидетельство СССР

II« 1104516,. кл. G 06 F 9/46, 1983. (54) (57) УСТРОЙСТВО МНОГОУРОВНЕВОГО

ПРЕРЫВАНИЯ, содержащее регистр запросов, блок выходных элементов И, триг- . гер запрета прерывания, триггер прерывания, триггер .синхронизации, по-. стоянный запоминающий блок, причем информационные входы регистра запросов являются входами запросов устройства, а выход регистра запросов соединен с входом постоянного запоминающего блока и информационным входом блока выходных элементов И, управ-. ляющий вход которого соединен с Rвходом триггера прерывания.и входом выдачи кода приоритетности устройства, а выход является выходом приоритетности устройства, вход "Прерывающая программа" устройства соединен с синхронизирующим входом триггера запрета прерывания первь|м информа- ционным входом входного коммутатора и первым входом запуска счетчика, выход которого соединен с входом дешнфратора, выход которого соединен с управляющими входами входного и выходного коммутаторов, выход выходного коммутатора соединен с первым входом схемы сравнения, второй вход которой соединен с:выходом постоянного запоминающего блока, вы— ход схемы сравнения соединен с первым входом первого элемента И, выход которого соединен с информационным входом триггера синхронизации, выход которого соединен с

5-входом триггера прерывания, выход .. которого является .выходом прерывания устройства и соединен с входом установки в "1" триггера запрета прерывания.,выход которого соединен с вторым входом первого элемента. И и первым входом второго элемента И, выход которого соединен с управляющим входом регистра запросов, вход так-. товых импульсов устройства соединен с вторым входом второго элемента И и тактовым входом триггера синхрониза-ции, вход "Конец прерывающей программы" устройства соединен с вторым входом запуска счетчика, вторым информационным входом входного коммутатора и третьим входом первого элемента И, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет динамического управления процессами прерывания путем изменения уровня прерывания обслуживаемой программы, оно содержит стек счетчиков состояний и коммутатор, причем выход входного коммутатора соединен с входом записи стека счетчиков состояний, выход которого соединен с информационным входом выходного коммутатора, выхо)(постоянного запоминающего блока соединен с информационным вхо1 7492Ь дом стека счетчиков состояний, вход !

"Продолжение прерывающей программы устройства соединен с четвертым входом первого элемента И и информационным

1Изобретение относится к области цифровой вычислительной техники, а точнее к устройствам обработки прерываний в муль ипрограммных ЦВМ, и предназначено дпя использования, 5 главным образом, в специа изированных вычислительных иуправляющих системах, организованных на основе микропроцессоров.

Целью изобретения является расши- 10 рение функциональных возможностей устройства за счет динамического управления процессом прерывания путем изменения уровня прерывания обслуживаемой программы. 15

Введение в устройство стека счетчиков состояний 1,вместо стека регистров состояний) и коммутатора (для коммутации счетного сигнала) расширяет функциональные возможности уст- 20 ройства, позволяя динамически управлять процессом прерываний путем изменения уровня прерывания обслуживаемой программы, Динамическое управление процессом прерываний позволяет 25 избежать затрат машинного времени на нерациональные прерывания и более эффективно использовать производительность ЦВМ.

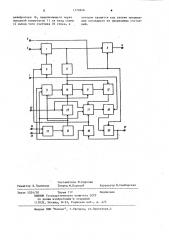

На чертеже приведена структурная 30 схема устройства.

Устройство содержит регистр 1 запросов, вход 2 запросов устройства, блок выходных элементов И 3, выход 4 приоритетности устройства, вход 5 выдачи кода приоритетности устройст35 ва, элемент И 6, вход 7 тактовых импульсов устройства, постоянной запоминающий блок (ПЗУ) 8, входной коммутатор 9, стек счетчиков 10 состояний, выходной коммутатор ll схему 12

40 сравнения счетчик 13, первый управляющий вход 14 устройства, второй управляющий вход 15 устройства, дешифратор 16, элемент И 17, триггер 18 синхронизации, триггер 19 запрета входом коммутатора, управляющий вход которого соединен с выходом дешифратора, выход коммутатора соединен со счетным входом стека счетчиков состояний. ° прерывания, триггер 20 прерывания, выход 21 прерывания устройства, третий управляющий вход 22 устройства, коммутатор 23.

Устройство работает следующим образом.

Исходное состояние устройства характеризуется тем, что регистр 1, . триггеры 18 — 20 и счетчик 13 находятся в нулевом состоянии, состояние счетчиков 10 стека и входа 2 произвольное, на входах 5, 7, 14, 15 и 22 устройства и на его выхо— дах 4 и 21 сигналы отсутствуют (!ьулевые уровни сигналов — на выходах регистра 1, триггера 18, счетчика 13, на входах 5 и 7 и выходах 4 и 21; еди. ничные уровни сигналов — на входах

l4, 15 и 22 и выходе триггера 19, являющемся инверсным выходом).

С приходом тактового импульса на вход 7 устройства он через элемент

И 6 поступает на управляющий вход регистра 1, разрешая прием запросов прерываний в регистр по входу 2. На выходе регистра 1 запросов с шифрато-. ром приоритетов формируется код приоритетности, соответствующий номеру (i = 1, n) активного источника запроса с наивысшим приоритетом (наибольшему из номеров активных источников). При отсутствии запросов на прерывание устанавливастся нулевой код. При отсутствии запросов на прерывание устанавливается нулевой код. Код приоритетности посту пает на вход ПЗУ 8, с выхода которого код уровня прерывания подается на вход схемы 12 сравнения.При нулевом коде прио-ритетности формируется нулевой код уровня прерывания, На другой вход ,схемы 12 сравнения поступает код с выходного коммутатора 11, характеризующий уровень прерывания обрабатываемой программы (основная програм! 174926 ма имеет нулевой код уровня прерывания) .

Если код уровня прерывания, сформированный ПЗУ 8, превосходит по зна. чению уровень прерывания обрабатываемой программы, то на выходе схемы 12 возникает единичный сигнал, которыи через элемент И 17 поступает на вход

D триггера 18.и по переднему фронту очередного тактового импульса 10 на входе синхронизации переводит триггер 18 в единичное состояние, что вызывает установку триггера 20 прерывания и выдачу в ЦП по выходу 21 сигнала прерывания, который по 15 входу S устанавливает триггер 19 запрета прерывания (на выходе триггера 19, являющемся инверсным выходом, возникает нулевой сигнал), запрещая временно (до установки нового поро- 20 га прерывания на входе схемы 12 сравнения) формирование последующих сигналов прерыв ания. Одновременно нулевой сигнал на выходе триггера 19 запирает элемент И 6 и "замораживает" состояние регистра 1, обеспечивая условия для корректного перехода к прерывающей подпрограмме, идентификация которой осуществляется по значению кода приоритетности.

Вместе с тем нулевой сигнал на выходе триггера 19 вызывает появление нуля на входе D триггера 18, что при водит к сбросу триггера 18 передним фронтом очередного тактового импуль35 са на входе синхронизации.

После. обнаружения сигнала прерывания ЦП вырабатывает импульсный сигнал выдачи кода приоритетности, подаваемый на вход 5. При этом код при40 оритетности через блок выходных элементов И 3 поступает по выходу 4 в

IgI и используется для перехода к соответствующей прерывающей поднрограмме, а триггер 20 устанавливается по входу R в нулевое состояние.

Прерывающая подпрограмма обеспечивает сохранение в стеке оперативного ЗУ всей информации, необходимой для последующего возврата к продолжению выполнения прерванной программы, и с помощью команды вывода посылает на вход 14 импульс отрицательной полярности, который запирает входной коммутатор 9, фиксируя код уровня прерывания, поступаю- щий с выхода ПЗУ 8, в соответствующем счетчике 10 стека, номер которо

4 го на единицу больше исходного показания счетчика 13. Вместе с тем по переднему фронту импульса на входе 14, связанном с входом суммирования счет - ка 13, начинается процесс увеличения на единицу показания этого счетчика и соответствующего переключения дешифратора 16, подключающего через выходной коммутатор 11 на вход схемы 12 сравнения выход того счетчика 10 стека, в котором зафиксирован новый код уровня прерывания, По заднему фронту им- пульса на входе 14, связанном с входом синхронизации триггера 19, на вход D которого постоянно подается нулевой сигнал, происходит сброс триггера 19 и на его выходе устанавливается единичный сигнал, разрешаю-. щий работу элементов И 17 и 6.

По мере. приближения к завершению выполняемой подпрограммы возрастает нежелательность прерывания ее выполнения, поэтому в определенных местах подпрограммы помещаются команды вывода, по каждой иэ которых на вход 22 устройстьа подается управляющий импульс отрицательной полярности, обеспечивающий повышение на единицу уровня прерывания подирограм мы. Осуществляется это с помощью ком мутатора 23, передающего (с инверсией) :правляющий импульс на счетный вход того счетчика 10 стека, номер которого соответствует двоичному коду на выходе указателя стека счет— чика 13. Переключение выбранного счет чика 10 стека начинается по переднему фронту импульса на счетном входе.

Чтобы исключить возможность формирования ложного сигнала прерывания под воздействием переходных процессов в счетчике 10 стека, коммутаторе 11 и схеме 12 сравнения производится временное запирание элемента И 17 управляющим импульсом с входа 22.

После завершения выполнения прерывающей подпрограммы восстанавливается последнее из прерванных состояний ЦП и с помощью команды вывода на вход 15 посылается отрицательный импульс, который запирает входной коммутатор 9 и элемент И 17. Вместе с тем по переднему фронту импульса на входе 15, связанном с входом вычитания счетчика 13,. начинается процесс уменВшейия на единицу показания счетчика и соответствующего переключения

1174926

Составитель М. Сорочан

Редактор Л. Гратилло Техред М.,Пароцай

Корректор М. Самборская

Заказ 5201/50 Тираж 710

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Подписное

Филиал ППП "Патент", r.Óæãoðîä, ул.Проектная,4 дешифратора 16, подключающего через выходной коммутатор 11 на вход схемы

12 выход того счетчика 10 стека, в котором хранится код уровня прерывания последнего из прерванных состояний.