Устройство для формирования адресов процессора быстрого преобразования фурье

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ АДРЕСОВ ПРОЦЕССОРА БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ, содержащее первый и второй .реверсивные счетчики , группу элементов И, W (где f« разрядность ) мультиплексоров, регистр , элемент И-НЕ, синхронизатор, первьш и второй выходы которого соединены соответственно с суммирующим и вычитающим входами первого реверсивного счетчика, выходы переноса и заема которого соединены соответственно с суммирующим и вйчитающим входами второго леверсивного счетчика, третий выход синхронизатора соединен с тактовым входом регистра, выходы разрядов которого являются информационными выходами устройства, выходы разрядов второго реверсивного счетчика соединены с соответствуюищми входами элемента И-НЕ и первыми входами соответствующих элементов И группы , вторые входы которых объединены и подключены к четвертому выходу синхронизатора, тактовый вход которого является тактовым входом устройства, а вход запуска синхронизатора соединен с выходом элемента И-НЕ, первый информационный вход -го ( 1 О, N -1) мультиплексора соединен с прямымвыходомj -го разряда первого реверсивного счетчика , второй информационный вход 1-го мультиплексора соединен с инверсным выходом j -го разряда перI вого реверсивного счетчика, выход -го мультиплексора соединен с (Л входом j-го разряда регистра, о тличающееся тем, что, с целью упрощения устройства, оно содержит узел постоянной памяти, входы кода адреса которого соединены с выходами соответствующих элементов И группы, а выход .

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК ((9) (!!) (5()4 G 06 F 15 332

ОПИСАНИЕ ИЗОБРЕТ

К ABTOPCH0MV СВИДЕТЕЛЬСТВУ соответствующих элементов И группы, вторые входы которых объединены и подключены к четвертому выходу синхронизатора, тактовый вход которого является тактовым входом устройства, а вход запуска синхронизатора соединен с выходом элемента И-НЕ, первый информационный вход 1 -ro (j = О, и -1) мультиплексора соединен с прямым выходом 1 -го разряда первого реверсивного счетчика, второй информационный вход i

1-ro мультиплексора соединен с инверсным выходом 1 -ro разряда первого реверсивного счетчика, выход

)-го мультиплексора соединен с входом 1 -го разряда .регистра, о тл и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит узел постоянной памяти, входы кода адреса которого соединены с выходами соответствующих эле1 ментов И группы а выход и, 1 -го (i = 0,1; 1 = О, Н -1) разряда узла постоянной памяти соединен с ) -м ! адресным входом ) -ro мультиплексора, третий информационный вход

1-го мультиплексора соединен с выходом младшего разряда первого реверсивного счетчика, четвертый информационный вход K --го () =0, N -2) мультиплексора соединен с прямым выходом (К+1)-го (К=О, 1(-.2) разряда первого реверсивного счетчика.

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 372979?/24-24 (22) 21.04.84 (46) 23 .08.85. Бюл. № 31

* (72) А.И. Шемаров и А.E. Леусенко (71) Иинский радиотехнический институт (53) 681.32 (088.8) (56) Авторское свидетельство СССР

¹ 548863, кл. G 06 F 15/332, 1976 °

Авторское свидетельство СССР

¹- 999062, кл, G 06 F 15/332, 1983, (54)(57) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ АДРЕСОВ ПРОЦЕССОРА Б61СТРОГО

ПРЕОБРАЗОВАНИЯ ФУРЬЕ, содержащее первый и второй .реверсивные счетчики, группу элементов И, N (где Ц разрядность) мультиплексоров, регистр, элемент И-НЕ, синхронизатор, первый и второй выходы которого соединены соответственно с суммирующим и вычитающим входами первого реверсивного счетчика, выходы переноса и заема которого соединены соответственно с суммирующим и вычитающим входами второго леверсивного счетчика, третий выход синхронизатора соединен с тактовым входом регистра, выходы разрядов которого являются информационными выходами устройства, выходы разрядов второго реверсивного счетчика соединены с соответствующими входами элемента И-НЕ и первыми входами й..„,.r, ЕНИЯ ":::: - " (рiÚ. Ъ, .(.3

«

1174939

2, 21

2 2!

2э 2

Ф

2 21+

2 2 "

2 " 2

Слой

1

2

2j 1

2

2

2 2 22

2 2 22

2 2 2

2М-

2N-f

° ° ° °

2

Й-

2 22 2э

2 2 2>

2э

j -1

+1

° ° ° a

° ° ° °

j+< 1 2

2 2э 2э

Изобретение относится к вычисли тельной технике и может быть использовано в составе процессора быстрого преобразования Фурье (БПФ) или быстрого преобразования в базис иных орто- 5 гональных функций, используемых в спектроанализаторах, генераторах широкополосного случайного процесса, синтезаторах речевых сигналов и т.д.

Цель изобретения - упрощение устройства.

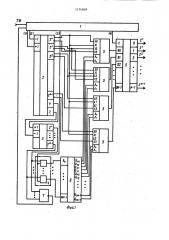

На фиг.1 представлена функциональная схема устройства; на фиг.2— функциональная схема синхронизатора, на фиг.З " временные диаграммы работы синхронизатора на фиг.4— прошивка узла постоянной памяти для произвольной разрядности устройства адресации.

Устройство для формирования адре- 20 сов процессора БПФ (фиг.1) содержит синхронизатор i, первый реверсивный счетчик 2, второй реверсивный счетчик 3, группу (двухвходовых) элементов И 4, N мультиплексоров (данных четыре канала на один) 5, регистр 6, элемент -HE 7 и узел 8 постоянной памяти.

В известном устройстве с помощью мультиплексоров соответствующим образом коммутируются разряды счетчика в зависимости от номера слоя, информация о котором подается на 45 адресные входы всех мультиплексоров одновременно, т.е. параллельно.Однако это требует, чтобы количество каналов мультиплексора было равно количеству слоев алгоритма БПФ,кото- 50 рое зависит от длины обрабатываемого массива. Причем, чем выше длина обрабатываемого массива, тем выше разрешающая способность в частотной области и тем точнее можно получить 55 результаты спектрального анализа.

Если проанализировать разряды счетчика, которые коммутирует кажСинхронизатор (фиг,2) содержит счетчик 9, элемент 4И-4И/ИЛИ 10, элемент 4И-4И-ЗИ/ИЛИ 11, элемент

2И-НЕ 12 .

На временной диаграмме (фиг ° 3) приведены следующие сигналы: ТИ— тактовые импульсы; А1-А4 — разрядные выходы счетчика 91 сигналы 13 на втором входе, 14 на первом выходе, 15 на втором выходе, 16 на третьем выходе и 17 на четвертом выходе синхронизатора 1. °

Принцип работы устройства заключается в следующем.

Известно, что адреса пары операндов алгоритма БПФ отличаются информа. цией в одном разряде, номер которого соответствует номеру слоя алгоритма

БПФ, причем адрес первого операнда содержит логический нуль в данном разряде, а адрес второго операнда— логическую единицу. Если сравнить адреса алгоритма БПФ и коды, вырабатываемые счетчиком, то нетрудно заметить, что в каждом слое алгоритма

БПФ адреса отличаются от кодов счетчика только порядком следования разрядов: дый мультиплексор (данных), то окажется, что каждый мультиплексор (данных) j (j = О, М -1) коммутирует не более трех разрядов счетчика (2,2

2 ).. Следовательно, не обязательно применять многовходовые мультиплексоры (данных), а необходимо и достаточно четырехканальных мультиплексоров (данных). Четвертый вход

I-го (1=0, М -1) мультиплексора (данных) подключается к инверсному разрядному выходу счетчика 21 и применяется при работе в специальном слое алгоритма БПФ. При использовании четырехканальных мультиплексоров (дан-ных) переключать нужно не все каналы одновременно, как в известном устройстве, -а последовательно мультиплек)-1 ) ) +1 М-1

A1AO АI АО AI AO АI АО

00, 00, 00, 00

00, 00, 00, 00

00, 00, 00, 00

Слой

О

01 00, 00, 00

10, 01, .00, 00

10, 10, 01, 00

10, 10, 10, 01

1Q, 10, 10, 10, }-1

1+1

М-1

10, 10, 10, 10, 103 10, 10, 10, код, по которому на выходах мультиплексоров (данных ) появляются инверсные значения двоичного счетчика.

При работе в специальном слое безызбытачный алгоритм БПФ на управляющих входах мультиплексоров (данных ) появляется

2 1+1 И-1

А1АО А I АО А I АО A I AO AI AO

11, I I i 11, 11, 11

О 1

А1АО АI АО

Слой Й 11, 11, Кроме того, с помощью группы злементов И 4 на управляющих входах мультиплексоров (данных)может быть сформирован код путем подачи на вторые входы группы элементов И 4 уровня логического нуля, по которому на вы-, ходах мультиплексоров (данных) появ4О ляются прямые значения кодов счетчика!

3 +1 М1

АIАО А1АО. АIАО AIAO

00 00 00 00

О 1 2

А1АО А1АО АIАО

Слой О 01 00 00 ранд, затем в счетчик добавляется единица и его прямое значение адресует первый операнд. Порядок следования пары специального слоя БПФ может быть произвольным, так как данная .пара обрабатывается по способу, отличающемуся от способа обработки пары операндов основных слоев алгоритмов БПФ, При работе в специальном слое адресуется пара операндов n,g -п(в=

М

= lg" -1)где М - количество разрядов счетчика.

Формирование адресов специального слоя алгоритма осуществляется следующим образом. Инверсное значение первого счетчика адресует второй опе-5s з 1174939 4 сор (данных) за мультиплексором (дан" g — 1 Х2, Х2, Х2, Х2, Х2, Х2, Х1 ных).

Для каждого слоя алгоритма БПФ Мультиплексор (данных четыре канала каналы мультиплексоров (данных) ком- на один) имее дв адр д на о н имеет два адресных входа АI мутируются следующим образом: и AO (АI = О и AO Π— на выход

Слой коммутируется канал ХО, АI = О и

О XI XQ, XO, XO XO, XO, XQ АО = 1 — на выход коммутируется ка1 Х2, ХI, ХО, ХО, ХО, ХО, ХО нал XI, AI = 1 H ÀQ = 0 - на выход г Х2, Х2, Х1, ХО, ХО, ХО, ХО комутируется кана Х2, А1 = 1 и

10 AO = 1 — на выход.коммутируется каХ2 Х2 Х2 Х1 XO XO ХО нал ХЗ). Следовательно, прошивка

Х2 X2, XI, XO, XO,Узла постоянной памяти будет выгляХ2, Х2 Х2 Х2 Х2, XI, XQ- деть следующим образом:

О 1 2

АIАО AIAO AIAO

01, 00, 00, 10, 01, ОО, 10, 10, 01, 1174939, Фиг.7

1174939 иг, Такты, 7,2,3,9,5,6, 7,8,9,70,77 12 Д1,2,5, Ф, 5, 6,7,8,9,10 77,72, 77

1174939

OO O C) O O O O O Ф» щю Фь Ib O Ct ооо ooooñ ooooe » щЮЮ Ю ЮЮЮ

Moo cs Фэo Фр>o oooo) ю» сфц ФВ cs Фф ФФ Ф:э о ф;р сф ф;р 4Ф Ф ф ооа со oo e oo ooo— евое еeo еoo aе»o

o o o с=э o o o o ФФ o o aea o o сэ o o o o сз

o %so o o Фр о йр е оo oooo ъ сз o сь 1ъ с0 ср» Фэ ° сэ В

ooo

ФЭ и »»

Ю»»

Ю Сй> °

° » ос съ сэва ср атее a ohio о сает с» o o a ас> e срln ъ д

Ъ = о к

< ъ : сэ съ >—

С> ЪСЪ Фэ D съ с с ц, сь аое о

o o

° »»»» ь р

o a о о

Сз CO

ЕЗО ю - о с

Ф4

° т с

Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, iK-35, Раушская наб., д. 4/5

Заказ 5202/51

Филиал IIIIII "Патент", г. Ужгород, ул. Проектная,4 Составитель А. Баранов

Редактор В. Петраш Техред А.Ач Корректор Л. Бескид,