Формирователь задержанных импульсов

Иллюстрации

Показать всеРеферат

ФОРМИРОВАТЕЛЬ ЗАДЕРЖАННЫХ ИМПУЛЬСОВ, сбдержащий входную шину двоичный счетчик, счетный вход которого соединен с шиной тактовых импульсов , а выходы - с входами дешифратора , входной RS-триггер, R-вход которого через элемент совпадения соединен с установочным входом двоичного счетчика, а инверсный выход входного RS-триггера подключен к второму входу элемента совпадения, о тличающийся тем, что, с целью расширения функциональных возможностей путем формирования выходньк импульсов длительностью, равной тактовым, и автоматического регулирования времени задержки, в него введены управляющие шины, элемент НЕ, группа элементов ЗАПРЕТ и элемент ИЛИ-НЕ, причем вькод элемента ИПИ-НЕ подключен к R-входу входного RS-триггера , входы элемента ШТИ-НЕ подключен к выходам элементов ЗАПРЕТ, у которых первые входы подключены к управляющим шинам, вторые входы соединены с соответствукн ими выхода (Л ми дешифратора, у которого стробирующий вход Через элемент НЕ подключен с к счетному входу двоичного счетчика, а S-вход входного RS-триггера соединен с входной шиной.

СОЮЗ СОВЕТСНИХ

ОВВЮЛ СМ

РЕСПУБЛИК (19) (11) (51)4 Н ()3 К 5 3

ОПИСАНИЕ ИЗОБРЕТЕНИ "

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

° ь

4LC8 /

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3712611/24-21 (22) 20.03.84 (46) 23.08.85. Бюп. )) 31 (72) В.И. Левинский и В.А. Чистяков (53) 621.374.5(088.8) (56) Авторское свидетельство СССР

В 790217, кл. Н 03 К 5/13, 1978.

Авторское свидетельство СССР

У 924839, кл. Н 03 К 5/13, 1980. (54)(57) ФОРМИРОВАТЕЛЬ ЗАДЕРЖАННЪИ

ИМПУЛЬСОВ, содержащий входную шину; двоичный счетчик, счетный вход которого соединен с шиной тактовых импульсов, а выходы - с входами дешифратора, входной Rs-триггер, R-вход которого через элемент совпадения соединен с установочным входом двоичного счетчика, а инверсный выход входного RS-триггера подключен к второму входу элемента совпадения, о тл и ч а ю шийся тем, что, с целью расширения функциональных возможностей путем формирования выходных импульсов длительностью, равной так- . товым, и автоматического регулирования времени задержки, в него введены управляющие шины, элемент НЕ; группа элементов ЗАПРЕТ и элемент

ИЛИ-НЕ, причем выход элемента ИЛИ-НЕ подключен к R-входу входного КЯ вЂ триггера, входы элемента ИЛИ-НЕ подключен к выходам элементов ЗАПРЕТ, у которых первые входы подключены к управляющим шинам, вторые входы соединены с соответствующими выходами дешифратора, у которого стробиру ощий вход через элемент НЕ подключен к счетному входу двоичного счетчика, а S-вход входного RS-триггера соединен с входной шиной.

1 11750

Изобретение относится к импульсной технике и может быть использовано в различных устройствах вычислительной техники в качестве"управляемого устройства задержки импульсов.

Цель изобретения - расширение функциональньм воэможностей путем формирования выходных импульсов, длительностью, равной тактовым, и автоматического регулирования времени l0 задержки.

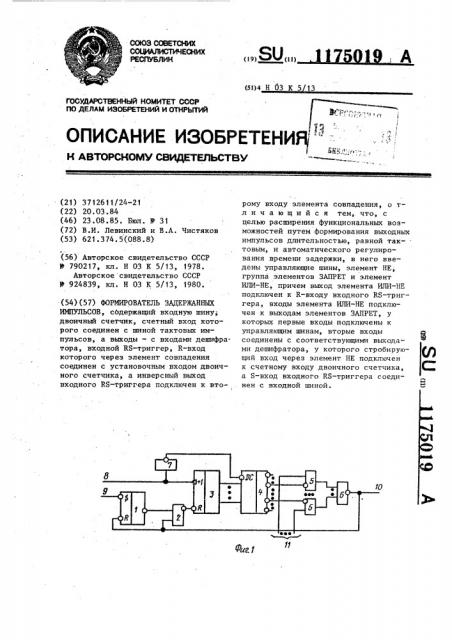

На фиг. 1 представлена функциональная схема устройства; на фиг. 2— временные диаграммы работы устройства. 15

Формирователь задержанных импульсов содержит входной RS-триггер 1, элемент. 2 совпадения, двоичный счетчик 3, дешифратор 4, группу элементов ЗАПРЕТ 5, элемент ИЛИ-НЕ 6, 20 элемент НЕ 7, входные шины 8 и 9, выходную шину 10.и управляющие шины 11.

При этом входная шина 8 соединена с счетным входом двоичного 25 счетчика 3 и через элемент НЕ 7

° подключена к стробирующему входу дешифратора 4, у которого соответствующие вьмоды подключены к вторым входам элементов ЗАПРЕТ 5, 30 первые входы которых соединены с управляющими шинами 11. Выходы элементов ЗАПРЕТ 5 подключены к входам элемента ИЛИ-НЕ 6, выход которого подключен к R-входу входного RS-триг35 гера 1, к выходной шине 10 и через элемент 2 совпадения к установочному входу двоичного счетчика 3.

S-вход RS-триггера 1 подключен к входной шине 9, а инверсный его выход †:к второму входу элемента 2 совпадения. Выходы двоичного счетчика 3 подключены к входам дешифратора 4.

Устройство работает следующим 45 образом.

В исходном состоянии на управляющих шинах 11 нулевые уровни, н входной шине 8 присутствуют импульсы тактовой частоты. На выходе 50 элемента НЕ 7 — импульсы, инверсные тактовым. На входной шине 9 входные импульсы отсутствуют. Нулевой уровень инверсного выхода элемента 2 совпадения удерживает 55 по установочному входу двоичный счетчик 3 в нулевом состоянии. На одном выходе дешифратора 4, дешифрирую19 2 щем нулевое состояние двоичного счетчика 3, периодически появляются импульсы нулевого уровня, совпадающие по времени действия с тактовыми. На выходах группы элементов

ЗАПРЕТ 5 - нулевые уровни, а на выходах остальных элементов — единичные. Перед началом работы на одной из управляющих шин 11 устанавливается единичный уровень, а на остальных — нулевые уровни. Предположим, что необходимо сформировать задержанный импульс на шесть тактов.

С приходом входного синхронного (асинхронного) сигнала по шине 9 срабатывает входной триггер 1, в результате чего на инверсном выходе элемента 2 совпадения появляется единичный уровень, который разрешает двоичному счетчику 3 производить пересчет импульсов тактовой частоты, поступающих по шине 8.

Двоичный счетчик 3 просчитывает по заднему фронту импульсы. При этом каждое состояние двоичного счетчика 3 дешифрируется дешифратором .4 и на соответствующем выходе дешифратора 4 появляется сигнал нулевого уровня во время действия следующего очередного тактового импульса на шине 8. Нулевой уровень соответствующего вьмода дешифратора 4 пропускается тем элементом ЗАПРЕТ 5, на первом входе которого установлен единичный уровень. В данном случае будет пропускаться нулевой сигнал шестого выхода дешифратора

4, который соответствует пятому состоянию двоичного счетчика 3. Единичный сигнал, появившийся на соответствующем выходе элемента ЗАПРЕТ 5, проходит нулевым сигналом через элемент ИЛИ-НЕ 6 на выходную шину 101 одновременно поступает на вход элемента 2 совпадения, блокируя на время выдачи выходного сигнала R-вход входного RS-триггера 1,. устанавливая

его в нулевое состояние. При этом на инверсном выходе выходного триггера

1 появляется единичный уровень, который ожидает окончания выходного сигнала. По окончании выходного сигнала на выходной шине 10 появляется единичный уровень, который проходит через элемент 2 совпадения нулевым уровнем, устанавливая по установочному входу двоичный счетчик 3, и удерживает его в этом сосI t I I I I

t I

Составитель Е. Суров

Редактор Е. Лушникова Техред А.Бабинец Корректор А, Зимокосов

Заказ 5211/55 Тиражi 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 тоянии до прихода очередного входного сигнала.

По начальному состоянию двоичного счетчика 3 формирователь устанавливается в исходное состояние.

Следующий входной сигнал повторяет процесс формирования задержанного синхронного импульса.

Следовательно время появления выходного импульса определяется подсоединением соответствующего выхода дешифратора 4 к второму входу соответствующего элемента ЗАПРЕТ 5

1175019 4 при подаче на первый его вход управляющего единичного уровня. Поэтому, подавая по очереди управляющие единичные уровни на соответствующие элементы ЗАПРЕТ 5, можно регулировать задержку выходных импульсов, оставляя при этом длительность выходных импульсов, равной длительности тактового импульса. Изменяя

1О количество элементов ЗАПРЕТ 5 можно регулировать число различных задерживаемых импульсов, которое не может превьппать число выходов дешифрато- . ра 4.