Преобразователь кода системы остаточных классов в напряжение

Иллюстрации

Показать всеРеферат

1. ПРЕОБРАЗОВАТЕЛЬ КОДА СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ в НАПРЯЖЕНИЕ , содержащий п регистров, по числу оснований системы остаточных классов, входы которых являются входными шинами преобразователя, выходы ( л -1) регистров подключены к соотвествующим первым входам (п.-1) блоков сравнения, прямые выходы которых подключены к входам блока сборки сигналов сравнения, первый выход которого подключен к управляющему входу блока вьодачи напряжения, выход которого является выходной шиной преобразователя, вход подключен к выходу блока суммирования напряжений, первый вход которого подключен к выходу первого цифро-аналогового преобразователя , отличающийс я тем, что, с целью повьш1ения быстродействия, в него введены (а -1) сумматоров по модулям оснований системы остаточных классов, кроме наименьшего, первый и второй преобразователи кода, (-1) элементов И, (п-1) счетчиков, (и.-1) цифро-аналоговых преобразователей, блок ключей, блок управления, первый вход которого объединен с управляющем входом блока ключей и является шиной начала преобразования, второй вход подключен к первому выходу блока сборки сигналов сравнения, группа вторых выходов которого и инверсный выход первого блока сравнения подключены к соответствующим первым входам первого преобразователя кодов , вторые входы которого подключены к соответствующим прямым выходам блоков сравнения, третий вход подключен к первому выходу блока управления, а выходы - к соответствующим первым входам второго преобразователя кодов и первым входам соответствую1хих (т--) элементов И, . .вторые входы которых объединены с управляющими входами сумматоров по модулям и подключены к второму выходу блока управления, выходы подключены к входам (п.-1) счетчиков, выходы которых подключены к соответству ющим входам соответствующих (п-1) цифрраналоговых преобразователей, выходы которых подключены к соответствующим (п-1) входам блока суммирования напряжений, при этом высд ходы первого регистра подключены к соответствующим входам первого цифро аналогового преобразователя и к соответствующим входам блока ключей, выходы которого подключены к соответст вующим вторым входам второго преобразователя кода,выходыкоторого подключены к соответствующим информационным входам сумматоров по модулям,выходыкоторых подключены к соответствующим вторым входам соответствующих блоков сравнения. 2. Преобразователь по п. 1, отличающийся тем, что блок

СООЗ СОВЕТСХИ)(СОЦ)ИАЛИСТИЧЕСХИХ

РЕСОУБЛИХ (!9) (! 3) (51)4 Н 03 М 1/66

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ ХОМИТЕТ СССР

00 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТХРЫТИЙ (21) 3597515/24-24 (22) 27,05,83 (46) 23.08.85. Бюл. № 31 (72) Н.А.Вершков, С.Н.Хлевной, Н.И.Червяков и Н.И.Швецов (53) 681.325(088.8) (56) Авторское свидетельство СССР

¹ 991407, кл. G 06 F 3/04, 1981 °

Авторское свидетельство СССР

N- 282767, кл,,Н 03 К 13/03, 1969. (54)(57) 1. ПРЕОБРАЗОВАТЕЛЬ КОДА

СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В НАПРЯЖЕНИЕ, содержащий n. р еeг иHс тTр оo в, по числу оснований системы остаточных классов, входы которых являются входными шинами преобразователя, выходы (< -1) регистров подключены к соотвествующим первым входам (-1) блоков сравнения, прямые выходы которых подключены к входам блока сборки сигналов сравнения, первый выход которого подключен к управляющему входу блока выдачи напряжения, выход которого является выходной шиной преобразователя, вход подключен к выходу блока суммирования напряжений, первый вход которого подключен к выходу первого цифро-аналогового преобразователя, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия, в него введены (rl. -1) сумматоров по модулям оснований системы остаточных классов, кроме наименьшего, первый и второй преобразователи кода, (<-I) элементов И, (n. — 1) счетчиков, (n.-1) цифро-аналоговых преобразователей, блок ключей, блок управления, первый вход которого объединен с управляющим входом блока ключей и является шиной начала преобразования, второй вход подключен к первому выходу блока сборки сигналов сравнения, группа вторых выходов которого и инверсный выход первого блока сравнения подключены к соответствующим первым входам первого преобразователя кодов, вторые входы которого подключены к соответствующим прямым выходам блоков сравнения, третий вход подключен к первому выходу блока управления, а выходы — к соответствующим первым входам второго преобразователя кодов и первым входам соЮ ответствующих (-1) элементов И, ..вторые входы которых объединены с управляющими входами сумматоров по модулям и подключены к второму выходу блока управления, выходы подключены к входам (и-1) счетчиков, выходы которых подключены к соответству ющим входам соответствующих (n -1) цифроаналоговых преобразователей, выходы которых подключены к соответствующим (n-1) входам блока суммирования напряжений, при этом выходы первого регистра подключены к соответствующим входам первого цифроаналогового преобразователя и к соответствующим входам блока ключей, вы- 4 ходы которого подключены к соответст вующим вторымвходам второгопреобразо- ф, вателя кода, выходыкоторого подключены к соответствующиминформационным входам сумматоров по модулям,выходыкоторых подключенык соответствующимвторым входам соответствующих блоков сравнения.

2. Преобразователь по п. 1, о тл и ч а ю шийся тем, что блок

1175034 управления выполнен на генераторе тактовых импульсов, элементе И,RSтриггере, элементе задержки, вход которого является первым входом блока управления, выход подключен к S-входу RS-триггера,R-вход которого является вторым входом блока управления, выход является первым выходом блока управления и подключен к первому входу элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, а выход является вторым выходом блока управления.

Изобретение относится к вычислительной технике и может быть использовано для сопряжения вычислительных устройств, функционирующих в системе остаточных классов (СОК) с различными оконечными устройствами, требующими аналогового вывода, а также в технике связи при использовании ,кодов СОК в цифровой телефонии.

Цель изобретения — повышение быст10 родействия преобразования.

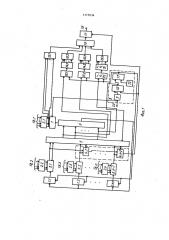

На фиг.l приведена структурная схема преобразователя кода СОК в напряжение; на фиг. 2 — пример реализации первого и второго преобра- l5 зователей кода для основания СОК 2, 3

5, 7.

Преобразователь кода СОК в напряжение содержит сумматоры 1. 1 — 1„

20 по модулям СОК кроме наименьшего, регистры 2.1 — 2.п, блоки 3.1

З,п-1 сравнения, блок сборки сигналов сравнения, который выполнен на

„25 элементах И 4.1 — 4п-2первый и второй преобразователи 5 и 6 кодов, блок 7 ключей, блок 8 управления, который выполнен на элементе 9 задержки, RS — триггере 10, элементе И 11, генераторе 12 тактовых импульсов, эле- З0 менты И l3.1 — 13.n-l, счетчики

14. 1 — 14 н 1, цифра-аналоговые преобразователи (ЦАП) 15.1 — 15n, блок

16 суммирования напряжений, блок

17 йыдачи напряжения, входные шины 35

3. Преобразователь по и. 1, о тл и ч а ю шийся тем, что блок сборки сигналов сравнения выполнен на (й- 2) элементах И, первые входы которых и второй вход первого элемента И являются входами блока сборки сигналов сравнения, каждый прямой выход (n- 3) элементов И, начиная с первого, подключен к второму входу последующего элемента И, прямой выход (h- 2) элемента И является первым выходом блока сборки сигналов сравнения, а инверсные выходы элементов И являются вторыми выходами блока сборки сигналов сравнения.

18.1 — 18п, выходную шину 19, шину

20 начала преобразования.

Первый и второй преобразователи

5 и 6 кодов могут быть выполнены, например, как показано на фиг, 2, для СОК с основанием 2, 3, 5, 7 на элементах И 21. 1 - 21.3 и элементах

ИЛИ 22.1 — ?2.5 соответственно.

Преобразователь работает по следующему принципу.

Число А, представленное в СОК по основаниям Р, P ..., Рпостатками, А1, ..., п в обобщенной позиционной системе (ОПС), записывается следующим образом: а+аР„+ аЗП1р+ + а„р, Г,, Рп-1.

Нахождение коэффициентов а, и с их помощью напряжения БХ=A.Ä, является конечной задачей преобразования °

Очевидно, что

А 1= /А/, =а1, А, = /А/ „= /а +а p / p (и = /а+ а2 р+ az р,р ° ..+а р р

2 т в

Рп-a / Pn

Другими словами для отыскания коэффициента а необходимо к а прибавлять величину р> до тех пор

У пока А . = /а +jр+ р не станет равным, < и, следовательно, j=a . Аналогично ,(з = /a,+ а р,+ j р, р /р при

3- - =3, У-1175

Таким образом можно найти все коэффициенты а, а затем, умножив на соответствующие веса, найти значение А. Для умножения в аналоговом виде можно использовать цифро-аналоговые преобразователи, у которых шаг квантования равен соответственно

"° 41 р ° д, Р

Тогда " I0

Б = а, 1 d« p, и аЗР„Рг ь+ ° ° °

+ a n Р» Рг ° ° ° Рд, 6 = A Ь | т.е. задача преобразования решена.

Преобразователь кода СОК в напряжение работает..следующим образом.

В исходном состоянии все сумматоры 15

1.1 -1;п-1 по модулям, счетчики

14.1 — 14, блок 16 и RS — триггер

10 обнулены. По входным шинам 18 подаются остатки Ф„ с(, ... Ж и записываются в регистры 2.1 -2.п. ЦАП 15,1 20 имеет шаг квантования 14.

По шине 20 подается короткий импульс, который открывает блок 7 ключей.и код К, пройдя второй преобразователь 6 кода записывается в сумма-25

J торы 1.2-1.п по модулям. Элемент 9 задержкц выполнен таким образом, что длительность задержки сигнала в нем больше длительности запускающего импульса. Таким образом, RS — триггер ÇO

10 перейдет в единичное состояние после того, как блок 7 ключей закроется. Единичный потенциал с прямого выхода RS — триггера 10 подается на второй вход элемента И 21.1, на первый вход которого подается,единичный потенциал с инверсного выхода блока 3.1 сравнения. Под действием сигнала с элемента 21.1 во втором . преобразователе 6 кода формируется 4р код величины Р1.. Одновременно единичный потенциал с элемента И 21.1 подается на первый вход элемента И

13.1 и тем самым " разрешает " прохождение тактовых импульсов с бло- 5 ка 8 управления; Под действием каящо-. го тактового импульса во все сумматоры 1.1 — 1 ь-! прибавляется ве034 4 личина Р, а счетчик 14.1 одновременно увеличивает свое состояние на 1. В тот момент, когда К станет равным т.е. выполнится равенство г1, /М, + 3p»/p,= =Ф a = j и В счетчике

14» будет находится величина а>, которая, пройдя процесс цифро-аналогового преобразователя в - ЦАПе 15.2, имеющем шаг квантования р„ А, запишется в блок 16 в виде величины а р Ь и сложится с а16 При совпа2 1 дении кодов К и содержимого сумматора 1 по модулю на прямом выходе блока 3.1 появится единичный потенциал, а на инверсном-нулевой. В результате этого с выхода элемента И

21.1 единичный потенциал изчезнет, а появится на выходе элемента И 21.2, на один вход которого подается единичный потенциал с прямого выхода блока 3.1, а на другой — единичный потенциал с инверсного выхода элемента И 4.1,. так как с блока 3.2 снимается нулевой потенциал. Прохождения импульсов разрешается теперь на счетчик 14.2, а сумматоры 1,g1,n-isa каждый такт добавляется величина P P код которой сформирован

У г Ф теперь на выходе второго преобразователя 6 кода. Когда Ф станет равным

13 вновь произойдет переключение выхода следующего элемента И первого преобразователя 5 кода, а в блок 16 прибавится величина а р, р д. г

Далее процесс будет продолжаться до тех пор, пока на выходе элемента

И 4.,п-2 не появится единичный потенциал. К этому времени в блоке 16 будет находится величина а,+а p+ ."+a 1p р

2 1 т) 1 р,„, ) = Ад

Единичный потенциал на выходе элемента И 4,q- 2 переведет RS — триггер 10 в нулевое состояние, что запретит вьдачу тактовых импульсов с блока 8 управления и откроет блок 17 вьдачи напряжения, Результат преобразования будет считан по шине 19.

1175034

i 175034

Составитель В.Першиков

Редактор Е.ЛушниковаТехред А.БабинецКорректор Л.Бескид

Заказ 5211/55 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4!5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4