Блок питания для доменной памяти

Иллюстрации

Показать всеРеферат

БЛОК ПИТАНИЯ ДЛЯ ДОМЕННОЙ ПАМЯТИ, содержащий два стабнлизированных источника постоянного тока и источник эталонного напряжения , отличающийся тем, что, с целью повьлпения надежности блока питания, он содержит элемент сравнения, два элемента задержки. элемент И, элемент НЕ и ключевой элемент, входы элемента сравнения подключены соответственно к выходу первого стабилизированного источника постоянного тока, который является первым вькодом блока питания, и к выходу источника эталонного напряжения , выход элемента сравнения подключен к входам элементов задержки и первому входу элемента И, выход первого элемента задержки через элемент НЕ подключен к управляющему входу ключевого элемента, подключенного к выходу второго стабилпзи i рованного источн1жа постоянного тока , который является вторым выходом СЛ блока питания, и шине нулевого потенциала , выход второго элемента задержки подключен к второму входу элемента И, выход которого является управлянщим выходом блока питания.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (k I) (5! ) 4 С 1 1 С 1 1/1 4 /

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ПАТЕНТУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО. ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 2968562 /24-24 (22) 18. 07. 80 (31) 091998/79 (32} 19.07.79 (33) JP (46) 23.08.85. Бюл. ¹ 31 (72) P. Имазеки и М. Хаттори (JP} (71) Фудзицу Фанук Лимитед (JP) (53) 681.327.66(088..8) (56) Патент США № 4017604, кл. 340-174, опублик. 1977.

Патент ClllA № 4027300,кл;340-174, опублик. 1977. (54) (57) БЛОК ПИТАНИЯ ДЛЯ ДОМЕННОЙ

ПАМЯТИ, содержащий два стабилизированных источника постоянного тока и источник эталонного напряжения, о т л и ч à ю шийся тем, что, с целью повышения надежности блока питания, он содержит элемент сравнения, два элемента задержки, элемент И., элемент НЕ и ключевой элемент, входы элемента сравнения подключены соответственно к выходу первого стабилизированного источника постоянного тока, который является первым выходом блока питания, и к выходу источника эталонного напряжения, выход элемента сравнения подключен к входам элементов задержки и первому входу элемента И, выход первого элемента задержки через элемент HE подключен к управляющему входу ключевого элемента, подключенного к выходу второго стабилизи— рованного источника постоянного тока, который является вторым выходом блока питания, и шине нулевого потен циала, выход второго элемента задержки подключен к второму входу элемента И, выход которого является управляинцим выходом блока питания.

1175367

Изобретение относится к вычислительной технике и может быть использовано при разработке запоминающих устройств на цилиндрических магнитных доменах (ЦМД). S

Цель изобретения — повышениенадежности блока питания для доменной памяти.

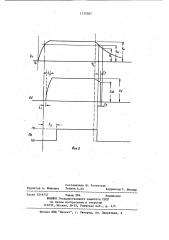

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2 - 10 временная диаграмма возрастания и убывания выходных сигналов.

Блок питания для доменной памяти содержит два стабилизированных источника 1 и 2 питания постоянного тока и источник 3 эталонного напряжения, элемент 4 сравнения, входы которого подключены к источникам 1 и 3, а выход через первый элемент 5 задержки подключен к входу элемента 20

НЕ 6 и входу 7 разрешения включения пи-тания источника 2,а такжечерез второй элемент 8 задержки к одному входу элемента И 9. Выход элемента НЕ 6 подключен куправляющему входуключевого 25 элемента 10, выполненного на тиристоре. Входы стабилизированных источников 1 — 3 через выключатель 11 подключены к первичному источнику 12 питания. 30

Блок питания для доменной. памяти формирует на своих выходах три выходных сигнала: сигнал разрешения обращения к памяти Ме, который подается в блок управления доменнойпамятью,первый сигнал напряжения постоянного тока Е, поступающий в доменную микросборку и блок управления доменной памятью, и второй сигнал напряжения постоянного тока Е 1,поступающий накатуш- 40 ки возбуждения вращающегося магнитного поля. Для обеспечения надежной работы доменной памяти при аварийном отключенчи первичного источника питания указанные выходные сигналы должны возрастать (при вкпючении первичного источника питания) и убывать (при его отключении) в определенных последовательностях (фиг. 2) .

Предлагаемый блок питания работает следующим образом.

При включении выключателя 11 напря" жение переменного тока подается на входы источников 1 — 3. На выходе источника 1 формируется сигнал Ес.

Поскольку сигнал на разрешающем входе

7 источника 2 равен нулю, выходной сигнал Е 1 в этот момент времени отсутствует. После того, как выходной сигнал Ес станет больше эталонного напряжения Ч, сигнал на выходе элемента 4 сравнения принимает значение логической "1", и через некоторое время t<, определяемое элементом 5 задержки, подается на разрешающий вход 7 источника 2 и через элемент

НЕ 6 на управляющий вход тиристора

10, запирая его. Напряжение ЕС1 на выходе источника 2 возрастает за некоторое время t до своего номинального значения Ч . Наконец, на выходе элемента И 9 сигнал принимает значение логической "1" в течение интервала времени t определяемого элементом

8 задержки. Таким образом, осуществля" ется формирование выходных сигналов

Е, Е 1 и Me в требуемой последовательности.

При аварийном отключении первичного источника 12 питания сигналы Ес и Е начинают постепенно уменьшаться.

Как только сигнал Е станет меньше эталонного напряжения Ч, элемент И 9 закрывается и сигнал Ме принимает зна1чение логического "0". Далее через ин1тервал времени t отключается сигнал на разрешающем входе 7 источника 2 и включается тиристор 10, после чего сигнал Е быстро убывает до нуля.

Выходной сигнал Е продолжает постепенно уменьшаться и через некоторый интервал времени t<(t О) становит- ся равным нижнему допустимому значению Ч .

Таким образом обеспечивается правильная последовательность отключения выходных сигналов.

1175367

Составитель Ю. Розенталь

Редактор А. Шишкина Техред А.Ач Корректор С. Шекмар

Заказ 5218/57 Тираж 584 Подписное

ВНИИПИ Государственного комитета CCCP по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4